UNIVERSITY OF GOTHENBURG

# Feasibility Study of Implementing "Reconfigurable Computing" in AUTOSAR Environment

Master's thesis in Embedded Electronic System Design

VINODH RAJKUMAR GANESAN

Department of computer science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2016 The Author grants to Chalmers University of Technology and University of Gothenburg, the non-exclusive right to publish the Work electronically and in a noncommercial purpose, make it accessible on the Internet. The Author warrants that he/she is the author to the Work, and warrants that the Work does not contain text, pictures or other material that violates copyright law. The Author shall, when transferring the rights of the Work to a third party (for example a publisher or a company), acknowledge the third party about this agreement. If the Author has signed a copyright agreement with a third party regarding the Work, the Author warrants hereby that he/she has obtained any necessary permission from this third party to let Chalmers University of Technology and University of Gothenburg store the Work electronically and make it accessible on the Internet.

Feasibility Study of Implementing Reconfigurable Computing in AUTOSAR Environment

© VINODH RAJKUMAR GANESAN, 2016.

Examiner: PER LARSSON-EDEFORS

Department of Computer Science and Engineering Chalmers University of Technology University of Gothenburg SE-412 96 Gothenburg Telephone +46 31 772 1000

# Abstract

Technological advancements have always been a driving factor for growth in many domains. Competitive market and changing customer needs are a common scenario in the automotive sector. Many advancements in the recent past like the drive by wire system or the anti-lock braking system have become reality due to electronic control systems. With the increase in number of electronic control units within a vehicle, the standardization of vehicle's electrical architecture has gained significance. A standard that has been gaining recognition in the automotive sector over the years and that looks to be the future way ahead is the Automotive Open System Architecture (AUTOSAR).

We can expect future vehicles to have more electronics inside them and the electronic control units to be developed based on AUTOSAR standards. Advancements in communication technology have made it feasible to have data exchange between vehicles and by doing so, they have also increased the concerns on safety and security in vehicles. Further, development of various modern concepts like autonomous driving, etc., has pushed the automotive industry to gather lot of data and look for faster processing solutions. General purpose processors, which were previously used, alone are not competent enough to support the processing demands of these embedded applications and thus, wherever possible, hardware acceleration is being tried to aid the processor. But in doing so, the power usage and silicon area of the circuits increase, which is not viable. One way to solve this problem could be to introduce reconfigurable computing. Reconfigurable Computing is a form of computing in which the hardware configurations are modified during program execution. With this technique, the system becomes more flexible for the designers and by smartly selecting the hardware to be reconfigured, high throughput, less power usage and other system specific requirements can be attained. Another advantage could be after sale bug fixes like those which are possible on software today can also be extended to hardware.

Thus, if reconfigurable computing can be implemented within AUTOSAR, it will showcase the possibility to use this technology in vehicles. To understand the feasibility, a system that can dynamically and partially reconfigure an Advanced Encryption Standard (AES) encryption and decryption module in hardware according to diagnostic requests from the user was implemented using *Arctic Core* (an open source AUTOSAR software) for a Zynq® System On Chip (SOC). Results show the possibility of implementing such a system with few limitations. Further it could also be seen that a partially reconfigurable design would be more preferable than a fully reconfigurable solution as it could minimize the down time during reconfiguration of the system.

Keywords: AUTOSAR, Complex Device Driver, Reconfigurable Computing

# Acknowledgements

I would foremost thank Mr. Johan Ekberg from Arccore AB for showing interest in the thesis idea without whom this work would not have been possible. I would like to express my sincere gratitude to Mr. Michael Lundell, my supervisor at Arccore AB and Mr. Mårtan Hilden for their guidance throughout this project. I am thankful to all the Arccore AB staffs for giving me a friendly environment and insights into various topics related to the thesis work, especially to Mr. Tomas Selldén and Mr. Staffan Johansson for sharing their expertise on the hardware.

My special thanks to professor Per Larsson-Edefors and my supervisor Mr. Sven Knutsson for their continuous support and patient reviews.

Vinodh Rajkumar Ganesan, Gothenburg, August 2016

# Contents

| List of Figures vi |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A                  | ronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 1                  | Introduction         1.1       Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1<br>1<br>2<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| <b>2</b>           | Theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                    | 2.1       Open Systems Interconnection         2.2       Automotive Open System Architecture         2.2.1       AUTOSAR Methodology         2.2.2       AUTOSAR Software Architecture         2.2.2.1       Application layer         2.2.2.2       Basic Software         2.2.2.3       Runtime Environment         2.3       Diagnostics         2.4       Controller Area Network         2.5       AES         2.6       Reconfigurable Computing         2.7       Zynq®         2.7.1       Processing System         2.7.2       Programmable Logic | $     \begin{array}{r}       3 \\       4 \\       5 \\       6 \\       6 \\       7 \\       7 \\       7 \\       8 \\       8 \\       9 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\      10 \\      10 \\  $ |  |  |

| 3                  | Methods         3.1       Software and Hardware Selection         3.1.1       AUTOSAR Software         3.1.2       Hardware         3.2       Intended System                                                                                                                                                                                                                                                                                                                                                                                               | <b>11</b><br>11<br>11<br>11<br>12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 4                  | Software         4.1       Development method         4.1.1       Design Strategy         4.1.1.1       Simple Example         4.1.1.2       Configuring Arctic Core for diagnostic requests                                                                                                                                                                                                                                                                                                                                                                | <b>15</b><br>15<br>15<br>16<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|          |       |         | 4.1.1.3   | Choice of a Complex Device Driver                                                               | . 16 |

|----------|-------|---------|-----------|-------------------------------------------------------------------------------------------------|------|

|          | 4.2   | Design  |           |                                                                                                 |      |

|          |       | 4.2.1   |           | n of CDD                                                                                        |      |

|          |       | 4.2.2   | Control   | of reconfiguration                                                                              | . 19 |

|          | 4.3   | Tools V | Used      |                                                                                                 | . 19 |

|          |       | 4.3.1   | Arctic S  | tudio $\ldots$ | . 19 |

|          |       | 4.3.2   | winIDEA   | Α                                                                                               | . 20 |

|          | 4.4   | Implen  | nentation |                                                                                                 | . 21 |

|          |       | 4.4.1   | Hello We  | orld                                                                                            | . 21 |

|          |       | 4.4.2   | Diagnost  | tic Control Module                                                                              | . 21 |

|          |       | 4.4.3   | Complex   | K Device Driver                                                                                 | . 23 |

|          |       |         | 4.4.3.1   | Software Component Description                                                                  | . 23 |

|          |       |         | 4.4.3.2   | Instantiate the newly added Software Component                                                  |      |

|          |       |         |           | (SWC) and generating RTE                                                                        | . 24 |

|          |       |         | 4.4.3.3   | Algorithm within CDD                                                                            |      |

|          |       |         | 4.4.3.4   | Partial Reconfiguration                                                                         | . 25 |

| <b>5</b> | Har   | dware   |           |                                                                                                 | 27   |

|          | 5.1   | Design  |           |                                                                                                 | . 27 |

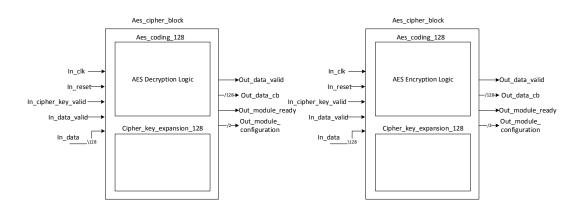

|          | 5.2   |         |           | Decryption                                                                                      |      |

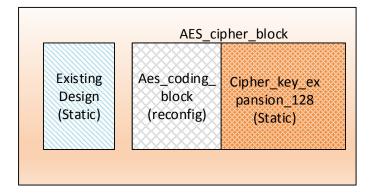

|          | 5.3   | • =     |           | n present design                                                                                |      |

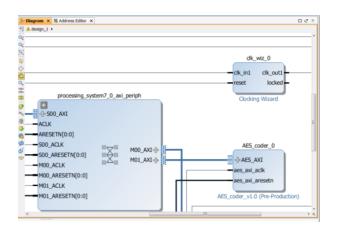

|          | 5.4   | -       | -         | tial Reconfiguration bitstreams                                                                 |      |

| 6        | Boo   | ting    |           |                                                                                                 | 37   |

|          | 6.1   | Zynq®   | Boot Pro  | DCess                                                                                           | . 37 |

|          | 6.2   | · -     |           |                                                                                                 |      |

|          |       |         |           | DK                                                                                              |      |

|          | 6.3   |         |           |                                                                                                 |      |

| 7        | Test  | -       |           |                                                                                                 | 41   |

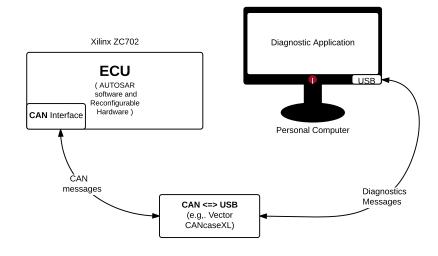

|          | 7.1   | Test Se | etup      |                                                                                                 | . 41 |

|          | 7.2   |         |           |                                                                                                 |      |

| 8        | Disc  | cussion | and Co    | onclusion                                                                                       | 43   |

|          | 8.1   | Discus  | sion      |                                                                                                 | . 43 |

|          | 8.2   | Conclu  | sion      |                                                                                                 | . 44 |

| Bi       | bliog | raphy   |           |                                                                                                 | 45   |

# List of Figures

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>  | The OSI model                                                                                                        | 3     5     6     8     9                             |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 3.1                                                                          | Intended Design Flow                                                                                                 | 13                                                    |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \end{array}$ | Possible locations for CDD                                                                                           | 18<br>19<br>20<br>22<br>23<br>24<br>26                |

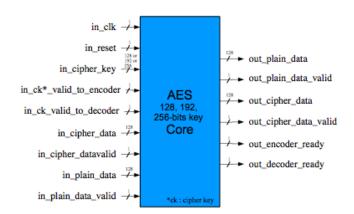

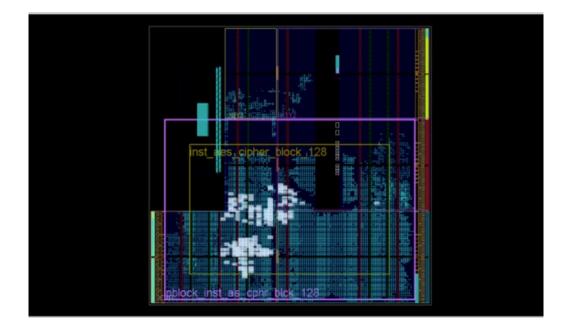

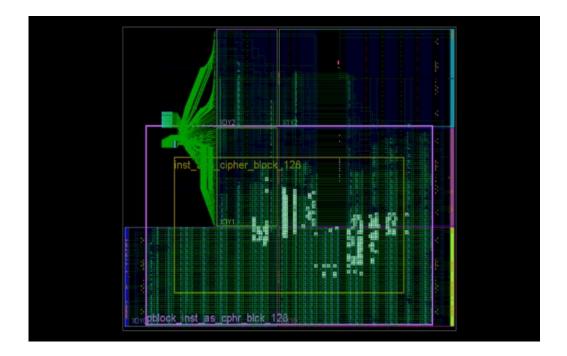

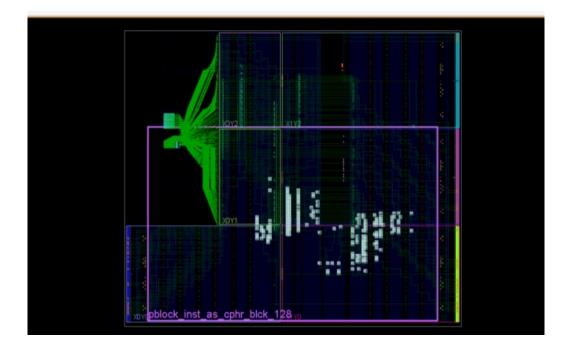

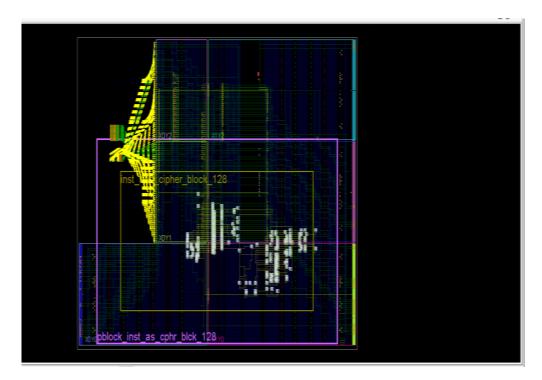

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\$             | AES core                                                                                                             | 27<br>28 28<br>29<br>29<br>31<br>32<br>33<br>34<br>34 |

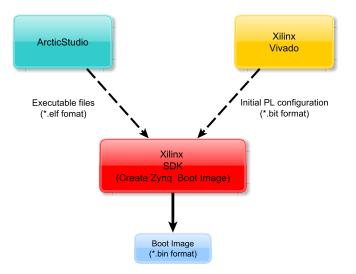

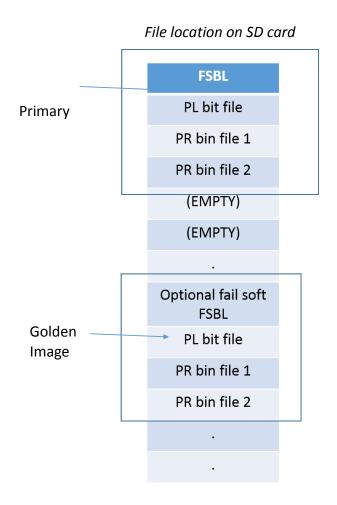

| $     \begin{array}{l}       6.1 \\       6.2 \\       6.3     \end{array} $ | Boot image creationBoot image structureReference location of PR bit files as seen in Xilinx "Create Boot Image" tool | 38<br>39<br>40                                        |

| $7.1 \\ 7.2$                                                                 | Test Setup                                                                                                           | 41<br>42                                              |

# List of Acronyms

| AES                      | Advanced Encryption Standard                   |

|--------------------------|------------------------------------------------|

| API                      | Application Program Interfaces                 |

| $\mathbf{APU}$           | Application Processor Unit                     |

| $\mathbf{ARM}$           | Advanced RISC Machine                          |

| AUTOSAR                  | Automotive Open System Architecture            |

| Artop                    | AUTOSAR Tool Platform                          |

| $\mathbf{AR}\mathbf{ML}$ | AUTOSAR XML                                    |

| ASIC                     | Application Specific Integrated Circuit        |

| AXI                      | Advanced eXtended Interface                    |

| $\mathbf{BSW}$           | Basic Software                                 |

| $\operatorname{CAN}$     | Controller Area Network                        |

| $\operatorname{CDD}$     | Complex Device Driver                          |

| $\operatorname{CPU}$     | Central Processing unit                        |

| $\mathbf{DCM}$           | Diagnostic Control Module                      |

| $\mathrm{DDR}$           | Double Data Rate                               |

| DID                      | Data Identifier                                |

| $\mathbf{DMA}$           | Direct Memory Access                           |

| $\mathbf{DMAC}$          | Direct Memory Access Controller                |

| DRC                      | Design Rule Check                              |

| $\mathrm{E}/\mathrm{E}$  | Electrical/Electronic                          |

| $\mathbf{ECU}$           | Electronic Control Unit                        |

| EMIO                     | Extended Multiplexed Input-Output              |

| $\mathbf{FPGA}$          | Field Programmable Gate Array                  |

| $\mathbf{FSBL}$          | First Stage Boot Loader                        |

| GIC                      | General Interrupt Controller                   |

| GPIO                     | General Purpose input/output                   |

| $\mathbf{GSM}$           | Global System for Mobile communication         |

| GUI                      | Graphical User Interface                       |

| $\mathbf{hdf}$           | Hardware Description File                      |

| ICAP                     | Internal Configuration Access Port             |

| IDE                      | Integrated Development Environment             |

| IO                       | Input Output                                   |

| IP                       | Intellectual Property                          |

| ISO                      | International Organization for Standardization |

| JTAG                     | Joint Test Action Group                        |

|                          |                                                |

|                              | Level 1<br>Level 2<br>Light Emitting Diode<br>Look Up Table<br>Multiplexed Input-Output<br>On-Board Diagnostics<br>On-chip Memory<br>Original Equipment Manufacturers<br>Open Systems Interconnection<br>Personal Computer<br>Processor Configuration Access Port<br>Protocol Data Unit<br>Programmable Logic<br>Processing System<br>Runtime Environment<br>Reduced Instruction Set Computing<br>Secure Digital<br>Software Development Kit<br>System On Chip<br>Software Component<br>Tool Command Language<br>Unified Diagnostic Services<br>Universal Serial Bus<br>Virtual Functional Bus |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VFB<br>VHSIC<br>VHDL<br>XADC | Virtual Functional Bus<br>Very High Speed Integrated Circuit<br>VHSIC Hardware Description Language<br>Xilinx ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 1 Introduction

Automotive is a fast growing sector where the demands of customers are ever increasing and so is the need to adopt new technologies. A few decades ago, automobiles had simple electrical components but today most of the vehicles have advanced microcontrollers that run real time software [1] which can communicate within themselves and work collectively to improve the drive environment for the users. Several latest advancements like driver assistance systems, autonomous driving, vehicle to vehicle communication, etc., depend heavily on electronics and software. Also the amount of data stored and transferred within vehicles have increased in recent times. Modern day vehicles need advanced Electrical and Electronics (E/E) architectures suitable not only for handling technical challenges but that can also look into factors like passenger convenience, fulfill legal requirements, etc. [2]. A standardized environment for development of these E/E is thus inevitable in such a scenario to manage modifications with better quality. This leads the manufacturers to adopt an open software architecture called AUTomotive Open System ARchitecture (AUTOSAR) [3].

In-order to improve security and safety, it is expected that the Electronic Control Unit (ECU) inside vehicles have some reconfiguration capability [4]. It is well known that Field Programmable Gate Array (FPGA) have the special characteristic that they can be configured and reconfigured after being manufactured. Modern FPGAs have significantly more options like partial reconfiguration, which means that some connections inside the FPGA can be partly changed. Moreover partial reconfiguration can be done without switching the power off. Thus when FPGAs of automotive quality are coupled with AUTOSAR, such that the software in the system is capable of controlling the reconfiguration of hardware, there can emerge a wide range of benefits like hardware re-usability, after-sales modification of circuits and many more.

# 1.1 Background

AUTOSAR is a union formed by leading Original Equipment Manufacturers (OEMs) and the tier 1 suppliers in the automotive sector. Their objective was to define an open standard upon which automotive E/E can be built. AUTOSAR makes it mandatory that the software is developed in a layered architecture with standardized Application Program Interface (API) and thus ensuring portability and hardware independence for the OEM's software [5].

Reconfigurable computing is a widely researched topic in the high performance

computing field. The significance of this approach is that it can combine the benefits of both general purpose processors and Application Specific Integrated Circuit (ASIC) [6]. When there is a computationally intensive task like signal processing or encryption/ decryption, it would be a good option to execute them in specialized hardware units rather than on general purpose processors. In doing so, not only the output is obtained faster but the processor is also allowed to execute other tasks thereby increasing the overall throughput of a system.

Modern System On Chip (SOC) have, within them, processor cores and configurable logic blocks and these even support partial reconfiguration [7]. The fact that these SOCs are available in automotive grades opens up the possibility to exploit the benefits of reconfigurable computing within automotive domain. As more vehicle manufacturers are leaning towards AUTOSAR, if reconfiguration of the hardware could be controlled through AUTOSAR software, it would be suffice to show that reconfigurable computing is feasible wherever needed in the automotive domain.

# 1.2 Aim

The goal of this thesis would be to show the possibility of implementing an ECU which can partially reconfigure an AES encryption and decryption hardware according to requirements, without affecting its other functionalities. The ECU's partial reconfiguration should be controlled by AUTOSAR software running on the same chip based on diagnostic requests from the user.

# 1.3 Limitation

The diagnostics implementation in AUTOSAR is broad. The standard supports a wide range of communication protocols and there are diagnostic services supported for each of them. To maintain simplicity, only requests of the below mentioned services through Controller Area Network (CAN) will be considered. The numbers refer to a service identifier and *service* here represents a request to the ECU from the user (or tester) in CAN message with these identifiers in specific locations.

- 0x23 Read memory by address

- 0x3D Write memory by address

- 0x27 Security Access

Although the implementation for the thesis is limited to these few services, the concept can easily be extended to other services and protocols supported by AUTOSAR.

# 2

# Theory

This chapter gives a small introduction about different software concepts and the hardware used in the thesis.

## 2.1 Open Systems Interconnection

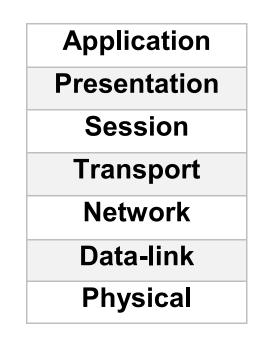

When computing systems need to be connected in a network, there must be a set of rules defined. The International Organization for Standardization (ISO) - Open Systems Interconnection (OSI) is a reference model based on which interconnection standards can be developed [8]. It consists of seven layers namely application, presentation, session, transport, network, data-link and physical as shown in Figure 2.1.

Figure 2.1: The OSI model

According to Mohammed M. Alani each layer handles data differently [9]. He further explains that if Protocol Data Unit (PDU) is considered the unit of data in a layer, then PDU for the physical layer is raw bits and the functionality of this layer

will be to aid in the data transmission between data-link layers of the sender and receiver. The PDU in the data-link layer would be frames and the data link layer will have a wide range of tasks to perform like flow control, error detection, etc. The network layer's PDU is packet. This layer is useful in maintaining communication within a network and controls the routing of messages between networks. The next level is the transport layer with PDU as segment which is helpful in segmenting big data for transmission according to the bus or decoding several packets of data into segments for the above layers. Neither the session layer nor the presentation layer, which are the next two in hierarchy manipulates the data any further. While the former is involved in establishing communication sessions between different units, the latter manages the method in which the data is given to the application. Finally the application layer helps the user communicate with the network.

# 2.2 Automotive Open System Architecture

AUTOSAR is a union of OEMs and other E/E suppliers within the automotive industry [10]. The members of AUTOSAR are brought into a three tier structure namely the **Premium partners**, the **Development partners** and the **Associate partners** sharing different rights and responsibilities [11]. The union works on three major tasks [12],

- Defining the standardized work flow model called the *AUTOSAR methodology* that can aid in sharing of tasks during the development period

- Defining Software architecture

- Defining the different interfaces between the basic software and the application layer

The standard has been continuously evolving since the AUTOSAR release 1.0 in 2005. Such a standardized architecture is supported by OEMs in a view that in the future, their application softwares can be developed independent of the hardware. Also, because of this approach, software module(s) developed for one vehicle model can easily be reused in other models and application software designed to run on a particular ECU can be shifted without much difficulties to another.

AUTOSAR prescribes a layered software architecture. A piece of code with some functionality is called a module and there can be several modules within a layer. The architecture defines the limitations and extent of accessibility for different modules. In doing so, the impact of changes in the code is limited and new software modules can henceforth be added easily without affecting the quality of the other software. This directly reduces the need to test the already existing modules and in-turn can reduce the time to market and the cost of development for a new ECU.

Looking at the benefits, many of the automobile manufacturers have already started to develop their software based on AUTOSAR [13] and the standard is gaining acceptance world wide. The number of ECUs based on AUTOSAR is estimated to rise from 25 million in 2011 to 300 million in 2016 [14] and this figure directly explains the standard's significance.

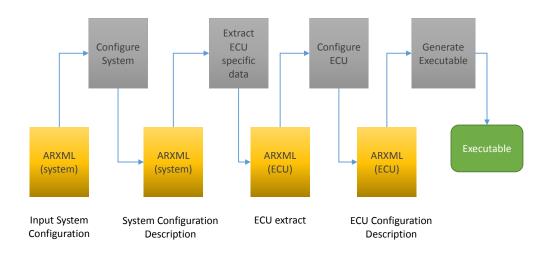

#### 2.2.1 AUTOSAR Methodology

In-order to achieve a model where software development can be done without the knowledge of underlying hardware, few procedures in the system development are to be followed and these are known as the "AUTOSAR Methodology" [15]. According to this, development begins by defining the overall functionality of the software in a vehicle. Then from these functionalities, requirements specific to the system, ECUs and different components of basic software are derived. The derived information is exchanged between different levels in a standard file format called AUTOSAR XML (ARXML). Since the flow is standardized, each part of the system can be developed separately and when adopted properly, different parts of the same software can be developed by various vendors. At some point when individually developed softwares are to be integrated, these ARXML will remain as the reference.

Figure 2.2: AUTOSAR Methodology

An overview of AUTOSAR methodology according to the standard [15] is shown in Figure 2.2. All the yellow boxes are either input or output of the system in ARXML format and the gray boxes are the tasks performed. As shown, the work flow begins with an ARXML file consisting of the system configuration details such as overall software component requirements in the system, ECU resources, bus topology, etc. Based on this input the *configure system* task allocates the application to ECUs, selects the bus topology and performs similar system level mappings and generates another ARXML files consisting all these details. This file now becomes the input to the next task in the work flow, Extract ECU Specific Data task, where details specific to individual ECUs are generated. An ARXML output named ECUextract gets generated and this serves as the input to the next task Configure ECU. During this task, based on the details from the ECU extract, finer details like BSW configuration, etc., needed for the development of software at the ECU level are derived and the output for this stage is the ECU configuration Description which serves as the base for the software development. The next process is the *Generate executable* task which generates the executable for a particular ECU.

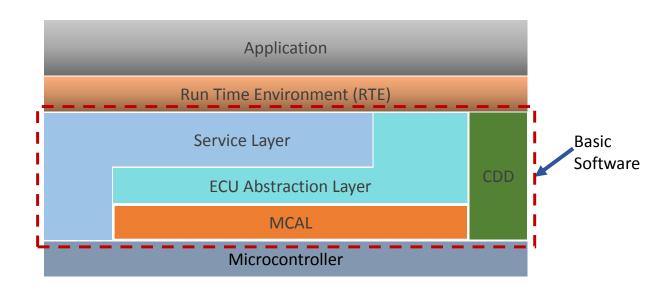

#### 2.2.2 AUTOSAR Software Architecture

The AUTOSAR software architecture mainly focuses on vehicle ECUs which use 16/32 bit micro-controllers and perform tasks at real time based on sensor inputs and other similar ECUs connected in networks [16]. Use of multi-core Central Processing unit (CPU)s is on the rise and the present AUTOSAR software architecture can be extended to support them.

As shown in Figure 2.3, for an ECU with single core, the software primarily consists of three layers namely

- Basic software (BSW)

- Application layer

- Runtime Environment (RTE) also referred as Virtual Functional Bus (VFB)

Figure 2.3: Basic structure of AUTOSAR

#### 2.2.2.1 Application layer

During requirement analysis, all the basic tasks a system should perform are called functional requirements [17]. In the application layer modules performing algorithms to accomplish these functional requirements are placed. The code in this section does not need to know how the system is configured to achieve this. For example, a requirement for the system could be, on a particular condition it should switch on a lamp (indicators) and blink at a particular rate. The code in this section will only control the algorithm for switching on and off the lamp, but details like how this lamp is connected or which port in the micro-controller needs to be switched on and off to achieve this and how the time is calculated are all abstracted.

#### 2.2.2.2 Basic Software

The BSW layer is made up of the service layer, ECU Abstraction layer and the microcontroller abstraction layer. These sections handle the requests from the application layer. As mentioned in the above example, the switching on and off of a lamp could be the request. The basic software layer has in it those finer details like how the lights are connected, which port(s) in the micro-controller needs to be switched, what is that value when assigned to the port will switch the light on/off, calculation of time according to the hardware oscillators that is used, etc., and thus help in achieving the functional requirements of the system.

#### 2.2.2.3 Runtime Environment

The *RTE* links *BSW* with the *application layer*. The common references could be variables in memory. In events like hardware modifications, now it becomes sufficient to modify only the RTE and the application layer code can largely be maintained unaffected.

# 2.3 Diagnostics

Software inside a car has multiple functions. One among them is to monitor the functioning of various units in the vehicles. This feature is called diagnostics and they help the technicians, manufacturers and vehicle owners to know crucial details of various sub-systems [18]. The ECUs inside a vehicle are interconnected for data exchange. They could be connected in the same or different networks. AUTOSAR describes two major diagnostic standards namely

- Unified Diagnostic Services (UDS) [19]

- On-Board Diagnostics (OBD) [20]

The former is based on ISO standard *ISO14229-1* while the later is based on ISO standard *ISO15031-6*. They lie in the application layer of the OSI model.

To read/write information from ECUs, software allows users to send messages in a pre-defined format. These predefined messages are called diagnostic requests and are characterized by a unique number called *Service Identifiers (SID)*. This distinguishes which service is being requested by the user from the ECU. The information sent back by the software is called a diagnostic response and will also posses a corresponding number. If the request message was supported by the ECU and if the software was able to collect the required information then the ECU sends back the read data with a valid response code to the user. In-case the request is not valid or if the ECU had not been able to process the request within a given time, it sends back a negative response.

## 2.4 Controller Area Network

The Controller Area Network (CAN) is a serial communication protocol within a bus network [21]. It is a widely used protocol in automotive industry for communications between ECUs because of its cost effectiveness in comparison with other protocols for a bit rate of  $1 \text{ Mb}s^{-1}$ .

# 2.5 AES

Cryptography is widely used for data security during transmission and storage. Various algorithms exist to do this. The National Institute of Standards and Technology (NIST) [22] is a federal agency within the U.S. Department of Commerce involved in defining standards. In the year 2011, they announced the *Rijndael algorithm* [23] as the Advanced Encryption Standard (AES) [24].

# 2.6 Reconfigurable Computing

The process of using or creating an algorithm to get a desired output is called computing [25]. In electronics, computing is achieved with the help of circuits. If these fundamental circuit configurations are changed within the architecture during run-time, for various reasons like speeding-up the computation, etc., then we obtain reconfigurable computing. Thus this form of computing is heavily dependent on the underlying hardware. Reconfigurable computing is a widely researched topic in the high performance computing domain [26].

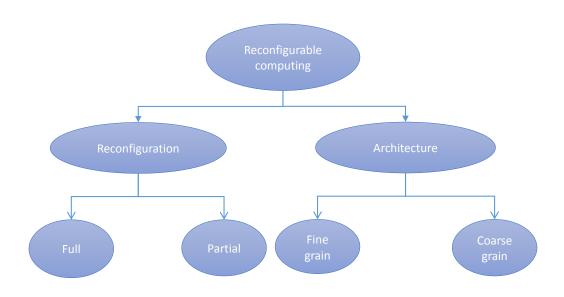

Figure 2.4: Reconfigurable Hardware types

Based on the extent of reconfiguration on circuits, a system can be classified as fully or partially reconfigurable system. During computation, if the whole hardware is to be reconfigured, then the system is called a fully reconfigurable system and on the other hand, if the system has the capability to reconfigure only a few parts of its whole circuitry, then it is called a partially reconfigurable system. Another way of classifying these systems is the smallest level of reconfiguration attainable called granularity. A system where the reconfiguration could be extended to the smallest unit available, like those in FPGAs, are called fine grain systems and those, in which a big circuitry using few basic units is replaced by another big circuit, are called coarse-grained reconfigurable systems [27].

# 2.7 Zynq®

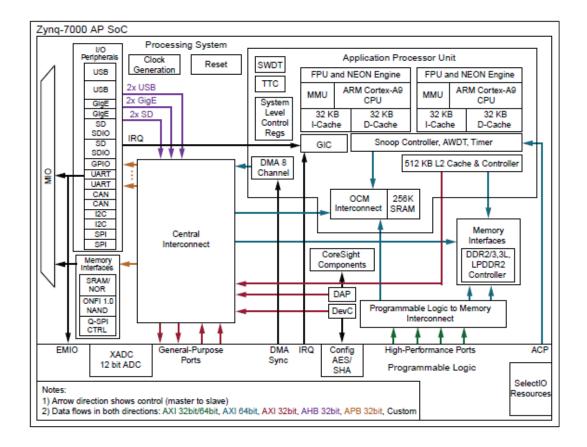

The growth in computing requirements within embedded systems has opened up the need for using high performance computing techniques. Zynq® is a SOC from Xilinx with a general purpose processor cores and a FPGA. Further, Zynq® SOCs are marketed as different variants like 7z010, 7z020, etc., and in this thesis work 7z020 variant is used.

Source: Zynq-7000 All Programmable SoC Technical Reference Manual UG585 (v1.10)

The section holding processing cores and supporting circuits is called a processing system (PS) and the section with FPGA and reconfiguration supporting circuits is called a programmable logic (PL). The block diagram of the SOC can be seen in Figure 2.5. Based on the technical reference manual for Zynq® from Xilinx [28], only those units which are of interest to this thesis, are mentioned below.

#### 2.7.1 Processing System

The PS is divided into four major sections namely the Application Processor Unit (APU), memory interfaces, input-output peripherals and interconnects. The APU comprises of two ARM Cortex<sup>TM</sup> A9 processing cores with 32 KB instruction and data Level 1 (L1) caches. It also has a 512 KB sharable Level 2 (L2) cache with snoop control units to maintain coherency between the L1 and L2 caches. In addition to these the PS also contains 256KB of on-chip memory. The Direct Memory Access (DMA) controller that controls the data transfer between memory and PL/PS independent of processor interventions, the General Interrupt Controller (GIC) that triggers or masks ARM defined interrupts and the watch dog timers are all part of the APU.

The memory interfaces supports Double Data Rate (DDR), quad-SPI, NAND technologies with special controllers. The input-output peripherals within PS consists of configurable General Purpose input/output (GPIO)s, a Secure Digital (SD) controller, CAN controllers, etc., In the interconnects section, there are central interconnects that can connect PL to the external peripherals, OCM interconnect that can connect PL and central interconnect to the OCM and PS-PL interfaces with Processor Configuration Access Port (PCAP) that support CPU controlled reconfiguration of PL and Extended Multiplexed Input-Output (EMIO).

#### 2.7.2 Programmable Logic

The PL section within a 7z020 device is based on Xilinx's Artix®-7 FPGA logic. It comprises of the device configuration module (devc) that helps configuring or reconfiguring the FPGA from the PS logic. It also has the Xilinx ADC (XADC) that helps in monitoring voltage and temperature inside the device are present also available in addition to the FPGA logic within the PL section. Interconnections between the PL and the PS is supported through the Advanced eXtended Interface (AXI). The major resources available in the 7z020 FPGA logic can be seen in Table2.1.

| Sl No. | Resource         | Size   |

|--------|------------------|--------|

| 1      | Logic Slices     | 13300  |

| 2      | Look-up Tables   | 53200  |

| 3      | Memory Resources | 560 KB |

|        | Block RAM        | 140    |

| 4      | I/O bank count   | 4      |

| Table 2.1: | Composition | of FPGA | in | 7z020 | device |

|------------|-------------|---------|----|-------|--------|

|------------|-------------|---------|----|-------|--------|

# 3

# Methods

In this chapter, the software and hardware selection criteria and the intended feature addition as of the thesis work are discussed.

## **3.1** Software and Hardware Selection

The initial work in the thesis was to find a platform to start the work. It involved selection of the hardware and software to be used. The software to be used should be in compliance with AUTOSAR and the hardware to be chosen needs to have capability for both running an AUTOSAR software and supporting reconfigurable computing.

#### 3.1.1 AUTOSAR Software

The AUTOSAR consortium works only on defining standards for the software and does not force the implementors to develop their solutions using any particular method. This strategy is followed in-order to encourage competition and innovation [2]. As a result, there are 76 vendors (as of April 08, 2016) who can deliver AU-TOSAR based products [29]. It is also important to note that these products are mostly proprietary.

Arccore AB [30], a Swedish company is one of the leading vendors in the automotive software market. Their product *Arctic core* comprises a complete embedded platform based on AUTOSAR. Further *Arctic core* is released under both GNU General Public license v2 and a commercial license making it best suitable for the thesis work.

#### 3.1.2 Hardware

As explained in section 2.7, Zynq<sup>®</sup> is a System On Chip (SOC) from Xilinx with a unique design. It has a PS with two ARM<sup>®</sup> processing cores and a PL that can be used to implement hardware designs. Zynq<sup>®</sup> has hardware that can support partial reconfiguration of the PL. Arctic core already supports Zynq<sup>®</sup> and thus it became the natural choice for this work.

# 3.2 Intended System

As mentioned earlier *arctic core* supports Zynq® architecture, but only to the extent that AUTOSAR software can be run on its PS. There is no option to control partial or complete reconfiguration of PL with PS.

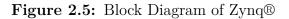

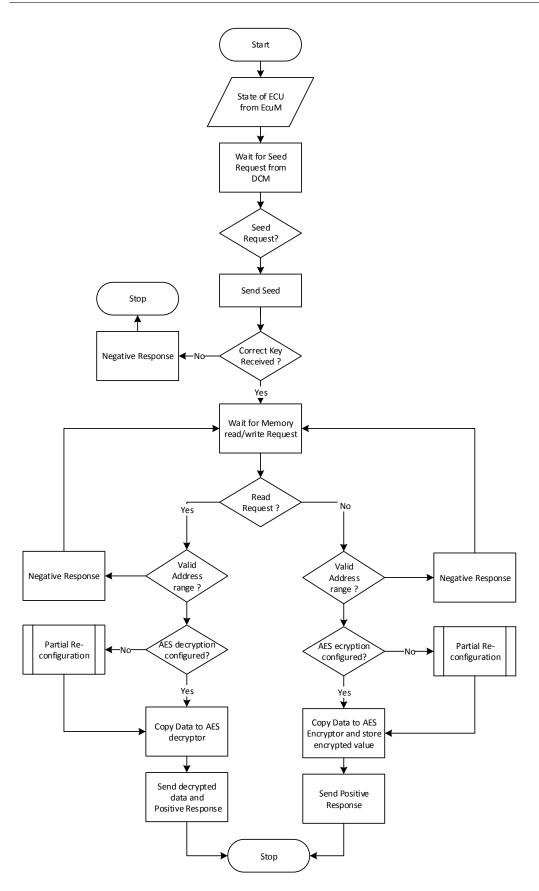

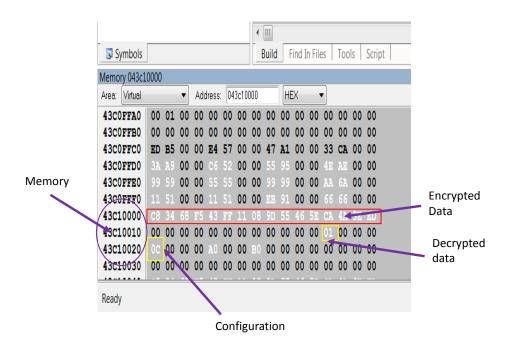

With the focus to showcase the capability of AUTOSAR software controlled reconfigurable computing, a simple system whose hardware configuration in PL can be modified between 128 bit AES encryption or decryption algorithm according to diagnostic requests from the user that will allow users to write into or read from a limited range of memory addresses after establishing a secured session is intended. The AES will be memory mapped and the software will know this address. The logic of the system is shown in Figure 3.1.

- The AUTOSAR software must know the initial hardware settings in the PL and it should keep monitoring for the diagnostic requests from the user.

- When there is a diagnostic request from the user requesting security access (service 0x27), there will be a number sent to the user as response known as *Seed*.

- If the user replies to that *Seed* with a matching predefined number called *Key*, the software will enable access to the previously inaccessible memory regions. This access will be available to user only for a fixed amount of time and the ECU identifies this as a secured session.

- If needed the secured session can be extended for a predefined time by a tester using *tester present* requests.

- When the secured session is established and if a correct memory read request (service 0x23) for a particular address in the memory is sent, the software will check for the configuration available in PL. If the present circuit is for AES encryption, then the software should reconfigure the hardware to AES decryption first and then try to read the data from it. Otherwise the software should directly read the value from AES. The AES unit, in-turn should read the corresponding memory location. When the memory address requested is accessible, the software should respond to the tester with a positive response along with the read data (in decrypted format). In all other cases there should be a negative response.

- Similarly, when the secured session is established and if a correct memory write request (service 0x3D) for a particular address in the memory is requested, the software will check for the configuration available in PL. If the present circuit is for AES decryption, then the software should reconfigure the hardware to AES encryption initially and then try to write into it. Otherwise the software should directly try to write into AES. The AES ciruit will then write the data into the corresponding memory location. When the address requested is accessible and write is performed, the software should respond with a positive response to the tester confirming that the write was successful. In all other cases there should be a negative response.

Figure 3.1: Intended Design Flow

Implementation of the above idea can be separated into hardware and software development. While the software part involves configuring an AUTOSAR ECU with necessary functionalities, the hardware part involves designing 128-bit AES encryption and decryption units. The procedures followed are described in detail in the following chapters.

## 3. Methods

# Software

The software design started with understanding the basics of the AUTOSAR architecture, learning how *arctic core* implements this and usage of *arctic studio*. It also involved exploring AUTOSAR methodology and understanding the usage of tools for this purpose. As a part of the software development two major points were to be considered.

- Firstly, the software should be capable of supporting CAN diagnostics and it should respond to only specified requests.

- Secondly, there should be a logic within the software that can verify the present hardware configuration in the Zynq®'s PL and perform a reconfiguration if needed.

The chosen AUTOSAR software (*arctic core*) is capable of running on different hardware and it can also support CAN diagnostics. But it has to be configured according to the project requirements. Further to bring in reconfiguration of hardware, the software needed a Complex Device Driver (CDD). In this chapter the details of tools used in software designing, the need for a CDD, various considerations and strategies adopted in CDD development along with the reasons for adopting such a flow are explained in detail.

## 4.1 Development method

AUTOSAR defines a standardized way of defining and sharing tasks during software development. As a result of such a methodology, simultaneous development of various software components becomes possible. Further multiple vendors can be involved in the development of these components. In this section, an introduction to the *AUTOSAR development method* and the application of it from the thesis perspective is presented.

#### 4.1.1 Design Strategy

In the case of this thesis work, the focus is at the ECU level and the objective is quite straight forward that the designed software must respond to selected diagnostic requests from the tester and then if needed control dynamic reconfiguration of Zynq® hardware. Arccore AB's Arctic Core software is used as the basic software. Arctic Core is compliant to AUTOSAR 4.0 and has in it all the basic components of an AU-

TOSAR software. Further, Arctic Core provides basic support for the Zynq SOC. However at present, the software does not have the capability to exploit Zynq's reconfigurable computing feature. Thus for the proposed system, software design should involve

- 1. Configuation of *Arctic Core* such that it responds to needed diagnostic requests.

- 2. Additional code in *Arctic Core* that allows it to support reconfiguration of *Zynq*®'s PL.

#### 4.1.1.1 Simple Example

According to AUTOSAR standards, to begin ECU development, an ECU extract that contains information regarding all the basic configurations required at the ECU level is needed. When Arctic Core software is downloaded, it contains a set of example configurations. The **Hello World** is one such simple example for a basic ECU and it consists of a configuration ARXML file (HelloWorld\_Generic.arxml), resembling an ECU's requirement derived from a full system. It also has an application module that can control the blinking of one or more Light Emitting Diodes (LEDs). In-order to simplify things, except for a few features most of the others are disabled using the configuration file. The Hello World example can be run on various boards after generating executables with corresponding configuration files for different hardware. So, the example configured for Zynq hardware was chosen to be the base for this thesis work.

#### 4.1.1.2 Configuring Arctic Core for diagnostic requests

The Diagnostic Control Module (DCM) exists in the communication layer of the AUTOSAR architecture and is responsible for monitoring diagnostic requests and permitting the ECU to service these requests based on the present session and diagnostic states [31]. Analysis showed that, within the present software configuration, it would be suffice to configure only the DCM to achieve services for all the intended diagnostic requests.

#### 4.1.1.3 Choice of a Complex Device Driver

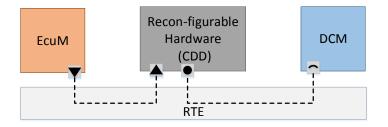

When there is a need to introduce new concepts in AUTOSAR, a non standardized software entity called Complex Device Driver (CDD) can be used. The CDD, as any other software component can interact with basic software modules of the AU-TOSAR with few restrictions as mentioned in [32]. The concept of reconfigurable computing requires quick access to hardware and further it is not standardized by AUTOSAR. Thus a CDD that can monitor and control reconfiguration was added to the design.

# 4.2 Design

The requirement to configure the DCM module was straight forward. But the design of a CDD is not standardized by AUTOSAR and the Zynq® architecture supports hardware reconfiguration in different ways. As a result, several solutions were found feasible to achieve the intended system. During the design of the CDD, two major questions were to be answered.

- 1. Where should the CDD be placed in the design?

- 2. How should the CDD control the hardware reconfiguration?

## 4.2.1 Location of CDD

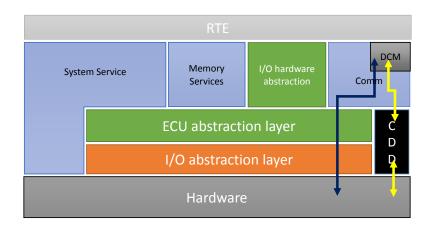

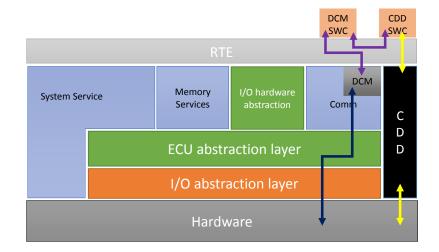

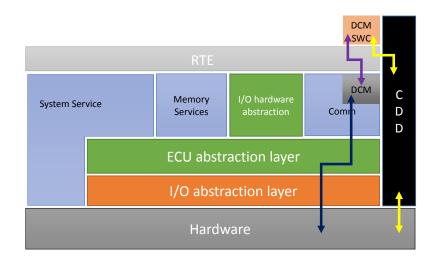

Based on requirement, the CDD should control reconfiguration of hardware based on diagnostics which is handled by DCM. This means there should be a way to establish communication between CDD and DCM. To achieve this, three different configurations were considered and these are shown in Figure 4.1. The Arrows indicate the flow of information or requests.

**Option (a)** shows the possibility of implementing the CDD within Basic Software (BSW). Under this design the communication between CDD and DCM is direct.

**Option (b)** shows a design to implement the CDD as a BSW and design a software component for both CDD and DCM. The communication between CDD and DCM will in this case be through Runtime Environment (RTE) with the aid of implemented Software Component (SWC)s.

**Option** (c) shows a design with CDD as a single SWC. There is also a DCM software component to be implemented. The communication between CDD and DCM here will also be through the RTE.

Under the given designs, option (a) will only allow BSW modules to communicate with CDD. The software components have no direct access to the CDD and this can limit those software components willing to control reconfiguration and thus was not chosen for implementation. Options (b) and (c) can be designed to allow both BSW modules and SWC to control reconfiguration. With simplicity in focus, option (c) was chosen for implementation.

#### (a) CDD entirely in BSW

(b) CDD as two modules, one in BSW and the other as a software component

(c) CDD entirely as a software component

Figure 4.1: Possible locations for CDD

#### 4.2.2 Control of reconfiguration

As mentioned before Zynq architecture has two Cortex-A9 CPUs, Direct Memory Access (DMA), etc., and there are various ways to control the PL reconfiguration. According to [28], reconfiguration can be controlled through either ICAP or PCAP, but for the reconfiguration to be controlled by the processor, PCAP must be used. There are other ways of doing this, like establishing a reconfigurable port in the hardware which on receiving interrupts from processor can begin reconfiguration.

# 4.3 Tools Used

During software design, *arctic studio* from Arccore AB and *winIDEA* from iSYSTEM were widely used. These tools are proprietary. Details regarding version and their usage are discussed in this section.

## 4.3.1 Arctic Studio

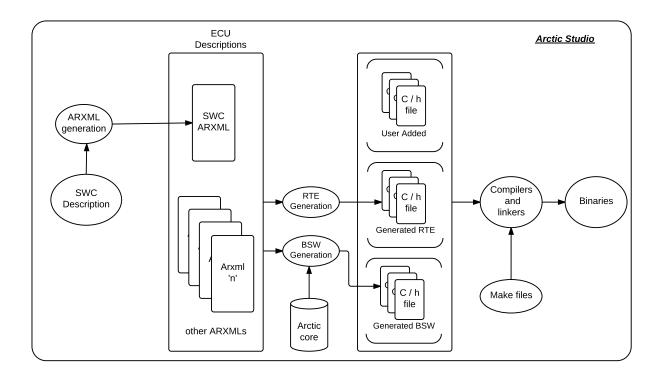

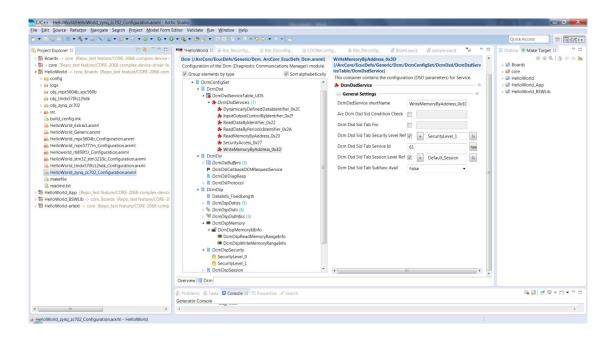

Arctic studio [33] is a collection of different tools presented as a single package by Arccore AB. To define it in simple words, it is an Integrated Development Environment (IDE). Software development, integration, etc., can be performed in the same tool. The version of Arctic Studio used in the project was 10.0.0. Functioning of this tool from the perspective of project is shown in Figure 4.2.

Figure 4.2: Arctic Studio work flow

The user's primary objective is to supply the tool with all the configuration details in the form of ARXMLs. To populate the information about SWC, each SWC is briefed using *ARText*. *ARText* is a framework defined by AUTOSAR Tool Platform (Artop) for modeling Software Component (SWC)s [34]. The external ports of a SWC and the connections between the considered module and other SWCs are listed out during this modeling. After individually defining all the software components, the descriptions are converted into ARXML files. The functionalities of SWC are coded separately with the help of text editors within *arctic studio*. The defined SWCs are instantiated into the design with help of another tool called *RTE editor*.

The next step is to configure the BSW. The functionalities of the BSW are coded in *Arctic Core*, but are very generic. Thus they must be configured with respect to the design needs. ECU configurations are made available to the tool in ARXML format and are referenced by another tool within the *arctic studio* environment called the *BSW editor*. Once all the configurations are present, the files for both BSW and RTE are generated with a single button click. The files are generated in \*.c and \*.h format.

Finally, the tool also contains a build system specific to all supported hardwares with reference to required compilers and linkers. With the help of build system executables (binaries) can be easily generated.

#### 4.3.2 winIDEA

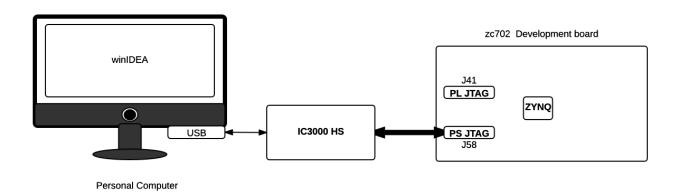

WinIDEA is an IDE from iSYSTEM [35]. The build used in the thesis work was 9.12.125. It was used extensively along with iC3000 HS, a debugger unit [36] and the connection setup is shown in Figure 4.3. As explained in the previous section arctic studio was used to develop required software, but it cannot be used to run programs on the hardware. Thus winIDEA along with iC3000 HS were useful in understanding the software flow and also for on-board debugging.

Figure 4.3: Programming Zynq® with winIDEA

Zc702 development board has two Joint Test Action Group (JTAG) connectors

that allows programming Zynq?'s PS (through pins J58) and PL (through pins J41) separately. Thus *iC3000 HS* with a USB port and a Joint Test Action Group (JTAG) port was used to bridge the connection between the Personal Computer (PC) and J58 of zc702.

# 4.4 Implementation

The implementation started with analyzing the Hello World example. The various components present and the configuration of DCM module were studied. The CDD was then added to the design.

## 4.4.1 Hello World

The Hello World example with the Arctic core release contained a simple ECU configurations necessary to run a software on the hardware with the communication ports enabled. The example could support different boards and thus the configuration available for the Zynq hardware was selected. The executable was generated with the help of Arctic studio and it was loaded on to the hardware with then help of winIDEA. The executable could periodically blink the LEDs in the zc702 board. Further when it was connected to CAN simulation tool (Busmaster) [37] and if random messages were sent with CAN id 0x01, the loop back program available with it responded by sending back the same sent data in another message with CAN id 0x02.

## 4.4.2 Diagnostic Control Module

The next step was to configure the *Hello World* so that it responds to the necessary diagnostics. To achieve this analysis showed that only the DCM module's configuration needed change. So the corresponding *ARXML* was opened in *BSW editor* within *arctic studio*. The configuration was done at four levels.

- 1. **DcmGeneral:** Basic configurations like the support for error detection, maximum dynamic identifiers to be supported can be configured here.

- 2. **DcmDsd:** The list of services supported by the DCM, for e.g service 0x22: Read Data Identifier (DID) can be configured.

- 3. **DcmDsl:** The parameters controlling the session layer of DCM, like the list of protocols to be supported, etc., are listed here

- 4. **DcmDsp:** The finer details of the services supported by the DCM, for example if the module supports memory read services, then details like the memory range accessible, the security session in which the ECU should remain to access these memory addresses can be configured here.

To achieve the desired functionality, the DCM must support services 0x27, 0x23 and 0x3D; Further it should be capable of establishing a secured session in which a limited range of memory is accessible for read and write. The configurations required with respect to individual services are listed in table 4.1.

| Diagnostic Service    | ID                                                      | Needed Changes                         |  |

|-----------------------|---------------------------------------------------------|----------------------------------------|--|

| SecurityAccess        | 0x27                                                    | a. Add service to supported list       |  |

|                       |                                                         | b. Additional security session support |  |

| ReadMemory by Address | adMemorybyAddress 0x23 a. Add service to supported list |                                        |  |

|                       |                                                         | b. choose accessible memory range      |  |

|                       |                                                         | b. choose accessible security session  |  |

| WriteMemorybyAddress  | 0x3D                                                    | a. Add service to supported list       |  |