# Evaluation of emerging additive technologies for circuit board manufacturing

In production and development projects

Master's Thesis in Product Development

Gustaf Almquist

# Evaluation of emerging additive technologies for circuit board manufacturing

In production and development projects

Master Thesis Report

**Gustaf Almquist**

# Evaluation of emerging additive technologies for circuit board manufacturing

In production and development projects

**Gustaf Almquist**

© Gustaf. Almquist, 2019.

Examiner: Eduard Hryha

Department of Industrial and Materials Science Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone + 46 (0)31-772 1000

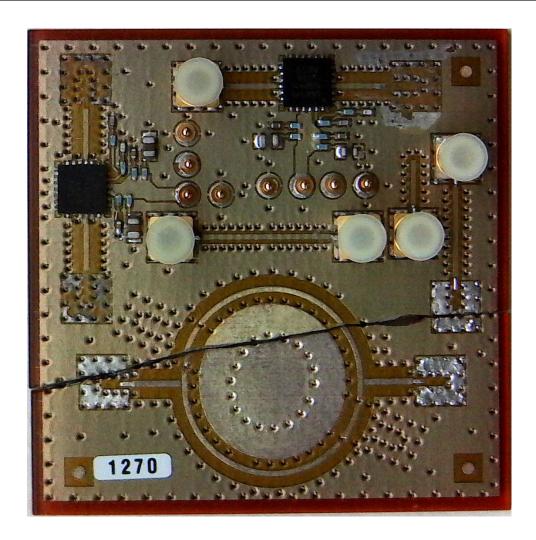

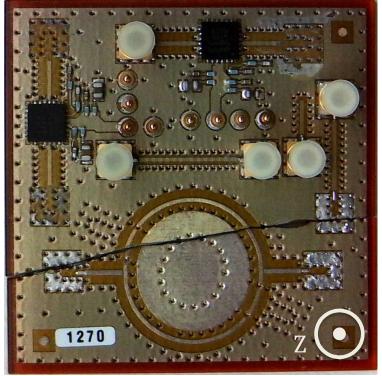

Cover: Printed evaluation board after assembly and soldering, More information found in the chapter on Evaluation Board Development on page 33.

Department of Industrial and Materials Science Göteborg, Sweden 2019

## **Abstract**

This thesis is focused on introduction of the state-of-the-art additive manufacturing process for circuit board manufacturing in the development process. Project was carried out at Saab AB during 2018 and is done in collaboration with the department for Industrial and Materials Science at Chalmers.

Focus of the thesis is to evaluate the possibilities and limitations of the recently developed manufacturing technology, that allows for additive manufacturing of a Printed Circuit Board (PCB). The technology was developed and launched by Nano Dimensions Ltd in the autumn of 2017. The additive manufacturing technology used is based on modified material jetting process that utilizes an ink containing silver or copper nano-powder in one printing head, and dielectric ink in other. This allows for simultaneous printing of both materials.

After printing, green part is cured at elevated temperature in order to sinter metal nano-powder and cure dielectric material. This is done by exposure to light from a photonic curing lamp after each layer is deposited. This allows to produce complex two- and three- dimensional circuit boards, providing the possibility to significantly speed-up process of PCBs development and prototyping. It also allows for manufacturing 3D PCBs, not possible with the conventional technologies.

Focus is on the evaluation of the performance of the PCBs, made by new technology, extensive characterisation of the microstructure of the PCBs, as well as defects and flaws that can affect its applicability. The results were used to estimate applicability of this technology at Saab. Product Lifecycle (PLC) for the PCBs made by this technology was evaluated as well.

Thesis also covers development of a method for evaluation of the new processes for PCB development following lean testing and qualitative methodology. While including stakeholders in the process and managing risks, it also discusses current state of additive manufacturing of electronics. For this purpose, an evaluation board was developed and printed using the new process. Unfortunately, the board broke during assembly, but material testing and inspections have given insights into the current state of PCB 3D-Printing.

Additive manufacturing of circuits and especially PCBs stand to develop rapidly over the coming years. Even at their current stage they allow to speed up development and allow for quick production of small series for production. Current limitations in additive processes limits its implementations but allows for rapid prototyping of low- to mid- frequency circuits. The technology shows promising results and potential to remove logistic bottlenecks, reduce waste and reduce the need for end of life purchase of components.

Keywords: additive manufacturing, material jetting, PCB, electronic development, prototyping process, DRL

## Acknowledgements

Chalmers and my Examiner for allowing me the opportunity to conduct this thesis.

The PCB development department specifically and Saab in general for allowing me to evaluate an exciting new technology and even as a company first for a thesis worker travel to a big technology fair in another nation. Over the course of the thesis I have had helpful discussions with many engineers at Saab and would like to say that you all have been awesome!

Huge thank you to my supervisors at Saab, you helped me with the project and allowed me to utilise your large network to get into contact with experts within the different fields. Outside of my supervisors, two persons at Saab have stood out in the amount of help, to Åsa and Theofilos I say thank you, the evaluation board wouldn't be what it is without you!

A thank you to the management at Pluspole for allowing me to disturb your technicians and engineers with my questions, for mentioned people for answers and discussions. Also, thanks for allowing me to photograph parts of your production and prototyping setup.

A special thank you to Artem Roev, for explaining and showing how PhD students at Chalmers work regarding PCB prototypes, also, for showing some of the challenges that can arise from subpar manufacturing processes.

Nano Dimensions for supplying an evaluation board for testing and for answering loads of questions over email. Especially a large thank you to the representative from Nano Dimensions for answering every question I had over the better part of three hours and even taking time over lunch to do so, I appreciate your contribution.

## Acronyms

AM - Additive Manufacturing

BOM - Bill of Material

CAD - Computer-aided design

CAM - Computer-aided manufacturing

**CNC - Computer Numerical Control**

CW - Continuous Wave

DFA - Design for assembly

DFM - Design for manufacturing

DoD - Department of Defence

DRL - Development Readiness Level

EDX - Energy Dispersive X-ray

FDM - Fused Deposition Modelling

FFF - Fused Filament Fabrication

HF - High Frequency

IR - Infrared Radiation

LS - Laser Sintering

MRL - Manufacturing Readiness Level

NFC - Near Field Communication

PCB - Printed Circuit Board

PD - Product Development

PLC - Product Lifecycle

RF - Radio Frequency

RM - Risk Management

RnD/R&D - Research and Development

RP - Rapid Prototyping

SEM - Scanning Electron Microscope

SLS - Selective Laser Sintering

STL - Stereolithography

TDB - Test Design Build

TLB - Test Learn Build

TFT - Thin-film Transistor

TRL - Technology Readiness Level

UV - Ultraviolet

VIA - Vertical Interconnect Access

## Content

| 1. INTRODUCTION                                                                                | 1          |

|------------------------------------------------------------------------------------------------|------------|

| ~ · · ·                                                                                        | _          |

| Background                                                                                     | 1          |

| Aim                                                                                            | 2          |

|                                                                                                |            |

| Research questions                                                                             | 3          |

| Limitations                                                                                    | 2          |

| Limitations                                                                                    |            |

|                                                                                                |            |

| 2. METHODOLOGY                                                                                 | 4          |

| Research approach                                                                              | 5          |

| 2000a 02 app. 2002                                                                             |            |

| Ethics and environmental concerns                                                              | <i>6</i>   |

|                                                                                                |            |

| 3. THEORETICAL FRAMEWORK                                                                       | 7          |

|                                                                                                | _          |

| Evaluation and rating methods                                                                  |            |

| Technological Readiness Level (TRL)                                                            |            |

| Manufacturing Readiness Level (MRL)                                                            |            |

| Manufacturing Capability Readiness Level (MCRL)                                                | 10         |

| Risk Management (RM)                                                                           | 10         |

| Summary and conclusion on available evaluation methods                                         | 12         |

| Development process and workflow                                                               | 13         |

| Agile Development and Scrum                                                                    |            |

| Lean Product Development (LPD)                                                                 | 15         |

|                                                                                                |            |

| 4. DEVELOPMENT READINESS LEVEL (DRL)                                                           | 17         |

| Definitions                                                                                    | 15         |

| Definitions                                                                                    | 1 /        |

| Usage of the DRL method                                                                        | 20         |

|                                                                                                |            |

| 5. EVALUATION OF PCB PROTOTYPING METHODS AND THEIR MATERIALS                                   | <b>2</b> 1 |

|                                                                                                |            |

| Manufacturing methods                                                                          |            |

| Material jetting                                                                               |            |

| Etching                                                                                        |            |

| TFT Circuits                                                                                   |            |

| External manufacturing                                                                         |            |

| Summary and selection of method for further evaluation                                         | 23         |

| Materials for Additive Manufacturing, their properties, health risks and environmental impact. | 24         |

| Materials used for additive manufacturing of PCBs                                              |            |

| Health                                                                                         |            |

| Environmental concerns                                                                         | 26         |

| 6.   | EVALUATION BOARD DEVELOPMENT                      | 27   |

|------|---------------------------------------------------|------|

| Wh   | nat to test and how to test it                    | 27   |

|      | Identification of Lead users and Stakeholders     |      |

|      | Identified user needs                             |      |

|      | Requirements                                      |      |

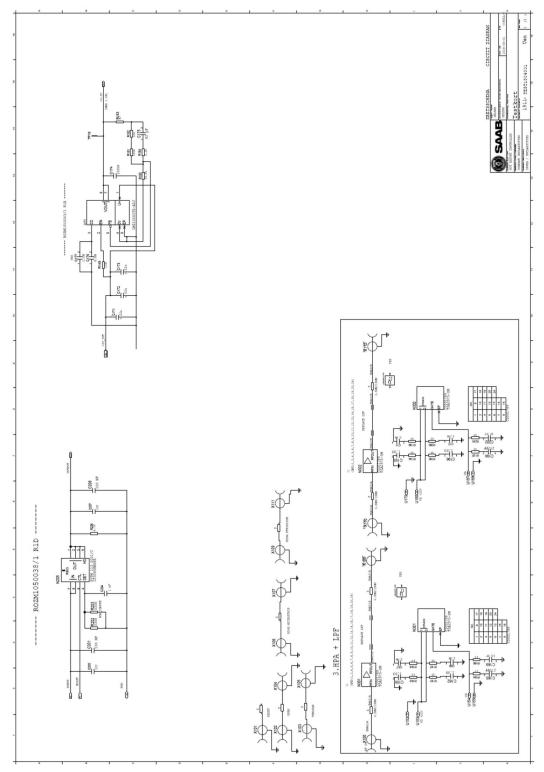

| Sch  | nematic of evaluation board                       | 29   |

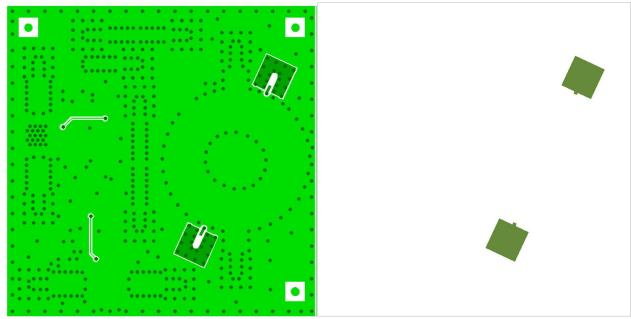

| Lay  | yout of evaluation board                          | 30   |

| Sna  | ecial structural components on the PCBs           | 21   |

|      | Calibration traces                                |      |

|      | Filters                                           |      |

|      | Ring oscillators                                  |      |

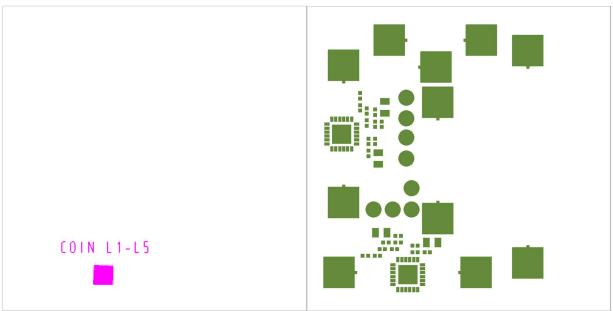

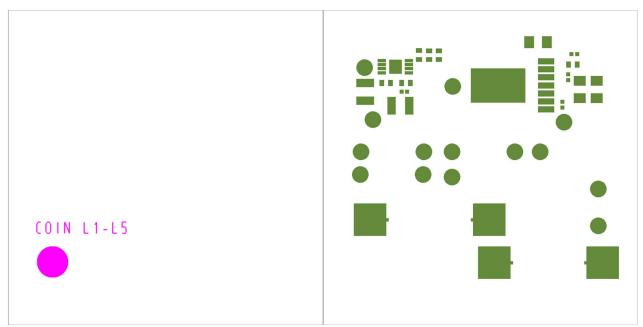

|      | Copper coins                                      |      |

| Fina | nal assembly and verification thereof             | 34   |

| 7.   | RESULTS AND FINDINGS                              | 35   |

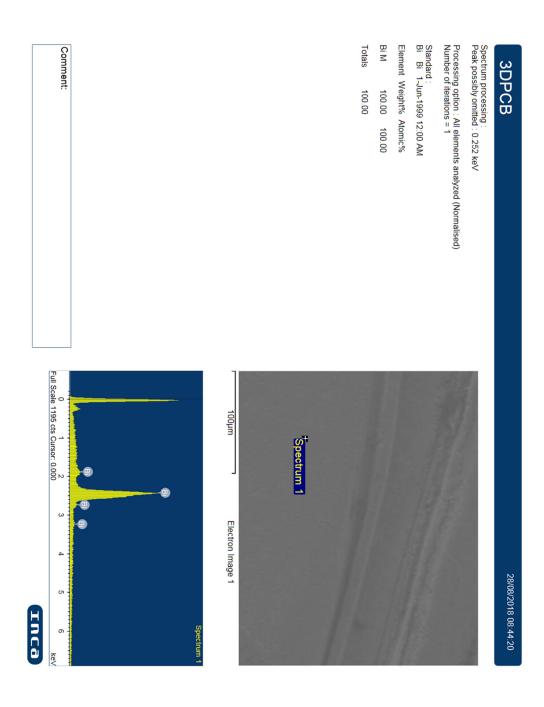

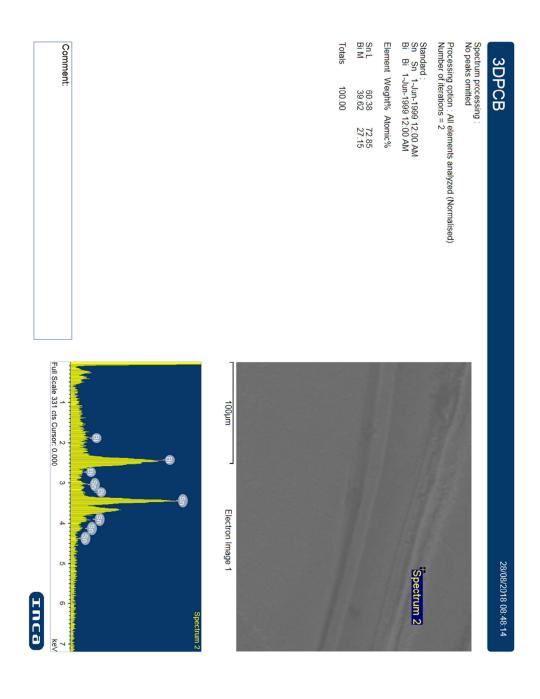

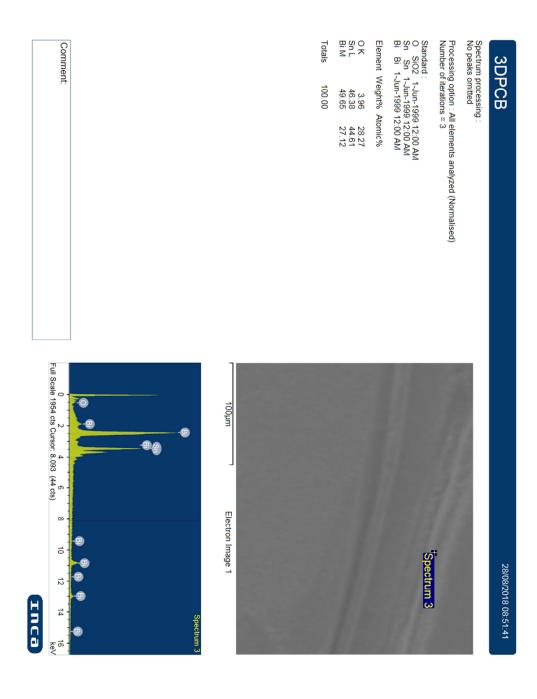

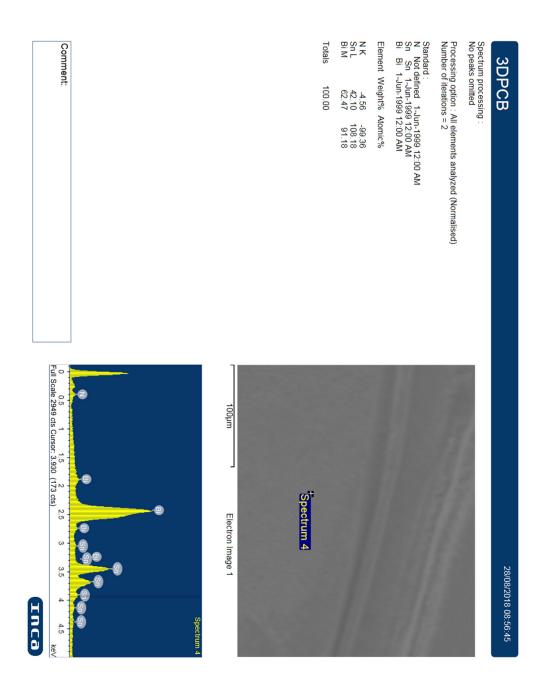

| Mic  | crostructure evaluation of AM fabricated PCB      | 35   |

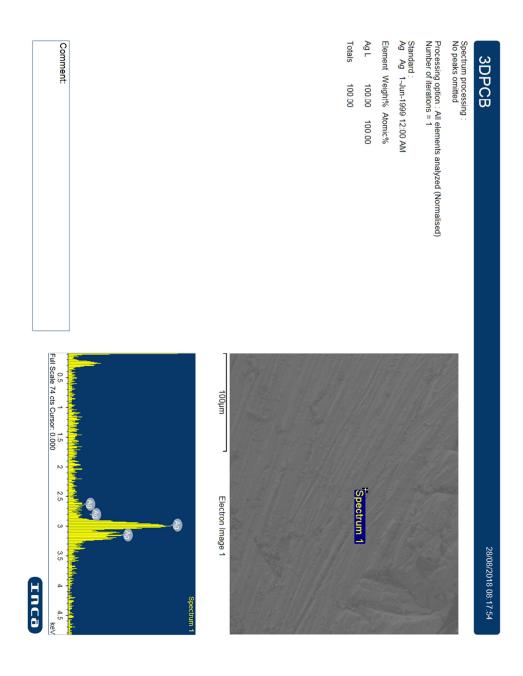

|      | SEM Scanning Electron Microscope inspection       |      |

|      | Material composition                              |      |

| Elec | ectrical testing                                  | 41   |

|      | High frequency, Ring oscillators and filters      |      |

|      | Conductivity                                      |      |

| Sun  | mmary of testing                                  | 42   |

| 8.   | DISCUSSION                                        | 43   |

| 9.   | CONCLUSION                                        | 46   |

| 10.  | . REFERENCES                                      | 47   |

| API  | PPENDIX A: EVALUATION BOARD SCHEMATIC             | XLIX |

| API  | PPENDIX B: EVALUATION BOARD 1 LAYOUT              | L    |

| API  | PPENDIX C: EVALUATION BOARD 2 LAYOUT              | LII  |

| API  | PPENDIX D: EVALUATION BOARD BOM                   | LIV  |

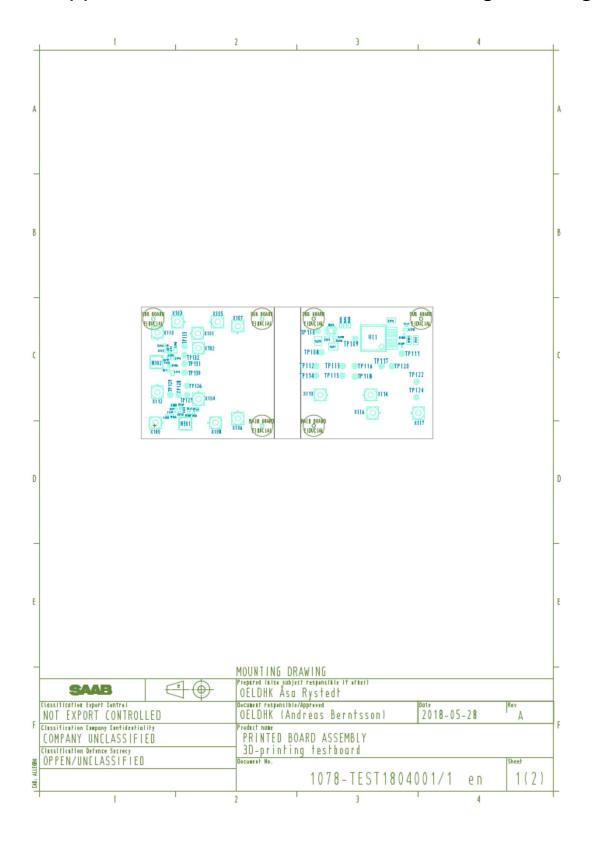

| API  | PENDIX E: EVALUATION BOARD MOUNTING DRAWING       | LV   |

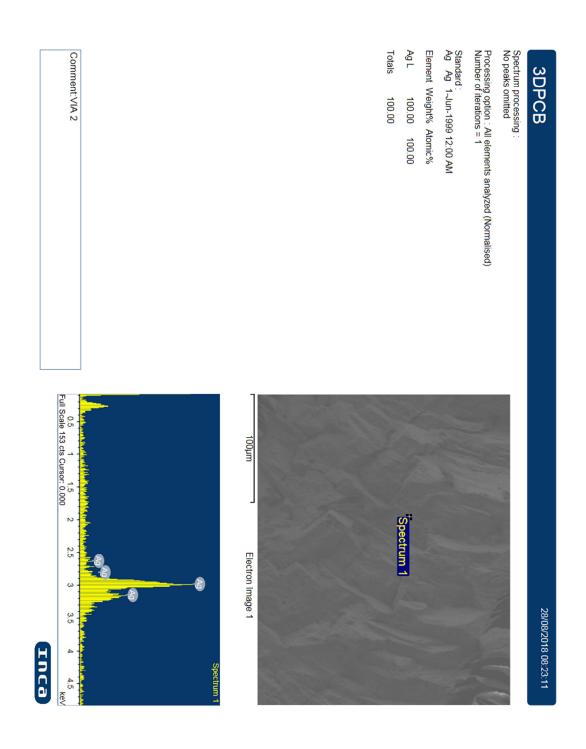

| API  | PPENDIX F: SEM+EDX ANALYSIS- SOLDER SURFACE 10 KV | LVI  |

| API  | PPENDIX G: SEM+EDX ANALYSIS- SOLDER SCRATCH 10 KV | LVII |

| APPENDIX H: SEM+EDX ANALYSIS- SOLDER SCRATCH 20 KV | LVIII |

|----------------------------------------------------|-------|

| APPENDIX I: SEM+EDX ANALYSIS- SOLDER SURFACE 20 KV | LIX   |

| APPENDIX J: SEM+EDX ANALYSIS- POLISHED VIA -10 KV  | LX    |

| APPENDIX K: SEM+EDX ANALYSIS VIA - 10 KV           | LXI   |

# Figures

| Figure 1: General overview of the proposed DRL method                                      | 17       |

|--------------------------------------------------------------------------------------------|----------|

| Figure 2: Detailed overview of the different stages of the proposed DRL method             | 20       |

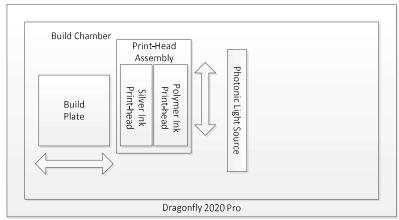

| Figure 3: Dragonfly 2020 Pro Internal Layout                                               |          |

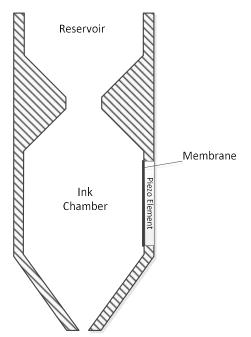

| Figure 4: Model of a piezoelectric printing nozzle                                         | 22       |

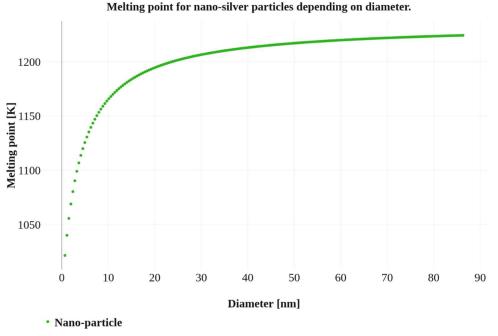

| Figure 5: Melting point of nano-silver particles depending on diameter. Source of data VSI | Particle |

| [20]                                                                                       | 25       |

| Figure 6: Schematic of Evaluation Boards                                                   |          |

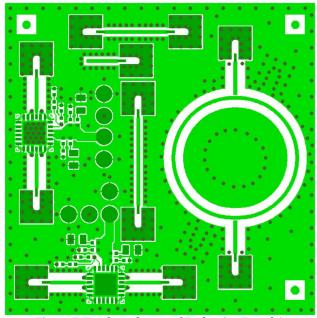

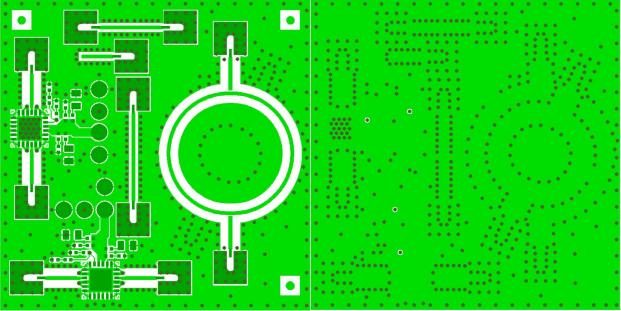

| Figure 7: Top layer layout of Evaluation Board 1                                           | 30       |

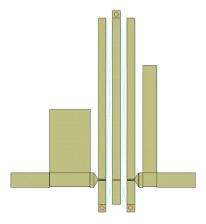

| Figure 8: Microstrip Filter Layout                                                         |          |

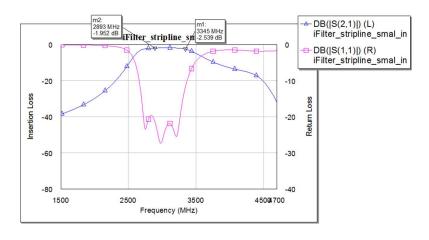

| Figure 9: Simulated frequency response of the Stripline filter                             | 31       |

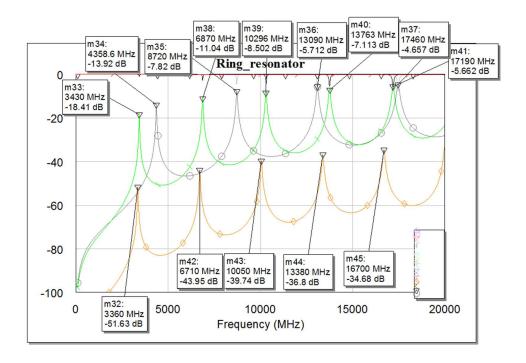

| Figure 10: Simulated frequency response of microstrip ring oscillator                      | 32       |

| Figure 11: Evaluation Board after assembly                                                 |          |

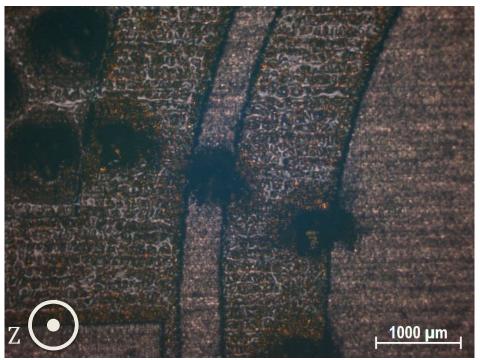

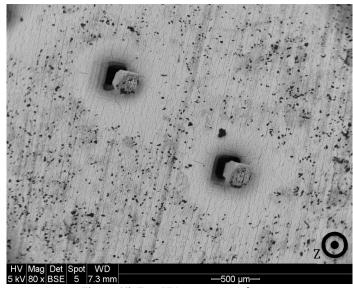

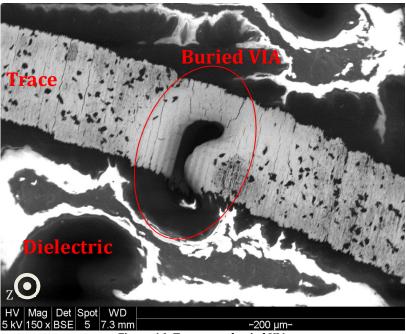

| Figure 12: Indention from buried VIA in conductive trace                                   | 35       |

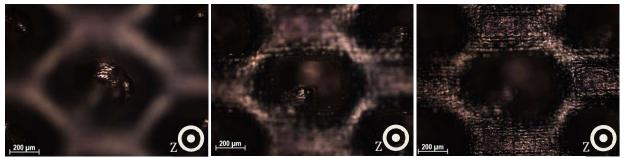

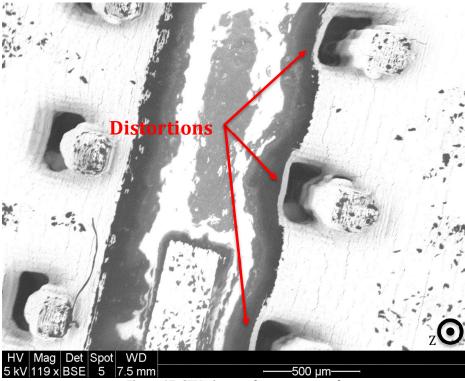

| Figure 13: 3 different focus depths on VIA cavity, Bottom, Middle and Top                  | 36       |

| Figure 14: Nano Silver Leakage: lines of leakage extending from the edge of traces         | 36       |

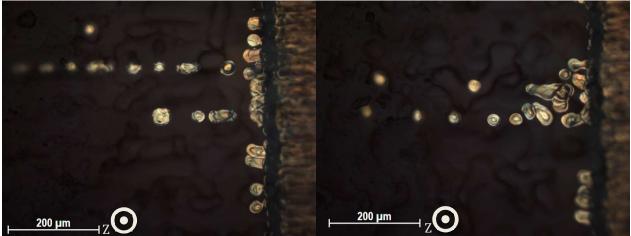

| Figure 15: Two VIAs on a ground pour                                                       | 37       |

| Figure 16: Trace over buried VIA                                                           |          |

| Figure 17: SEM picture of a connector pad                                                  |          |

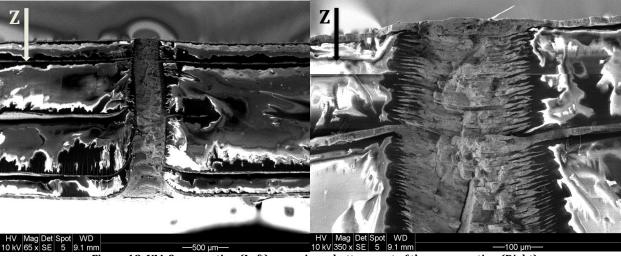

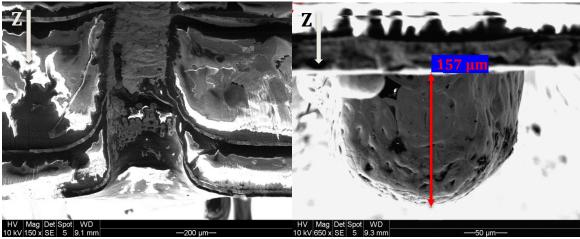

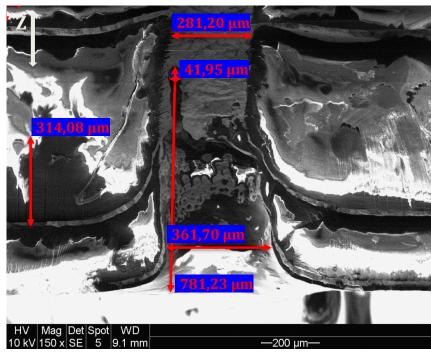

| Figure 18: VIA Cross-section (Left), zoom in on bottom part of the cross-section (Right)   |          |

| Figure 19: Cross-section of top cavity (Left), side view of VIA bump (Right)(Right)        |          |

| Figure 20:Cross-section of top cavity with measurements of cavity dimensions               |          |

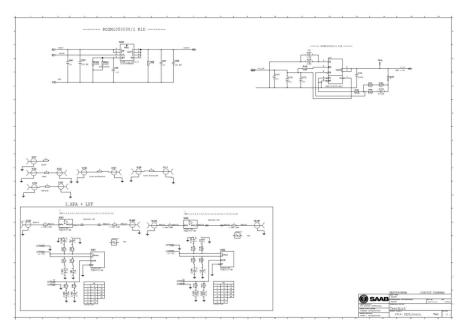

| Figure 21: Evaluation Board Schematic                                                      |          |

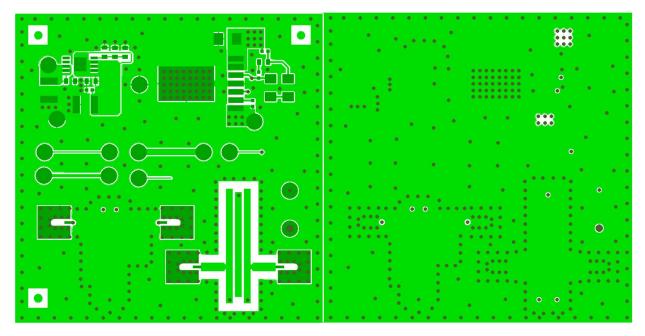

| Figure 22: LH Coin layout board 1; RH Top solder mask board 1                              |          |

| Figure 23: LH Layer 1 board 1; RH Layer 2 board 1                                          |          |

| Figure 24: LH Layer 3 board 1; RH Layer 4 board 1                                          | LI       |

| Figure 25: LH Layer 5 board 1; RH Bottom solder mask board 1                               |          |

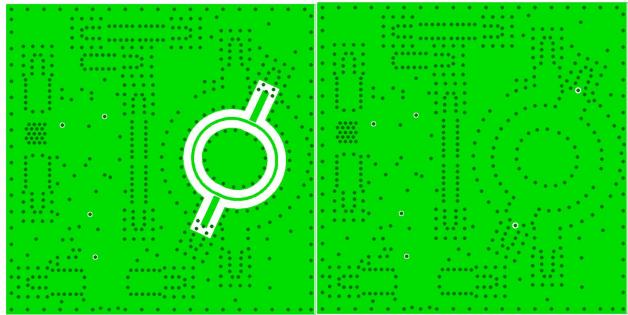

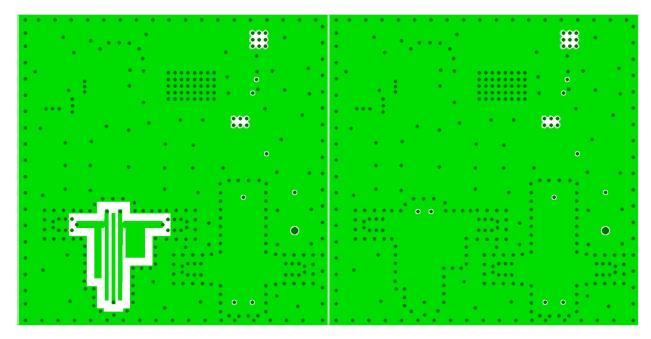

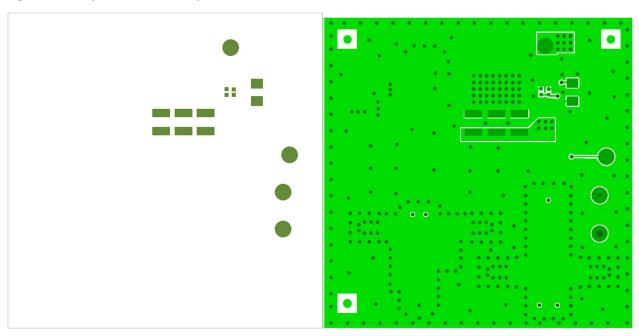

| Figure 26: LH Coin layout board 2; RH Top solder mask board 2                              |          |

| Figure 27: Figure 23: LH Layer 1 board 2; RH Layer 2 board 2                               |          |

| Figure 28: LH Layer 3 board 2; RH Layer 4 board 2                                          |          |

| Figure 29: LH Layer 5 board 2; RH Bottom solder mask board 2                               | LIII     |

## 1.Introduction

The thesis is focused on the possibility of involving manufacturing processes in the development process. It was carried out at Saab AB during 2018 and was done in conjunction with the department of Industrial and Materials Science at Chalmers in frame of the Centre for Additive Manufacturing – Metal (CAM<sup>2</sup>).

## Background

Nearly all not purely mechanic manufactured products incorporate a circuit board in one form or another. Due to the complex structure of these Printed Circuit Boards (PCBs), their development cycle is rather complex resulting in a complex supply chain and long delivery times for manufacturing of the functional prototypes. In many other product areas, implementation of the additive manufacturing technology allows to significantly minimize delivery times that resulted in significantly quicker and cheaper development. However, as PCBs require complex material structure – conductor and dielectric materials printed with high resolution – such a technology was not in place until now.

In addition, due to the complexity of products being developed, companies working with research and development are increasingly faced with a demand for faster development of new products and services. Partly because of shorter product life-cycles but also because of global competition [1].

In order to meet these demands while ensuring quality, companies needs to explore new technologies and continuously work on improving their process. One way to speed up the development is by using simulations instead of physical prototypes. Another is to work on the process and use new tools and technologies [2].

An important part of most technical development projects is the transition from a breadboard to a PCB, both to show function and size. But it also gives an indication of performance and shows progress in a tactile way for developers to help them understand what is happening in the project.

Current processes for PCB manufacturing have a relatively long lead time or are not usable for multilayer applications. A large part of the lead time comes from waiting for deliveries from external manufacturers both for components but also boards. Even when external manufacturers can deliver products quickly, the act of sending intellectual property to external partners carries a risk for the company. Internal manufacture with alternative methods is seldom an option due to the process expertise and production volumes needed to economically make it an acceptable alternative.

Recent development in binder jetting technology allowed Nano Dimension Ltd, to develop a platform that allows the printing of advanced conductive and dielectric inks for manufacturing of high-performance multi-layer PCB prototypes. The first systems were delivered in the late summer of 2017 and machine has a build volume of 200\*200\*3 mm.

As it is the first additive manufacturing technology on the market when it comes to manufacturing of circuit boards, evaluation of the technology potential for novel design possibilities and

development of new products, possibilities and limitations of the technology and properties of the 3D printed PCBs are of crucial importance [3].

The usage of an additive process for PCB manufacturing might allow for novel design solutions and can most likely be used to reduce the time of prototyping in development of new designs. For example, if PCB boards manufactured by additive are viable, and does only require more time and material for extra layers and complex structures like copper coins and buried VIAs, then it gives complexity without adding additional costs from special manufacturing steps. It also enables inhouse prototyping of complex boards with minimal spatial and manpower requirements, while protecting intellectual property from outside threats.

Some of the possible improvements in future machines might be to build in capacitors and resistors in the PCB, thus saving space, logistics and assembly costs. Preparing for and knowing when and how to use it gives an advantage in development time and cost. While many evaluations for visual and structural prototyping with additive machines have been carried out, and companies are using them to speed up development projects, to date nothing similar have been done for PCB prototyping.

LPKF have for many years-built prototype equipment for PCB manufacturing, lately they have started to include lasers to achieve tighter tolerances therefor enabling high frequency prototyping. They have also launched an additive process, adding conductive traces to 3D-structures [4]. This makes them a fitting example of alternative prototyping processes compared to Nano Dimensions.

#### Aim

The objective of the Thesis is to evaluate functionality and resulting material properties of the additively manufactured PCB compared to an ordinary production process. The work includes detailed characterization of the 3D printed PCB, characterization of its performance, cost estimation and environmental impact of the process as well as impact on the delivery time.

The objective is to evaluate and compare functionality and resulting material properties, between an additively manufactured PCB compared to an ordinary production process. In addition, the environmental impact of the new AM process, compared to the traditional process is investigated.

Project also aims to identify mechanical and electrical methodologies, to study and carry out material testing in real applications such as digital, power, analogue and high frequency, to analyse strengths and weaknesses regarding performance and durability. This will allow for the study to find how to integrate PCB prototyping in the development process, benchmark future technologies and involve engineers in process development.

Project aims to develop principles, methods and solutions to use the new process in conjunction with the current processes inside development projects taking place in the company, to form a basis for quick and efficient evaluation of processes, leading to informed decisions about new technologies in the future

## Research questions

Research questions that were established before the start of the project:

- a) Technical trends in PCB manufacturing by additive manufacturing

- b) Principles for evaluation of alternative PCB manufacturing processes

- c) Design and manufacturing principles of 3D printed PCBs

- d) Usage of additive manufacturing of PCBs in product development

#### Limitations

The thesis will not include more than one evaluation card per process type, due to time and cost limitations. The reasoning behind is that the variance in the separate processes is smaller than between processes.

Due to time limitations, no full LCA will be conducted, only partial analysis of internal waste in the process and eventual toxic substances handled for the process or created during the process will be considered. This is partly to allow the thesis to be carried out in the timespan allotted, but mainly because these are the points a company aiming to incorporate the processes in-house, will have to consider.

One crucial limitation of the thesis was the limited time and effort spent, by the author, on creating evaluation boards. Focusing on processes and development, board design used was comparably simple. They also partly reused designs developed in other projects to save time.

While products from full scale production lines will be evaluated in the project, the focus will be on prototyping lines and not full-scale production. This is done mainly because the aim of the thesis is to look at processes used for development and not for volume manufacturing.

The rise of the maker movement and the tech start-up trend have resulted in a few alternative additive processes, mainly V-One from Voltera and Squink from BotFactory. These while mentioned in the final report will only be further evaluated in case of time and resources. The focus will be on professional processes resulting in finished PCBs comparable to those from manufacturing processes used for finished products.

# 2. Methodology

This thesis starts with a thorough literature reviews and interviews with subject matter experts to determine status and trends in additive manufacturing, complex electronic components including PCBs, recent PCBs development and manufacture methods.

Thesis compares and investigate how the use of the different methods proposed by Maylour and Wheelwright that sets the foundation of PD (Product Development) education at Chalmers. In combination with how current processes compare to the process proposed in LPD (Lean Product Development) and what parts of the process might benefit from new and alternative production processes.

Evaluations carried out in the thesis are based on the test to failure method from LPD to learn the limits of the different technologies and their applications. Platform and modularization methods like the Contact and Channel method was utilized, to identify and build test systems while maintaining easy to evaluate sub-systems, to save on number of boards while keeping test-features for evaluation.

The project started with looking at as many technologies as possible before grouping them together depending on defining characteristics, to make it easier to compare to each other. This was followed by collecting information about process, materials and use-cases to build a better understanding of the process, to build knowledge to bring to experts at a later stage to set base requirements used evaluating the gathered concepts. Input from stakeholders and lead users was used to refine the requirements during the project, allowing their expertise to fill in the gaps in the available knowledge of the processes.

To conduct the evaluation of new processes, a new method was created by building on existing methods used to evaluate related fields. The proposed method can be found in the theoretical framework in section 4.

## Research approach

Following is a description of how information has been gathered during the thesis and how quality was assured. To guarantee the quality of sources used in the project the aim has been to only use the following type of material:

- Work published by government agencies such as NASA (National Aeronautics and Space Administration) or universities that disclose partners and sources of funding for the research.

- Articles published in credible journals after being reviewed and that have been cited in other works, lecture material and course literature from relevant courses at Chalmers University.

- Interviews with Lead-Users and experts from the industry conducted after informing them of the intended use of the information, and when the interview have been conducted a transcript has been sent to the interviewed person for review. This is to allow for correction of misunderstandings and to remove any sensitive information from the documentation.

- Information given by manufacturers will be used as a credited source after verification by testing it or cross referencing it with information given by other manufacturers.

- Finally, all source material used should be written in English and be easily accessible to allow for inspection and review of cited material.

First when no source filling these criteria was available, other sources have been used, and then only for minor parts of the thesis. When information must be gathered outside of literature available, a qualitative approach has been used since the time and resources are too limited for a quantitative study.

#### Ethics and environmental concerns

During an evaluation about using a new production process, it would be unacceptable to not investigate health and environmental aspects and how it will affect the operators and those around it. During the duration of a thesis it can only be done to a limited amount, but it is something I have taken into account whenever it was possible.

#### Ethics when it comes to methods and evaluations

It is interesting to reflect over the ethics of looking into ways for a defence company to work more efficiently, when developing new products. But the core of the thesis is to make all development more efficient, hopefully leading to better products but primarily less wasted resources. The more efficient the process, the larger amount of good can be done with a set amount of resources.

Putting my trust into humanity to work towards a better more sustainable future, I am only looking into how to evaluate and utilize new technology to reach there faster with less waste on the way.

One primary focus during the thesis have been to look at everyone involved and affected by the process to identify risks to health or environment. Things like harmful substances, work environment, waste and potential bodily harm, have been investigated and considered during the course of the thesis.

As a guide the IEEE code of ethics [5], have been used, especially the following paragraphs:

- **§1:** "to accept responsibility in making decisions consistent with the safety, health, and welfare of the public, and to disclose promptly factors that might endanger the public or the environment."

- **§3:** "to be honest and realistic in stating claims or estimates based on available data."

- **§5:** "to improve the understanding of technology, its appropriate application, and potential consequences."

This has been used as the basis for the considerations done and the decisions taken during the project.

#### Environmental concerns as part of thesis work

As stated in the introduction, no full LCA was carried out to look at the environmental impact of using any of the processes. What was done is looking at available studies of health and environmental impacts from the materials, also, what hazards and concerns stated in the material declarations are available.

## 3. Theoretical framework

This thesis and report have been carried out at a high-tech company that develops new products using the latest technologies, this sets requirements at a higher level compared to a more midtech company.

Without a basic understanding of what a PCB is, how a circuit is developed, and which manufacturing methods are used to produce PCBs, it is impossible to follow the practical part of the evaluation. Hence the DRL method should also be usable for evaluating processes that are not geared towards manufacturing electronical products and should be understandable on its own.

## Evaluation and rating methods

The problem of including new technologies and processes in a development project is that evaluation and rating methods focus on a finished product built on or with a new technology, not for usage within a part of a development project. To conduct the thesis, it became paramount to create a method that does this.

Before trying to create a new method, it was needed to build knowledge on available methods and how they are used. It was also decided that it would build on and include parts from established methods but try to create something useful for the specific case. One restriction, set to ensure quality is that all methods need to be tried, tested and recognised by companies around the globe that uses them. When this was found to be true, the methods were considered for use during the thesis. Following is a short description of the methods evaluated and used during this thesis.

#### **Technological Readiness Level (TRL)**

Launching a large project based on a promising new technology that at a later stage is found to not work as intended or fail to deliver the required performance, can lead to expensive redesign of a product in the later stages of development. If the technology shows to be unsuitable enough it can also lead to delays, sub-par performance or even cancelation of the project.

To reduce the likelihood of such a situation NASA developed the TRL method [6], it is a rating system that aims to allow for comparison between different technologies while helping with keeping track of progress. Used by both NASA and DARPA (Defence Advanced Research Projects Agency) to help with decisions regarding the inclusion of a new technology in a project or to start a project based on a new technology.

Following is the different levels as defined in Mankins white paper, with a short description of what should be reached to fulfil the requirements for that level [6].

- **TRL 1:** The most basic of principles observed and reported, this can be as simple as material properties. Scientific studies are transferred into applied research.

- **TRL 2:** Formulation of possible applications for the technology, it can still be speculative concepts of use with no supportive evidence but the possibility of using a certain property in an application needs to be there.

- **TRL 3:** At level 3 analytical and experimental proof of critical function or proof of concept are needed.

- **TRL 4:** Level 4 is proving functionality in a laboratory, either on a component level or a basic PCB/Breadboard.

- **TRL 5:** TRL 5 builds on level 4 with moving the system to the real/representative environment with relevant support elements.

- **TRL 6:** A representative prototype system tested in a representative environment.

- **TRL 7:** To reach TRL 7 a prototype needs to be tested with or near the planned system that will be used in conjunction with the prototype.

- **TRL 8:** At TRL 8 the system should function in the final system during expected conditions.

- **TRL 9:** A technology reaches level 9 when it has proven full functionality when being used for its final function at operational conditions.

While called levels, the different stages of TRL can be seen as milestones for development of a new technology, because a technology will be at a certain level first when it fulfils all demands for that level.

Using TRL in practise means that the levels must be represented with actual requirements corresponding to the field of technology and the planned usage of the technology. The newer and more novel the technology is, the stricter the adherence to the method and the higher the requirements will be set.

However, as stated in the recommendations of the CECOM (U.S. Army Communications-Electronics Command) report [7]: "Much of the value of TRLs comes from the discussion between the stakeholders that go into negotiating the TRL value."

By sitting down with relevant stakeholders to discuss and negotiate the readiness level, it becomes a communication tool that hope to lead to a common understanding of the technology while removing personal biases from affecting the requirements and the perceived readiness.

#### **Manufacturing Readiness Level (MRL)**

Some spectacular failures have resulted from developing a product around a manufacturing process that is not ready for use. A situation that often arises from using immature or misunderstood manufacturing methods is the need to redesign the initial design late in the project to accommodate the usage of an alternative manufacturing method.

One example of a company struggling with having developed a product for a manufacturing technology that wasn't ready is Intel. Intel has been working on a manufacturing method that can create transistors on the 10nm scale since before 2014 when they released their 14nm based processors. They planned to release a processor built using that method as early as 2016, delays lead to an initial release during 2018 with scale production planned for 2019 [8] [9].

Manufacturing Readiness Levels was developed partly to reduce the risk of something like that happening but also to serve as a compliment to TRL. Since MRL is meant to complement the TRL method, MRL 1-9 can only be reached if the technology is on the corresponding TRL [10].

MRL was developed by Department of Defence (DoD) and is used extensively by NASA, DoD and DARPA to prevent the starting of a project that plans to use a manufacturing method that hasn't shown to be capable enough. Therefore, reducing the risk of delays due to redesign or even scraping of the project if the manufacturing technology fails to deliver [7].

MRL is a substantial framework for evaluating manufacturing methods. To fully represent MRL in an understandable way would take the majority of this report, hence the following is the MRL definitions as laid out in the MRL handbook released by the DoD [10].

#### **MRL 1: Feasibility Assessment**

Studies and laboratory work show a feasible concept.

#### **MRL 2: Concept Defined**

Identified concept shows capability of building a prototype part.

#### MRL 3: Proof of Concept Developed

Basic validation of the manufacturing technology, materials and processes have been characterized.

#### **MRL 4: Laboratory Demonstration**

Process assessed in laboratory with plans to deal with identified deficiencies, cost driving parameters found and realistic cost approximation for further development set.

#### **MRL 5: Process Development**

Enabling or critical technologies have been identified, process sequences identified, inspection, tooling and strategy procedures identified and are in development. Performance is demonstrated in production relevant environment.

#### MRL 6: Functional system or sub-system producing in process environment

Critical systems have been produced and tested in planned process environment. Testing carried out on a pilot line demonstrating function and giving insights into yield, reliability and costs.

#### MRL 7: System or subsystem production

On this level the focus is on proving the capability and initialising the six-sigma process. A plan should be in place to reach full production with targets and tracking for process parameters. Work on optimization and cost reduction should be on the way.

#### **MRL 8: Pilot line production**

Low Rate Initial Production (LRIP) ready process that is controlled to 3-Sigma, is established and data from test runs is used to update cost models and the yield analysis.

#### MRL 9: Proven process producing products

To reach level 9 the process must be proven to function fully at a low rate and be ready to scale up to high rate production. During the low rate production, it must be controlled to 6-Sigma standard or equalling rating system.

#### MRL 10: Lean production implemented on full scale production line

Proven process with well-developed Lean production practices. Development is limited to cost reduction and quality improvement measures.

#### **Manufacturing Capability Readiness Level (MCRL)**

MCRL Manufacturing Capability Readiness Level is developed by Rolls-Royce to introduce a new manufacturing technology at later stages of a product lifecycle to move production to the new process [11].

MCRL is divided into three phases and nine levels, what follows is a short description of both phases and levels according to a report published by Rolls-Royce in 2011 [11].

#### Phase 1

Assessment and evaluation to show function, proving the basis of the technology and includes level 1 - 4.

MCRL 1: Concept proposal

MCRL 2: Validity demonstrated

**MCRL 3**: Proof of concept

MCRL 4: Laboratory validation

#### Phase 2

Preproduction consist of levels 5-6 and is focused on creating an operational production line.

**MCRL 5**: Functional production on the equipment

**MCRL 6**: Process optimization for maximum production rate

#### Phase 3

Start of production contains level 7 – 9 and is the introduction of the technology into actual production.

**MCRL 7**: Builds on level 6 but requires sustainable production with economic output and with no major changes to the process.

MCRL 8: Ramp up to volume production

**MCRL 9**: Volume production with extended production runs, all requirements needs to be meet and the manufacturing technology is ready for full scale use.

#### Risk Management (RM)

During a project or around a business there will always be risks. Managing those risks is important to ensure both a safe conduct, but also the continued profitability of the organisation. Risk is often considered something more physical like an accident or a fire. Risk in a business consists of many aspects. The risk of missing out or to be left behind is one of the driving factors behind this study and a risk that often is overlooked.

Including new manufacturing processes or new technologies in a project is a risk. To manage this, risk management was introduced as a tool included in business planning. Following is how risk management is defined by NASA in the Risk Management Handbook [12].

#### $RM \equiv RIDM + CRM$

As stated in the Risk Management Handbook by NASA, "Risk Management as the Interaction of Risk-Informed Decision Making and Continuous Risk Management"

To work with RM, a continuous work with both Risk-Informed Decision Making (RIDM) and Continuous Risk Management (CRM) is needed, were one goes into the other in a never-ending loop. But to do this and still be effective in moving the project forward, is where the challenge begins. Following is how RIDM is defined by NASA in the Risk Management Handbook [12].

#### Risk Informed Decision Making (RIDM)

#### Part 1: Identification of Alternatives

Find and identify alternative solutions and opportunities.

#### Part 2: Risk Analysis of Alternatives

Analyse the risks of the different alternatives as part of setting up the technical requirements.

#### Part 3: Risk-Informed Alternative Selection

Evaluate alternatives according to risk and reward followed by selection of the best alternative after careful deliberation.

#### Continuous Risk Management (CRM)

#### **Step 1:** Identify

Identifying and capturing risks is done by finding perceived risks the stakeholders have and collecting those with their conditions in a database.

#### Step 2: Analyse

Analysing the risks collected into the database with focus on how likely they are and what ramifications will follow. This is done to rank the risks against each other to allow focus to be put on the most imminent and critical risks first.

#### Step 3: Plan

Setting up a plan for how to handle and mitigate the different risks going forward in the project. There are five categories of actions that can be taken in the planning stage and those are: **Accept** the risk, work actively to **Mitigate** the risk, **Watch** the risk continuously, continue **Research** into the risk, **Elevate** the risk to a higher threat level or deem it unimportant and **Close** the risk file.

#### **Step 4:** Track

Risks are not static, and the tracking face is used to continuously look for how the work with risk management is going and to re-evaluate the risks being monitored. This can be reclassifications of old risks and introduction of new.

#### Step 5: Control

Should the tracking step indicate that the work with mitigating a risk isn't performing within an acceptable level the control step includes actions to assure that the planned action is successful. This can be extra resources or moving it to people with higher permissions. After a control action a risk will need to be reevaluated on the planning stage to better handle it in the future.

All steps and actions depend on proper communication between all involved stakeholders and documentation of the steps, plans and actions.

One of the most important things to understand with risk management, is that in order to move forward, a business needs to find acceptable risk levels for operation and go forth, while doing the best they can to systematically mitigate the possible fallout. To not take any risks at all, leads to stagnation and obsolescence and that is a risk to the entire organisation. In the introduction to this report the risk related to being behind in development processes was mentioned as a prime example of why investigating and evaluating new technologies and processes was important to be competitive.

To summarise this chapter, it is important to emphasize that the risks associated with being left behind needs to be balanced with the risk associated with being in the forefront of technology. This should be done while working with minimising the fallout of an accident and the chances of one occurring.

#### Summary and conclusion on available evaluation methods

The problem of including new processes or technologies into a new project is something that has been studied a lot and methods to mitigate the risks are already developed and tested. The problem for both TRL and MRL, are that focus have been on having a new technology in the final product or use a new method for producing a product and not looking at including it at a stage of the process while having the option of leaving it in or out of the final product. MCRL investigates replacing an existing process for an existing product using the foundation and thinking of MRL. Risk assessment has been built around this and can be used to mitigate the risks that come from using an unfamiliar technology or method in a project.

The lack of a process for evaluating manufacturing processes for usage in development projects lead to the combination of method to show TRL during a project, it is described in the **Development Readiness Level (DRL)** chapter.

## Development process and workflow

A short summary of a few product development processes and how they work with prototypes.

### **Agile Development and Scrum**

Since many companies have started working with Agile methods for product development outside of programming, it becomes interesting to see the difference between the different fields that is programming, mechanical and electrical development. Developed for programming projects and workflows, Scrum focuses on short cycles or sprints to rapidly create core functionality that can be tested and verified, creating the basic functions while programming and going from there to create a final program only containing what the customer needs [13].

Scrum is built around Scrum Teams working in Sprints to complete tasks in the product backlog. The Team is built around three roles while the process has five main steps. Following is the three roles in a Scrum Team and the five main steps of the process according to Jeff Sutherland's Scrum Handbook [13]:

#### **Scrum Team**

#### 1: Product Owner

The Product Owners role is to identify product features that the customer wants and prioritize among them, so the Team can work on the most important features. Interactions between product owner and the Team is personal were the Product Owner looks at the progress of the sprint and relays the most important features to the Team. Prioritising and deciding on features are solely the domain of the Product owner.

#### 2: Team Members

The Team is a cross functional and self-organising team consisting of between five and nine persons. Developing the features prioritised by the Product Owner by dividing it into tasks and committing to solve those tasks within each sprint.

The Team does its own testing to build knowledge on what works and how to improve the product.

#### 3: Scrum Master

The Scrum Master serves the Team and works to provide whatever the Team needs to succeed in their task. One additional task is being the layer between the Team and distractions like the Product Owner wanting to swap some prioritized features during a Sprint.

#### **Scrum Process**

#### 1: Product Backlog

The Product Backlog is created and maintained by the Product Owner. It can contain a multitude of tasks from solving a problem and creating a feature to research and correcting an old mistake. The Product Owners role is to identify product features that the customer wants and prioritize among them, so the Team can work on the most important features in the Sprint.

#### 2: Sprint

A Sprint is a work period of between one to four weeks within which the Team does the development work with no alterations to the Backlog. Team members commit to solve tasks and works towards completing the backlog during the set time period.

#### 3: Sprint Planning

At the start of a Sprint there is a first Sprint meeting, it involves everyone in the Sprint team, the Scrum master and the Product owner. In the first meeting the features in the Backlog are discussed with a focus on their context and requirements. Then the Scrum Team selects a few features they commit to complete during the Sprint. Following the first meeting is a second meeting were the selected features are divided into tasks to be completed.

#### 4: Daily Scrum Meeting

During the duration of the Sprint the Scrum Team has a daily meeting to update each other on the current situation. The meeting is done standing up and should not take more than fifteen minutes.

#### 5: Sprint Review and Retrospective

Following a completed sprint, the completed features are committed and presented to the Product Owner during a Sprint Review. During this review the Team and the Product Owner discuss what have been done and what's next. After the review the Team gathers for a Sprint Retrospective to go through what have worked during the Sprint and what needs improvement before the next Sprint.

Even if Scrum started out as a development process for programming, today Scrum is used for entire development projects. This demands collaboration between disciplines in teams tasked with delivering something to test or to test on after a short sprint. It is easy to build and test code using simulations, evaluation boards or even on the final system.

However rapidly delivering iterative prototypes of mechanical systems takes longer time since the computer designed and simulated parts needs to be manufactured before testing. Comparing the time, it takes to compile some code for testing, to manufacture components by 3D-Printing polymers or metallic for testing, the time needed for the latter is significantly larger. Even if 3D-printing mechanical structures allows for quick or rapid manufacturing of mechanical prototypes it functions on timescales of hours, not minutes like the compiling software. Add to that the need for assembly and cost inherent to additive manufacturing, and the mismatch between the two becomes apparent.

Electrical prototyping is in many cases the link between programming and mechanical engineering, making a system a functioning mechatronic component. The big difference between making electric prototypes and mechanical ones, is the need for special components with lead times, add to that the time it takes for a PCB to be manufactured and delivered and it can take even longer time to iterate an electrical prototype compared to a mechanical.

The core idea of Sprint is to rapidly develop something and then test it, to learn from it before doing another iteration to add extra features. This requires a rapid prototyping approach to keep within the mandated Sprint cycles.

### Lean Product Development (LPD)

Lean Product Development is a development method developed by Toyota. The foundation of the method was built on the way the Wright brothers developed the first airplane and today it has become one of the dominating methods when it comes to product development.

Lean is often described as a toolbox, and both the tools and the usages vary between different companies. In this thesis the focus has been on how and why it was implemented at Goodyear and Harley Davidson. Their available material has been used as the primary sources of information about the methods. Further focus was put into Knowledge based product development, The Swirl Model, set based development, Trade of curves and the Test to Failure method. Following is a short description of the parts of these methods and tools used in this thesis.

Knowledge based product development is an adaptation of Lean done by Harley Davidson, where the goal is to find the best alternative to develop further. This is done by gathering knowledge from many different possibilities in a process called "concurrent engineering". This leads to the final decision to what will serve as the final solution being postponed until enough knowledge is gathered [14]. The reason this is important is that at the beginning of a development cycle a lot is unknown, both about the technologies but also the market and what the customers' demands. Hedging your bets instead of going all in on one solution until you have a clear indication of what will be the winning solution.

Using an LPD method for testing called Test to Failure [14]. In contrast to Test to Specification, Test to Failure searches for the point when something breaks or fails to fulfil its purpose. This means that each test is more extensive and therefore more expensive, but should the requirements change and therefor the specifications, no new tests need to be conducted. Testing to Failure have the data for the possible design space readily available while a new test to Specification will be needed to attain that knowledge [14].

The Test to Failure approach goes into the Test Design Build (TDB) cycle of LPD and Test Learn Build (TLB) cycle of Norbert Majerus. Both focus on start with testing to learn what you don't know before starting on any design work [15]. This contrasts with the older standard Design Build Test (DBT) cycle used in many development methods.

One example of the difference between Test to Failure and test to Specification used by Harley Davidson [14], is testing an engine with fuel containing 30% ethanol because of Brazilian regulations allow for that specific mixture, compared to running a full test series mapping the range between 0% and 100% ethanol. This would give knowledge no matter the ethanol content of the market, without additional testing. This is often used in conjunction with Trade of curves that is a tool to visualise the available design space and trade-offs between different solutions. Plotting them in a dual axis graph is done to show how they compare depending on two attributes.

One description of how ideas and suggestions transition from a simple idea to a project or change in the organisation is the Swirl model. In the Swirl model ideas, concerns and possible solutions exist in a Swirl. Inside of the Swirl they are discussed and debated before fading away or rising towards the top. This process can take years but when they raise through the Swirl, they are both in the awareness of the organisation and driven by an individual or group that believes in it and wants to carry it further. At this stage, the idea needs to pass a filter made by upper management. Nothing should come as a surprise to management and any suggestion reaching the filter stage

should be well thought out with answers to questions to why they are needed and what the root cause of the problem is [14].

Waste is a common theme when it comes to Lean but instead of focusing on wasted movements, etc. LPD focuses on wasted ideas, knowledge and time. Not using the full capability of all employees is a huge waste when it comes to an organisation's human capital. According to Norbert Majerus there is a core group of inventors in a successful R&D organisation that interacts with each other and stands for a disproportionally large part of all development within an organisation. One additional observation was that identified inventors need to have the possibility to invent or they will regress to a similar output as an average employee [15].

Waiting is the largest of the eight wastes in research and development and often there is no cost associated with it. To put a cost on waiting time Goodyear introduced Cost of Delay (COD) as a measure to translate waiting time into a cost in dollars. When looking at waiting as a cost and being able to compare it to the investments needed to reduce the waiting time, the problem becomes easier to confront and solve [15].

One additional waste is the reinventing the wheel that is done due to forgotten knowledge. It can be knowledge leaving with employees when they leave the organisation or hidden in a cumbersome data management system that makes it easier to relearn than finding it again.

## 4. Development Readiness Level (DRL)

Looking at the evaluation methods available for analysing new technology and manufacturing methods, it is clear that they focus on including new technology in projects only when they are fully developed and are considered for final production.

Unless the technology evaluated for adaption into the development process is developed in-house, any new technology will be at one of the higher levels of TRL when it is made available for the development team.

Implementing MRL and using the process with all its stages and steps designed for the DoD and projects on the cutting edge of technology, is a monumental task. If it can be scaled down to fit to the size and complexity of the situation, it becomes useful even for evaluating technology for inclusion in the development process. This is similar to, what happened when MCRL was developed to facilitate the move from one manufacturing technology to another, but instead of moving the finalised product between technologies it looks at how different technologies can be used at different stages of development.

Combining parts from the different methods to make a method to use both during the thesis and as a proposed method for continuously evaluating new manufacturing technology in the future. This was done following the knowledge-based product development core idea, that instead of early putting all money into developing one idea that seems to be the most promising. Spend some money on investigating many ideas and commit to one idea only when you know it will work.

#### **Definitions**

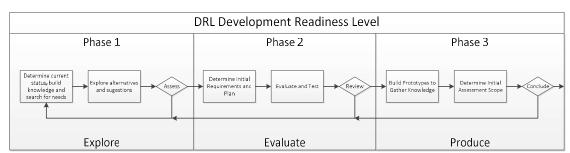

Like in the MCRL method there are three phases of DRL, they are shown in Figure 1 as an iterative stage gate process. DRL tries to involve people in searching, testing and evaluating so their ideas, knowledge and experience can be used to help guide the company forward.

Figure 1: General overview of the proposed DRL method

The advancement along the levels can be seen as a climb up a ladder and building on the Lean philosophy. The climb up the ladder should be communicated to and with all affected parts of the organisation.

**Phase 1 - Explore**: The goal of phase 1 is to identify needs and possible solutions, it can be seen as a pre-study. With the final aim of only going forward with technologies showing a great deal of promise for expanding the capability of the organisation.

However, it needs to be stated that the amount of information needed varies with the goal. To start phase 2 with the goal of reaching DRL 6, it starts when a possible solution being assessed show promise of reaching MCRL 7. While if the needs correspond to DRL 5 it can start when a process have reached MCRL 5.

Phase 1 should be part of the work with continues improvements within the organisation and people should be able to partake while continuing their ordinary tasks. It is a continuous and iterative phase that builds on learnings from earlier projects and iterations, it does not need any specific source but should be done by everyone in an organisation.

In a way Phase 1 is operating as the funnel in the product development process proposed by Ulrich & Eppinger in the way that it gathers information from a wide pool of knowledge within and outside the organisation and funnels it towards a decision point [16].

The entirety of phase 1 and the first level of phase 2 is also a formalisation of the Swirl model with the gate moved to an earlier stage.

**Level 1:** is reached after evaluation of existing needs found after looking at work flow and asking people working at different stages what they think is bottlenecking the process. When the status is known and measured then it is time to explore alternatives on how it can be solved.

**Level 2:** Level 2 is the process of searching for possible solutions to investigate further. It can be seen as reached after alternative solutions to the problems and discrepancies identified in level one has been found and thoroughly discussed between different stakeholders.

**Assess Gate:** Up until this point a low amount of time, effort and resources should have been put into both looking at the problem and for finding possible solutions. To get past the gate a clear and concise picture of the problem with the reasons why it exists and why it is a problem needs to be presented, together with a simple plan for time and resources needed to conduct phase 2.

**Phase 2 - Evaluate**: Phase 2 begins when management think that a technology shows enough promise to be investigated further. To get to this stage will often need a sponsor since now personnel work actively on evaluating the technology, this means that it will use resources that could have been spent on other projects. The focus of phase 2 is like in phase 1 about finding information, but now the effort is done actively with a budget, set goals and the aim of delivering a report for evaluation at the review gate.

**Level 3:** Finding the requirements needed to assess a technology can be as tricky as discovering the need for change. By finding stakeholders and experts the usage of focus groups or other tools can use the experience to set objective requirements and details for evaluation.

One way to find requirements and gaps in knowledge of a process is to reuse requirements from real stages in the process but only if they correspond to something real and quantifiable.

Reach out to process owners to gather what data can be found without investment and survey the possibilities for testing.

**Level 4:** Level 4 is the stage when the technology starts to be tested in a more practical way. What needs to be evaluated and possible ways to do it should be set at level 3 but there is the possibility to adapt the evaluation to changing circumstances. Test on hardware, according to the test to failure philosophy to gather the needed knowledge. This is done to get a good measure of how the technology corresponds to TRL and MRL but primarily to see the limits and how they correspond to the set requirements. After testing the results needs to be review and presented to the stakeholders to either be passed to the review gate or iterated on. This process of test, review, and redesign should continue until enough knowledge have been accumulated and builds on the test, learn, and build cycle of Norbert Majerus.

**Review Gate:** To pass the review gate the technology needs to be well understood with few or no unknown properties, it should also show a real promise to improve the internal development process.

Alternative outcomes are halting of the evaluation process or a restart at a previous level. The important part is that knowledge is shared and stored in a usable way. Should the technology pass the review gate the next step is to acquire access to the technology to allow for development teams to make use of the technology.

**Phase 3 - Produce**: Phase 3 begins when a new technology has been introduced to an organisation and has started to be used for prototyping by development teams.

**Level 5:** means that the process can be used to produce prototypes for at least TRL 4 verification and should be made accessible for development teams to build knowledge and evaluate the technology further. At this stage development teams needs to be made aware of the new technology, the limitations and advantages. Active encouragement might be needed for the teams to use the technology in order to continue building knowledge to allow for further advancement of the process.

**Level 6:** is reached when the process has shown MRL 8 and the process can be used to manufacture subsystems for the final product in a relevant production process. At level 5 a sufficient knowledge base should have been built to quickly do an MCRL and MRL evaluation to use the new process in conjunction with or to supersede the old process. Findings should be summarised and presented to management to decide on future implementation.

**Concluding Gate:** Borrowing from Scrum and other iterative cycles the conclusion is reached when the project is done, it is used to evaluate the process and how the project was carried out. This is the stage when the people involved in the process come together and try to find what went wrong, well and how it can be improved for the next time. It also the stage when a report for upper management is finalised and when the project with its findings is presented to the organisation. The report should not come as a surprise to

management and all stakeholders need to have been involved in the process to build awareness and support.

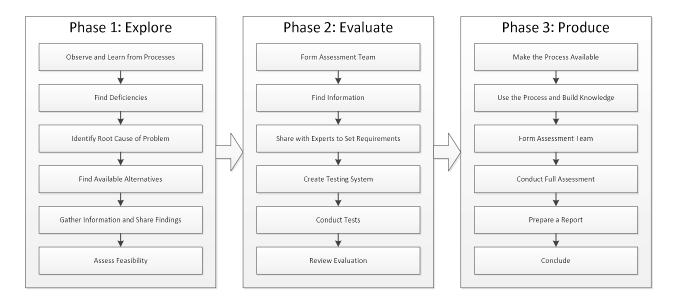

# Usage of the DRL method

Using the DRL method before and during the beginning of the thesis that would correspond to Phase 1 was not an option since the method came about during the thesis. However, the process leading up to the thesis resembles Phase 1. A second note is that the thesis only conducts the first iteration of phase 2 not including the review gate, leaving further iterations and phase 3 unexplored.

Figure 2: Detailed overview of the different stages of the proposed DRL method

Following parts of the project follows the proposed DRL process and can be seen in an alternative form in Figure 2.

# Evaluation of PCB prototyping methods and their materials

Even if Phase 1 of the proposed DRL method was conducted and approved before the beginning of the thesis, a short summary of the most interesting, of the identified manufacturing methods will be presented, followed by the materials used and implications of how those materials affect health and environment.

# Manufacturing methods

During the beginning of the thesis several possible manufacturing methods were briefly examined. Following is a brief description of the methods and the technology that goes into them.

### **Material jetting**

In material jetting both conductive and nonconductive Inks are used to build a multilayer PCB layer by layer. The chosen manufacturing method used as an example of material jetting is the Dragonfly 2020 Pro produced by Nano Dimensions [3]. Following is the specifications and technologies specific to the Nano Dimensions printer.

Figure 3: Dragonfly 2020 Pro Internal Layout

Internal core components of note, when it comes to the Dragonfly are the Print-Head assembly and the photonic light source. These are the components that in combination with special materials make the printing of a PCB possible.

The heated Build plate moves back and forth below the print heads to allow for material deposition before entering under photonic light source allowing for photonic exposure, partly sintering the silver and curing the polymer. This is done by exposing the materials to short burst of a certain wavelength of light causing the solvent to evaporate and the Nano material to sinter [17].

The Print-Head assembly consist of two sets of Print-Heads, jetting both the conductive and the nonconductive Ink needed to build a multilayer PCB.

Figure 4: Model of a piezoelectric printing nozzle

The Print-Heads build on piezoelectric printing nozzles that eject a droplet on command by operating the membrane on the Piezo element. This is the same principle that is used in Piezo Drop on Demand inkjet printing which is widely used in computer printers.

The Print-Head assembly deposit one layer of material on the print bed that continues in below the photonic light source, were the inks are cured creating one solid layer.

#### **Etching**

Following is a short summary of the etching process for manually manufacturing PCBs as described by MEGA Electronics, it is slightly different from a full-scale production line but builds on the same principles [18].

Etching is done on laminates with conductive material sandwiching a substrate, often with a photo resist pre-applied. For simplification the process of etching copper will be used as an example.

After designing the layout, a negative need to be created. The negative is used to transfer the layout to the laminate by using an UV exposure unit and either harden or break down the photo resist on the board.

After exposure the board needs to be immersed in developer fluid to remove unwanted photo resist and allow the etching fluid access to etch away unwanted copper.

Etching fluid, normally Ferric Chloride is used to etch away the copper using the following chemical reactions:

$$FeCl_3 + Cu \rightarrow FeCl_2 + CuCl$$

$FeCl_3 + CuCl \rightarrow FeCl_2 + CuCl_2$

This process leaves Ferric Chloride, Ferrous Sulphate, Cuprous Chloride and Copper Chloride as waste products from the etching process. These chemicals need to be sent to a waste treatment facility.

After etching the board needs to be rinsed and leftover photoresist removed by a cleaning process and any eventual holes needs to be drilled. The drilling process does as in milling release particles from the board and the substrate that might need to be filtered.

For more than two layers, boards are stacked on top of each other with pre-fab materials in between before being pressed together while applying heat. Additional steps for VIAs to connect the different boards are also needed.

#### **TFT Circuits**

TFT circuits are made by printing conductive Nano silver traces on a thin film that in many cases are made of PET to create the layout on the thin film before photonic curing is used to sinter those traces leaving a functional circuit. Additional steps to add semi-conductive layers can be done to print entire assemblies [19].

# **External manufacturing**

Instead of using an internal resource for manufacturing, it is possible to use an external supplier. Using an external supplier to manufacture evaluation circuits gives access to all previously mentioned methods and even full-scale production lines. Advantage of using this approach is that, having focused on what they are good at, leads to mastery of their techniques.

One alternative to have an internal prototyping line is to work closer with a PCB manufacturer This method is in many cases recommended, especially in the supply network of Lean Production, since it lets experienced suppliers make small series of the prototype with the same material and manufacturing method of the final product.

Production line at PCB manufacturers vary in capability and quality, but what these lines have in common is the size and need for skilled workers. Then again, the supplier of prototyping board does not have to be the same supplier as the one that produce the final product, even if using the same supplier allows for prototyping using the same manufacturing technique as the final product. However, involving an external supplier adds some things to consider such as working conditions at the supplier and waste disposal.

The risk associated with using an external manufacturer is connected to the loss of control over intellectual properties and the risk that comes from sending vital information about products in development to another party.

#### Summary and selection of method for further evaluation

Production size, both in actual board size and in numbers limits what methods are applicable for different projects. The prototyping lines and machines considered in the study have a relatively small maximum board size compared to full scale production facilities.

When it comes to volume production, of circuit boards running on the prototyping lines, is not an option and here comes an important question for the end of phase 1: Will it only be usable for small scale production, like prototypes or can it be usable for serial production?

Even if a process only is usable for small scale prototypes, it is a step up from not having any process for prototyping at all, so it can be advantageous to investigate further. To summarize the initial chapter on manufacturing methods, the method chosen for further evaluation was Nano Dimensions Dragon Fly. This is because the printer produced by Nano Dimensions is the only printer for PCBs available on the market.

# Materials for Additive Manufacturing, their properties, health risks and environmental impact

Additive manufacturing of PCBs is new and to understand the challenges and limitation a basic understanding of the materials used is needed. This is because material properties in conjunction with the process set the technical limitations for the properties of the final board.

In the same way as when it comes to PCBs, it is not only the materials going into the final board, but the materials used during and around manufacturing, needs to be taken into account when evaluating the materials and any possible environmental impact they might have.

## Materials used for additive manufacturing of PCBs

In additive manufacturing the challenge for printing with two or more different materials is that adhesion can suffer if the thermal expansion and curing temperatures are to different. If they do not match, the print will risk failing.

PCBs have conductive and electrically isolating materials. When it comes to printed conductors the most common material is silver in the form of nano-particles that is delivered in paste, powder or Ink form. To prevent particles from clustering together and to ease application while preventing oxidation, additional chemicals are added to the inks and pastes. When it comes to the nano silver ink, a solvent is added to both, keep it from clogging, but also to give it the correct viscosity for printing. It can also be used to prevent particles from spreading in the air. Additionally, the size of the nano-particles affects the melting point and therefore the curing temperature [20].

Figure 5: Melting point of nano-silver particles depending on diameter. Source of data VSParticle [20]

One alternative material for printing the conductive traces is copper, but due to the risk of oxidation in the absence of a protective atmosphere, it will need a protective atmosphere during printing, as stated in the interview with a Nano Dimension Representative [21].

Present literature on photonic curing of nanoparticle silver inks shows that silver nanoparticles have wide spectra absorption rate of almost 90% between 200-800 nm with a noticeable dip to 65% at  $\sim$ 330 nm [22]. It also concludes that photonic curing, most probably is connected to the solid-state sintering processes.

The limiting factor for both conductivity and curing time is the maximum temperature tolerance of the substrate. With higher temperature the curing time goes down and the conductivity increases.

## Health

Considering the health impact of using one technology over another is for the largest part outside the scope of this thesis, but there are some factors that need to be understood when evaluating processes for PCBs that have been investigated.

This is normally part of the risk assessment done before introducing a new process but for simplification of evaluation, only physical health has been investigated, mental health has been left for future evaluations.

## Exposure to harmful substances

Any operator working with traditional methods for producing PCBs will be exposed to the risk of encountering harmful substances. Therefore, it is important to read the material declaration for the material and chemicals used in the process. This should be done to understand the risks involved and put appropriate safety measures into place.

Etching is for example, done using an acid, in many cases ferric chloride. Milling on the other hand, has some risks because the standard substrate, that is called FR4, is a glass-reinforced epoxy laminate. When milling and drilling it is possible that small particles will be released into the local atmosphere and leads to a risk for operators in the vicinity.

When it comes to 3D-printed electronics, the conductor is normally made using nanoparticles of silver. While studies done on rats show no genetic toxicity in the bone marrow in vivo caused by exposure to nano silver, but it indicated that inhaled nanoparticles are systematically distributed in mammalian tissues [23].