UNIVERSITY OF GOTHENBURG

# **Digital Audio Interface Jitter**

Master's thesis in Electrical Engineering

FREDRIK SINKKONEN

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2024

MASTER'S THESIS 2024

**Digital Audio Interface Jitter**

FREDRIK SINKKONEN

UNIVERSITY OF GOTHENBURG

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2024 Digital Audio Interface Jitter FREDRIK SINKKONEN

© FREDRIK SINKKONEN, 2024.

Supervisor: Morten Fjeld, Department of Computer Science and Engineering Examiner: Morten Fjeld, Department of Computer Science and Engineering

Master's Thesis 2024 Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg SE-412 96 Gothenburg Telephone +46 31 772 1000

Typeset in  ${\rm IAT}_{\rm E}{\rm X}$  Gothenburg, Sweden 2024

Digital Audio Interface Jitter FREDRIK SINKKONEN Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg

## Abstract

Jitter is the short-term deviation of a digital signal from its ideal position in time. Some common issues know to produce jitter in currently used digital audio interface formats were examined and multiple implementations of a Universal Serial Bus (USB) audio interface were designed with the intention of creating a device free from interface jitter. Using the three standardized clock synchronization mechanisms in the USB protocol for isochronous transmissions and a selection of suitable clock sources, USB audio class devices were created for which jitter measurements then were performed. The results were compared with jitter audibility thresholds from three studies containing listening tests. While all implementations were functionally acceptable, their jitter results did differ. For the two isochronous synchronization modes of USB that require a continuously adjustable clock source on the receiving side of the interface the jitter issue consists of two parts. Periodic adjustments of the clock signal are in itself a source of jitter and the way in which an adjustable clock source is constructed is another. The initial core idea was that a USB audio interface using isochronous transfers coupled with the asynchronous clock synchronization mode and a fixed frequency clock source would be able to provide an interface in which no additional jitter on top of the inherent jitter level of the source clock would be added by the transfer of data over the interface. The two fixed frequency clocks that were used did however not perform any better than the results of the best adjustable clock source and when they were attached to the test system their jitter levels increased even further. Analysis of the jitter measurements point in the direction of asynchronous mode being preferable for lowest possible jitter levels but the results are not completely unambiguous and jitter levels below the lowest recorded hearing thresholds were also achieved with one of the other synchronization modes for isochronous USB transfers.

Keywords: Asynchronous, Audio, Clock, DAC, Digital, Interface, Jitter, PSoC, S/PDIF, USB.

# Contents

| List of Figures                                                                                                                                                                                                                     |                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| List of Tables                                                                                                                                                                                                                      |                                                                         |

| Terms and Abbreviations x                                                                                                                                                                                                           | xix                                                                     |

| 1 Introduction         1.1 Background and Motivation         1.2 Scope and Delimitations         1.3 Functional Requirements         1.4 Outline                                                                                    | <b>1</b><br>1<br>2<br>2<br>3                                            |

| 2.1.4.1Random Jitter2.1.4.2Periodic Jitter2.1.4.3Data Dependent Jitter2.1.4.3Data Dependent Jitter2.1.4.4Duty Cycle Distortion2.1.4.5Bounded Uncorrelated Jitter2.1.5Audibility of Jitter2.1.5A Theoretical Jitter Audibility Model | <b>5</b><br>5<br>7<br>7<br>10<br>11<br>12<br>12<br>13<br>14<br>14<br>14 |

| <ul> <li>2.2.1 Biphase Mark Code</li></ul>                                                                                                                                                                                          | 20<br>21<br>22<br>24<br>25<br>28<br>29<br>29<br>30<br>31<br>32<br>33    |

|   |                                               | 2.3.5.1 Control Transfers                                                                                                                                                                                                                                                                                                                                  | 33                                                                                                                                 |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 2.3.5.2 Isochronous Transfers                                                                                                                                                                                                                                                                                                                              | 33                                                                                                                                 |

|   |                                               | 2.3.6 Time Units                                                                                                                                                                                                                                                                                                                                           | 34                                                                                                                                 |

|   |                                               | 2.3.7 Bus Access Period                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                 |

|   |                                               | 2.3.8 Endpoint Buffering                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                                 |

|   |                                               | 2.3.9 Prebuffering Delay                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                                 |

|   |                                               | 2.3.10 Transfer of Data                                                                                                                                                                                                                                                                                                                                    | 36                                                                                                                                 |

|   |                                               | 2.3.10.1 Packet Types                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                                 |

|   |                                               | 2.3.10.2 Packet Fields                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                 |

|   |                                               | 2.3.11 Isochronous Synchronization Types                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                 |

|   |                                               | $2.3.11.1$ Synchronous $\ldots$                                                                                                                                                                                                                                                                                                                            | 41                                                                                                                                 |

|   |                                               | $2.3.11.2  \text{Adaptive}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                               | 41                                                                                                                                 |

|   |                                               | 2.3.11.3 Asynchronous                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                                                 |

|   |                                               | 2.3.12 Explicit Feedback                                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                 |

|   |                                               | 2.3.13 The Audio Device Class                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                                 |

|   |                                               | 2.3.13.1 Clocks, Time and Synchronization                                                                                                                                                                                                                                                                                                                  | 43                                                                                                                                 |

|   |                                               | 2.3.13.2 Entities $\ldots$                                                                                                                                                                                                                                                                                                                                 | 44                                                                                                                                 |

|   |                                               | 2.3.13.3 Audio Class Descriptors                                                                                                                                                                                                                                                                                                                           | 44                                                                                                                                 |

|   |                                               | 2.3.13.4 Audio Class Requests                                                                                                                                                                                                                                                                                                                              | 46                                                                                                                                 |

|   |                                               | 2.3.13.5 Audio Class Definition 2.0 $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                             | 46                                                                                                                                 |

|   | 2.4                                           | Inter-IC Sound                                                                                                                                                                                                                                                                                                                                             | 47                                                                                                                                 |

|   | 2.5                                           | Frequency Synthesizers                                                                                                                                                                                                                                                                                                                                     | 48                                                                                                                                 |

|   | 2.6                                           | Fractional Dividers                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                                 |

|   |                                               |                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    |

| 3 | Svs                                           | tem Design and Implementation                                                                                                                                                                                                                                                                                                                              | 51                                                                                                                                 |

| 3 | -                                             | tem Design and Implementation<br>Hardware Selection                                                                                                                                                                                                                                                                                                        | <b>51</b><br>51                                                                                                                    |

| 3 | 3.1                                           | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | 51                                                                                                                                 |

| 3 | -                                             | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51\\52$                                                                                                                           |

| 3 | 3.1                                           | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation                                                                                                                                                                                                                                                                               | 51<br>52<br>52                                                                                                                     |

| 3 | 3.1<br>3.2                                    | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock System                                                                                                                                                                                                                                                     | 51<br>52<br>52<br>52                                                                                                               |

| 3 | 3.1                                           | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation                                                                                                                                                                                                                                       | 51<br>52<br>52<br>52<br>54                                                                                                         |

| 3 | 3.1<br>3.2                                    | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54$                                                                                           |

| 3 | 3.1<br>3.2                                    | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 $                                                                                          |

| 3 | 3.1<br>3.2                                    | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation3.3.3Adaptive Mode Implementation                                                                                                                                        | $51 \\ 52 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54$                                                                                           |

| 3 | 3.1<br>3.2                                    | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62$                                                                                     |

| 3 | 3.1<br>3.2<br>3.3                             | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation3.3.3Adaptive Mode Implementation                                                                                                                                        | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62$                                                                                     |

|   | 3.1<br>3.2<br>3.3                             | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation3.3.3Adaptive Mode Implementation3.3.4Synchronous Mode Implementation                                                                                                    | 51<br>52<br>52<br>52<br>54<br>54<br>54<br>57<br>62<br>67<br><b>71</b><br>71                                                        |

|   | 3.1<br>3.2<br>3.3<br>Res                      | Hardware SelectionDevelopment Environment3.2.1Monitoring of Device Operation3.2.2The PSoC Clock SystemImplementation3.3.1Common Design Layout3.3.2Asynchronous Mode Implementation3.3.3Adaptive Mode Implementation3.3.4Synchronous Mode Implementation3.3.4Synchronous Mode Implementation4.1.1Functional ResultsFunctional Results for Asynchronous Mode | 51<br>52<br>52<br>52<br>54<br>54<br>57<br>62<br>67<br><b>71</b><br>71                                                              |

|   | 3.1<br>3.2<br>3.3<br>Res                      | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | 51<br>52<br>52<br>52<br>54<br>54<br>54<br>57<br>62<br>67<br><b>71</b><br>71                                                        |

|   | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1        | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | 51<br>52<br>52<br>52<br>54<br>54<br>54<br>57<br>62<br>67<br><b>71</b><br>71<br>71<br>76<br>80                                      |

|   | 3.1<br>3.2<br>3.3<br>Res                      | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62 \\ 67 \\ 71 \\ 71 \\ 71 \\ 76 \\ 80 \\ 83 \\ 83$                                     |

|   | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1        | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62 \\ 67 \\ 71 \\ 71 \\ 71 \\ 76 \\ 80 \\ 83 \\ 84 \\ 84$                               |

|   | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1        | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62 \\ 67 \\ 71 \\ 71 \\ 71 \\ 76 \\ 80 \\ 83 \\ 83$                                     |

|   | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1<br>4.2 | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62 \\ 67 \\ 71 \\ 71 \\ 71 \\ 76 \\ 80 \\ 83 \\ 84 \\ 84$                               |

| 4 | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1<br>4.2 | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | $51 \\ 52 \\ 52 \\ 52 \\ 54 \\ 54 \\ 57 \\ 62 \\ 67 \\ 71 \\ 71 \\ 71 \\ 76 \\ 80 \\ 83 \\ 84 \\ 92 \\$                            |

| 4 | 3.1<br>3.2<br>3.3<br><b>Res</b><br>4.1<br>4.2 | Hardware Selection                                                                                                                                                                                                                                                                                                                                         | 51<br>52<br>52<br>52<br>54<br>54<br>54<br>57<br>62<br>67<br><b>71</b><br>71<br>71<br>71<br>76<br>80<br>83<br>84<br>92<br><b>95</b> |

| Bibliography |                          | 99              |                                                      |                   |

|--------------|--------------------------|-----------------|------------------------------------------------------|-------------------|

| A            | USE<br>A.1<br>A.2<br>A.3 | Asyncl<br>Adapt | riptors<br>hronous Mode USB Descriptor Table         | I<br>I<br>IV<br>V |

| В            | $\operatorname{Reg}$     | ister N         | Aaps for Si5351                                      | VII               |

|              | B.1                      | Regist          | er Map Generated by ClockBuilder Pro                 | VII               |

|              | B.2                      | Manua           | ally Generated Register Values                       | VIII              |

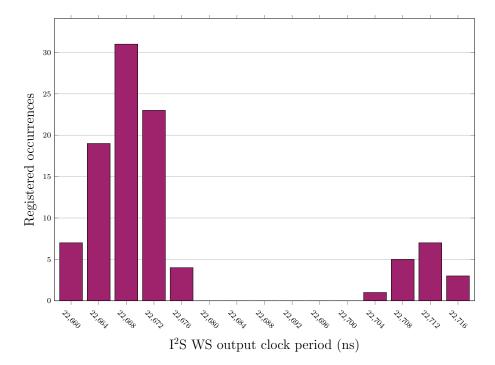

| $\mathbf{C}$ | Jitte                    | er Hist         | ograms                                               | XI                |

|              | C.1                      | Asyncl          | hronous Mode Jitter Histograms                       | XI                |

|              |                          | C.1.1           | Asynchronous Mode with Si5351 Integer Multisynth     | XI                |

|              |                          | C.1.2           | Asynchronous Mode with External Crystal Oscillator . | XIV               |

|              |                          | C.1.3           | Asynchronous Mode with Fixed Frequency Clock         | XVI               |

|              |                          | C.1.4           | Asynchronous Mode with Custom Fractional Divider .   | XIX               |

|              |                          | C.1.5           | Asynchronous Mode with Si5351 Integer Multisynth     | XXI               |

|              | C.2                      | Adapt           | ive Mode Jitter Histograms                           | XXIV              |

|              |                          | C.2.1           | Adaptive Mode with Si5351 Integer Multisynth         | XXIV              |

|              |                          | C.2.2           | Adaptive Mode with Si5351 Fractional Multisynth      | XXVI              |

|              | C.3                      | Synchi          | ronous Mode Jitter Histograms                        | XXIX              |

|              |                          | Č.3.1           | Synchronous Mode with Custom Fractional Divider      | XXIX              |

# List of Figures

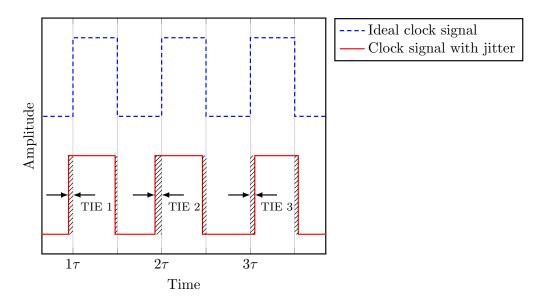

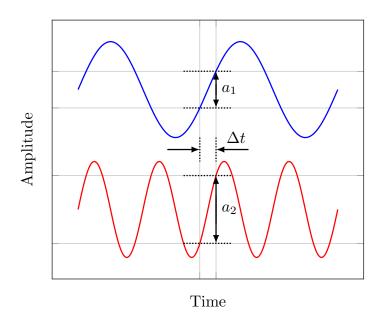

| 2.1  | Jitter assessment for a clock signal having a reference            | 6               |

|------|--------------------------------------------------------------------|-----------------|

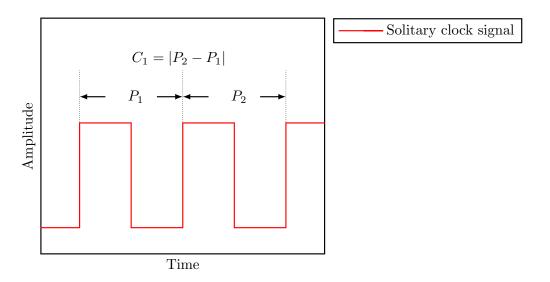

| 2.2  | Jitter assessment for a solitary clock signal                      | 6               |

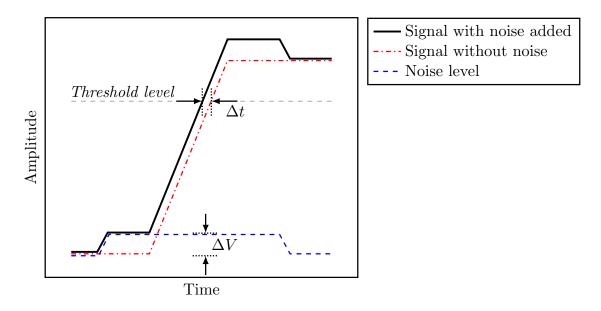

| 2.3  | Visualization of how noise in the voltage domain can produce       |                 |

|      | jitter                                                             | 7               |

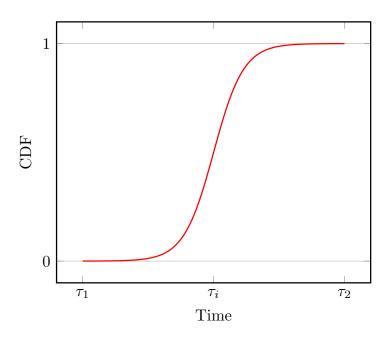

| 2.4  | Theoretical example of a cumulative distribution function for a    |                 |

|      | clock signal with ideal transition time at $\tau_i$ .              | 8               |

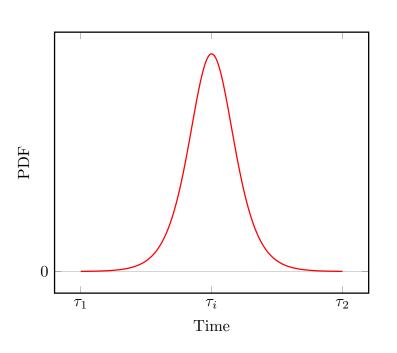

| 2.5  | The probability density function corresponding to the cumulative   |                 |

|      | distribution function in Figure 2.4.                               | 9               |

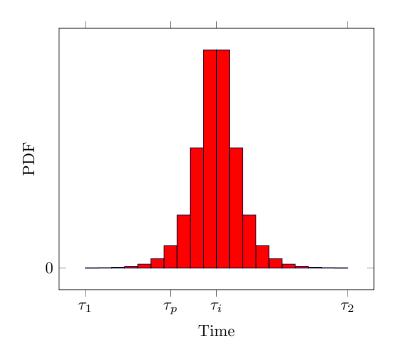

| 2.6  | The probability density function from Figure 2.5 divided into      | 0               |

|      | time brackets with an arbitrary point in time $\tau_p$ selected    | 9               |

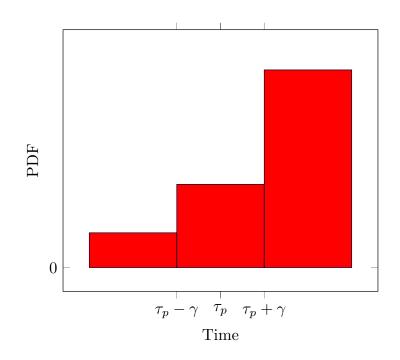

| 2.7  | A closeup of the probability density function in Figure 2.6 around | 0               |

| 2.1  | the arbitrarily selected point in time $\tau_p$                    | 10              |

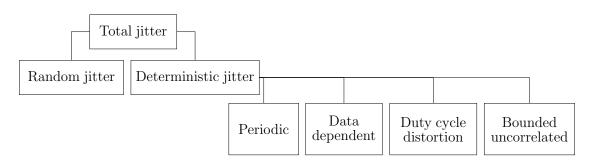

| 2.8  | Jitter components contributing to total jitter.                    | 11              |

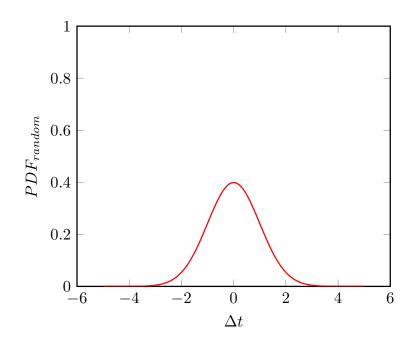

| 2.9  | Probability density function for random jitter                     | 11              |

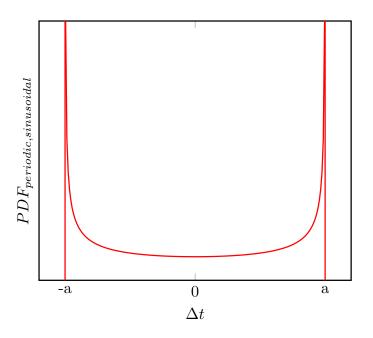

| 2.10 | The probability density function for a sinusoidal periodic jitter  | 11              |

| 2.10 | distribution.                                                      | 12              |

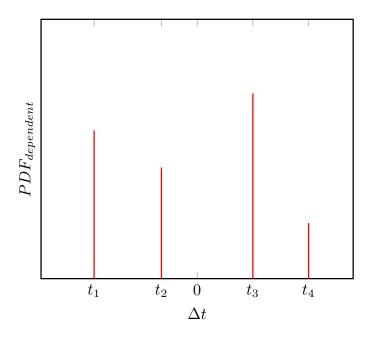

| 2.11 | Typical probability density function for data dependent jitter.    | 13              |

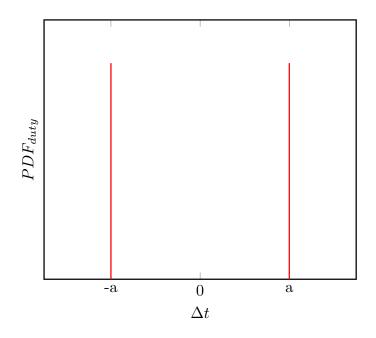

|      | Probability density function for duty cycle distortion             | 14              |

|      | The size of an amplitude error caused by a timing error depends    | 11              |

| 2.10 | on the slope of the signal.                                        | 15              |

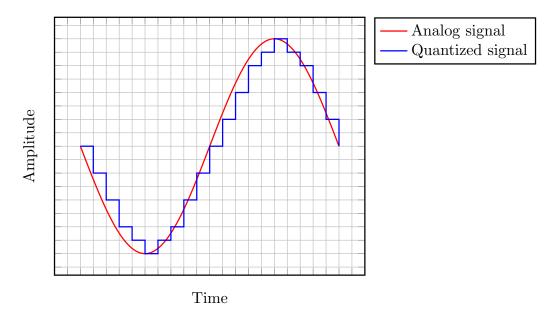

| 2 14 | Analog sine wave and the resulting waveform after quantization     | 10              |

| 2.11 | in low resolution.                                                 | 19              |

| 2 15 | Data structure of AES/EBU and S/PDIF. The contents of a) an        | 10              |

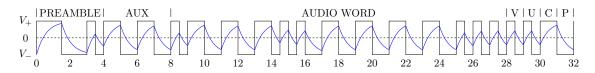

| 2.10 | audio block, b) a frame and c) a subframe                          | 21              |

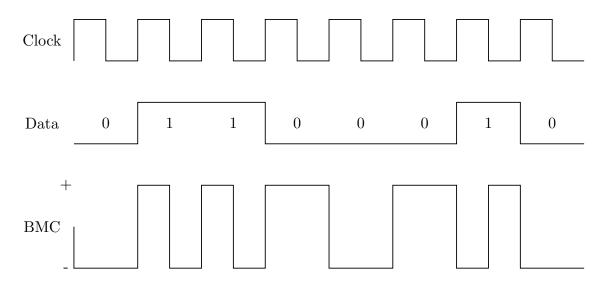

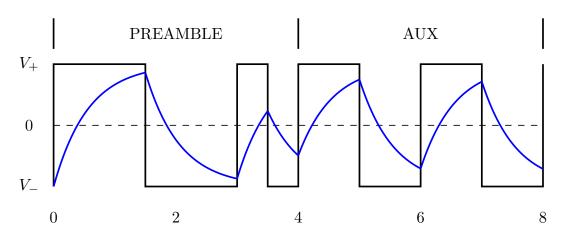

| 2 16 | Biphase mark code timing diagram.                                  | $\frac{21}{22}$ |

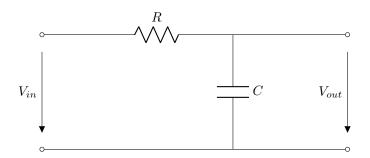

|      | First order passive low pass filter used to simulate bandwidth     |                 |

| 2.11 | limited transmission channel.                                      | 23              |

| 2.18 | Transmission of one subframe over bandwidth limited channel.       | 23<br>23        |

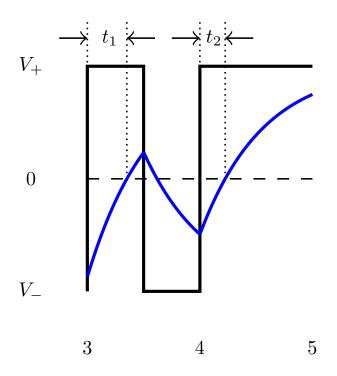

|      | First eight bits of the subframe                                   | 20<br>24        |

|      | Bits four and five of the subframe                                 | 24              |

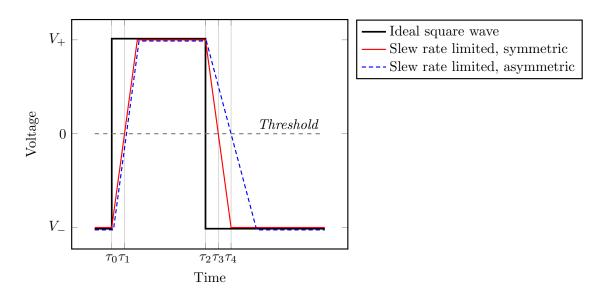

|      | Symmetric versus asymmetric slew rate response to an ideal square  | 21              |

| 2.21 | wave                                                               | 25              |

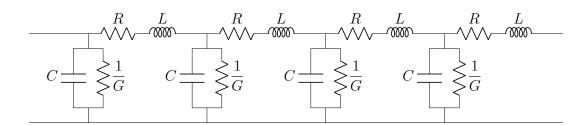

| 2.22 | Cascaded network model for high frequency transmission line.       | $\frac{25}{25}$ |

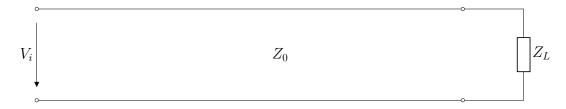

|      | Transmission line with load attached                               | $\frac{25}{26}$ |

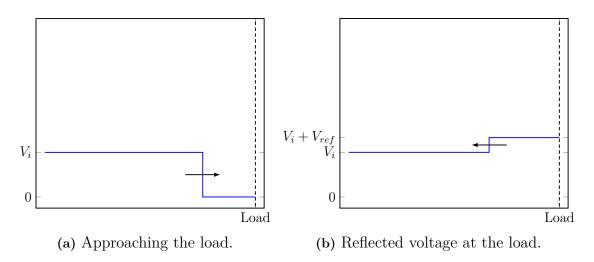

|      | High frequency voltage pulse applied to a transmission line        | $20 \\ 27$      |

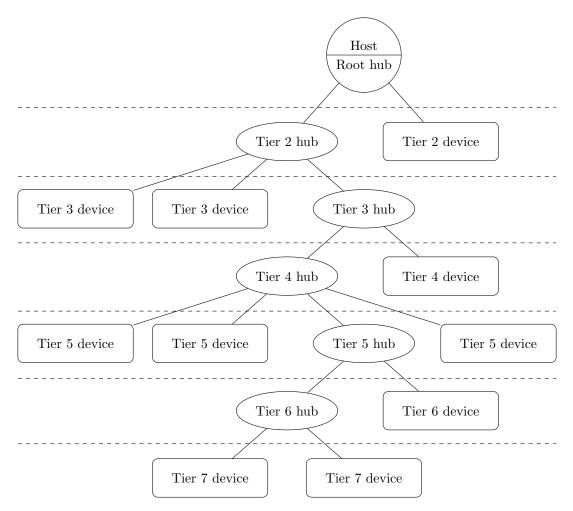

|      | USB topology                                                       | $\frac{21}{30}$ |

| 4.40 | 00D 10p0106.y                                                      | 50              |

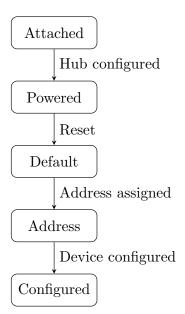

| 2.26         | Device state changes during enumeration process                      | 31         |

|--------------|----------------------------------------------------------------------|------------|

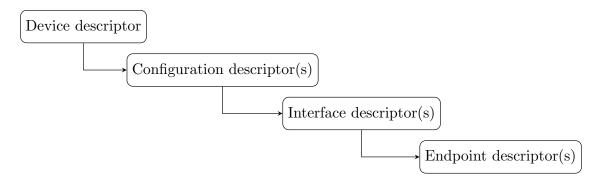

| 2.27         | Configuration, interface and endpoint descriptor structure           | 32         |

| 2.28         | Delay induced due to prebuffering at endpoints                       | 36         |

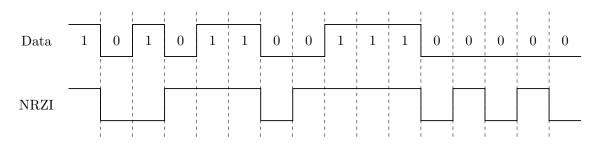

| 2.29         | Example of NRZI encoded data                                         | 36         |

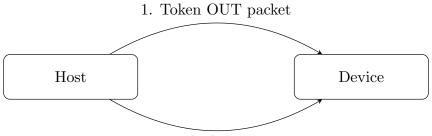

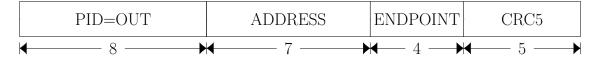

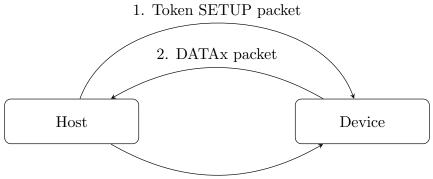

| 2.30         | Isochronous USB OUT transaction sequence                             | 39         |

| 2.31         | USB OUT token packet.                                                | 39         |

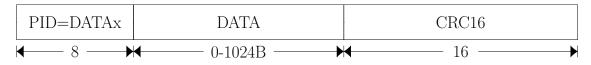

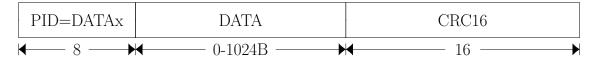

| 2.32         | USB DATAx packet.                                                    | 39         |

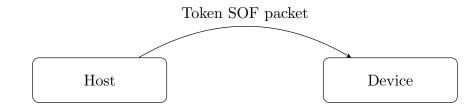

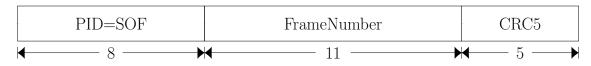

| 2.33         | USB SOF packet transaction sequence                                  | 39         |

| 2.34         | USB SOF packet                                                       | 39         |

|              | USB control transfer sequence                                        | 40         |

| 2.36         | USB SETUP packet used in a control transfer                          | 40         |

| 2.37         | USB DATAx packet used in a control transfer                          | 40         |

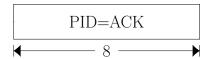

| 2.38         | USB ACK handshake packet used in a control transfer                  | 40         |

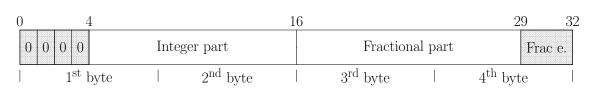

| 2.39         | Feedback format for full-speed endpoint                              | 43         |

| 2.40         | Feedback format for high-speed endpoint                              | 43         |

| 2.41         | $I^2S$ transmitter and receiver pair with the transmitter having the |            |

|              | role of the controller                                               | 47         |

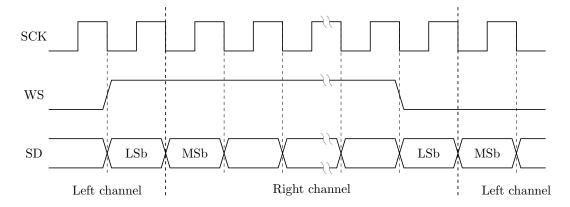

| 2.42         | $I^2S$ interface timing diagram                                      | 48         |

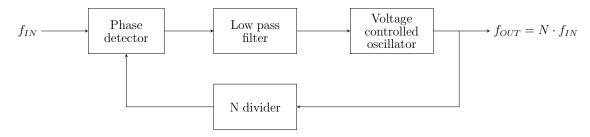

| 2.43         | Block diagram of a phase-locked loop                                 | 49         |

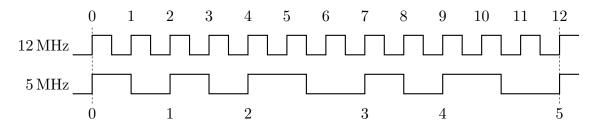

|              | Example of fractional division by 2.4                                | 50         |

| 0.1          |                                                                      | 50         |

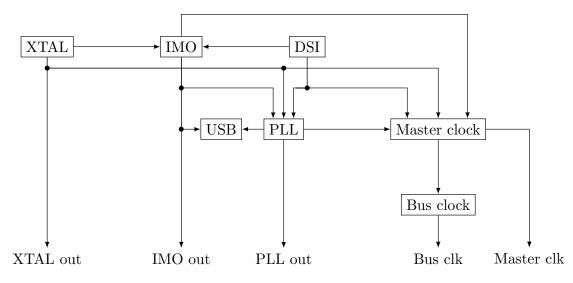

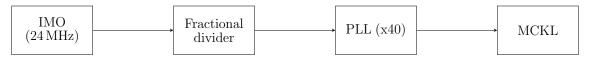

| 3.1          | The PSoC core clocking network.                                      | 53         |

| 3.2          | Layout of the audio path and the physical entities.                  | 55         |

| 3.3          | General transfer sequence for USB audio transmissions                | 55         |

| 3.4          | Audio data transfer path inside the PSoC device                      | 56         |

| 3.5          | $I^2C$ single register write operation                               | 57         |

| 3.6          | $I^2C$ burst write operation to two consecutive registers            | 58         |

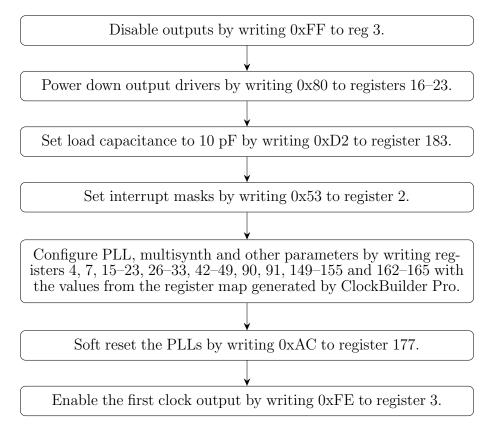

| 3.7          | Programming procedure for the Adafruit Si5351 external clock         | <b>F</b> 0 |

| <b>n</b> 0   | generator board.                                                     | 58<br>50   |

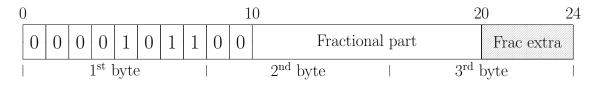

| 3.8          | Feedback array with integer part populated.                          | 59<br>60   |

| 3.9          | Bit values around the decimal point in the feedback array            | 60         |

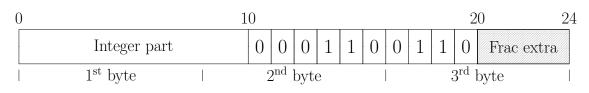

|              | Feedback array with the fractional part populated.                   | 61         |

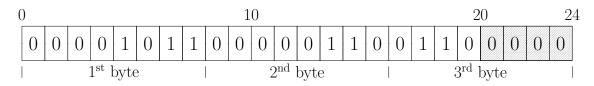

|              | The complete USB feedback array.                                     | 61         |

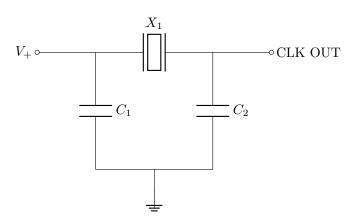

|              | Crystal oscillator circuit used for generating external clock        | 62         |

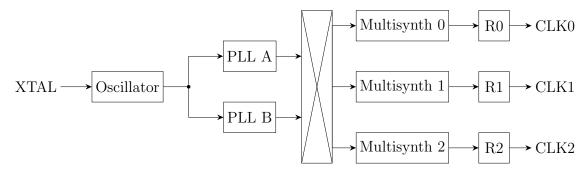

|              | Si5351 block diagram.                                                | 63         |

| 3.14         | Clock configuration for the synchronous mode implementation.         | 69         |

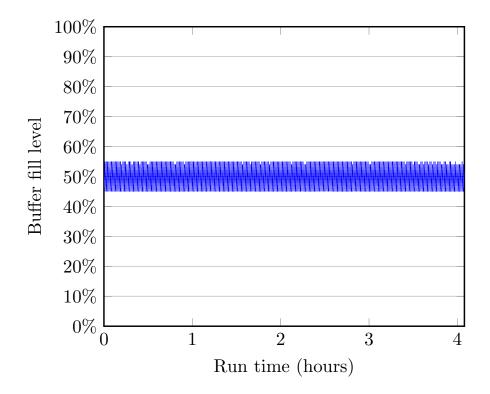

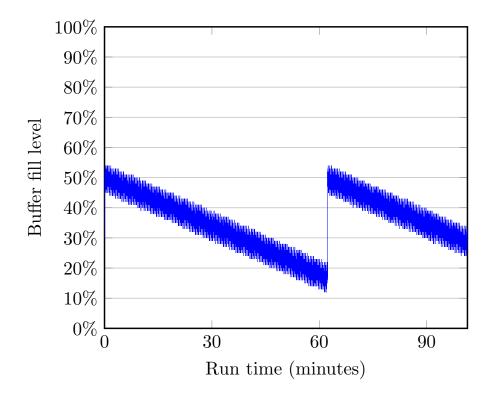

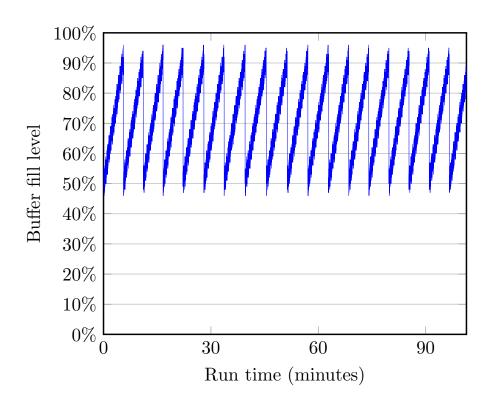

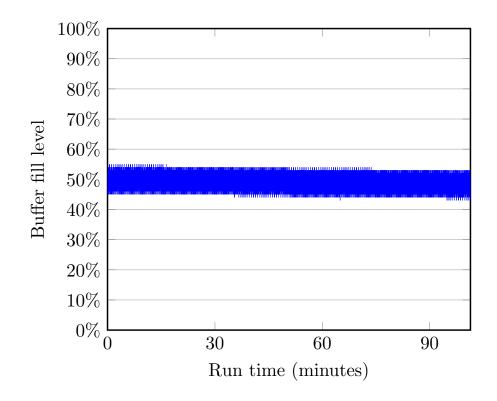

| 4.1          | Buffer fill level during four hour long playback session using asyn- |            |

| <b>T</b> , I | chronous mode.                                                       | 72         |

| 4.2          | Accumulative error without correction of buffer fill.                | 74         |

| 4.3          | Accumulative error with correction of buffer fill.                   | 74         |

| 4.4          | Accumulative error with correction of build hill.                    | 14         |

| 1.1          | ber of buffer chunks.                                                | 75         |

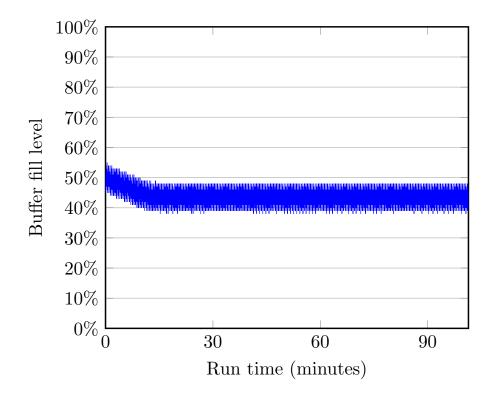

| 4.5          | Increasing the number of buffer chunks to twenty for asynchronous    | 10         |

| 1.0          | mode.                                                                | 75         |

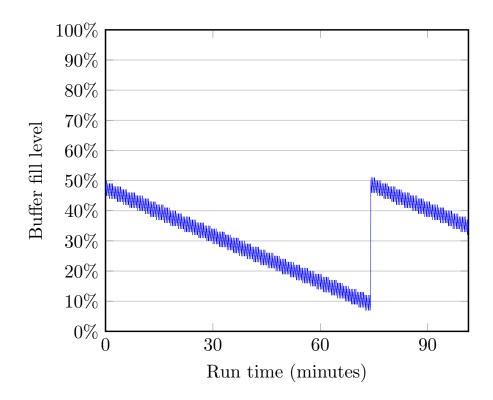

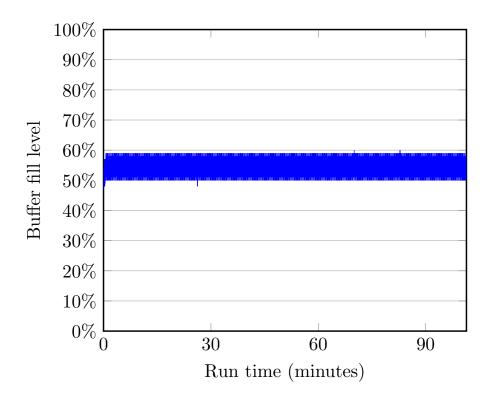

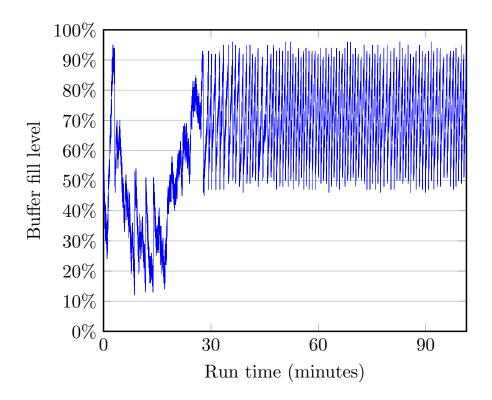

| 4.6          | Buffer fill level for USB in adaptive mode with the multisynth in    | 10         |

| <b>r</b> .0  | integer mode without clock adjustment                                | 78         |

|              |                                                                      | 10         |

| 4.7               | Buffer fill level for USB in adaptive mode with the multisynth in                | 70    |

|-------------------|----------------------------------------------------------------------------------|-------|

|                   | integer mode and clock adjustment activated.                                     | 78    |

| 4.8               | Buffer fill level for USB in adaptive mode with the multisynth in                | -     |

|                   | fractional mode without clock adjustment.                                        | 79    |

| 4.9               | Buffer fill level for USB in adaptive mode with the multisynth in                | -     |

|                   | fractional mode and clock adjustment activated                                   | 79    |

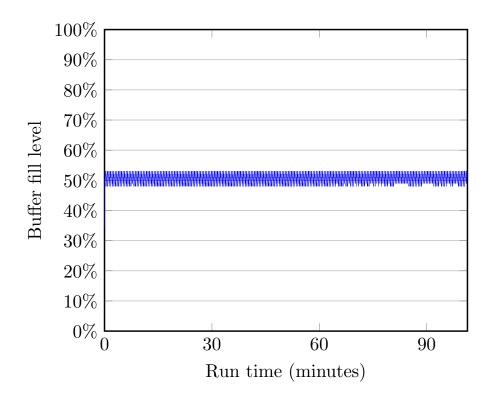

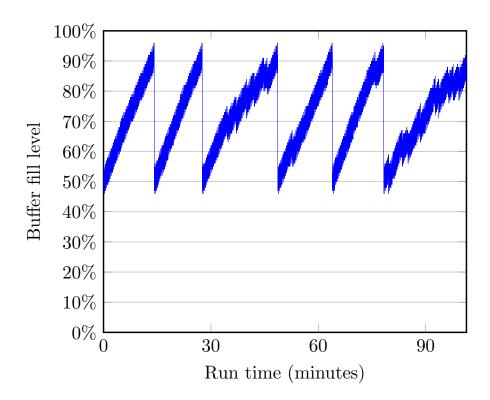

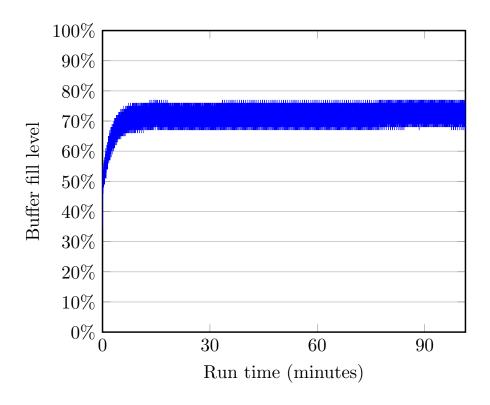

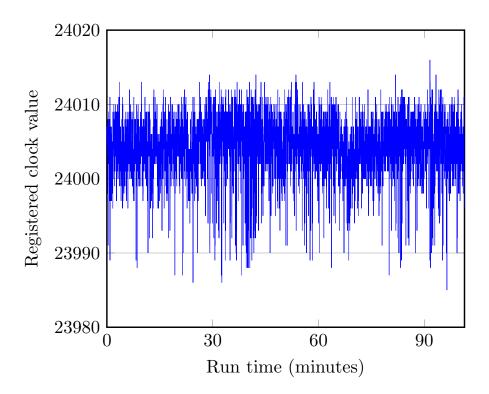

| 4.10              | Buffer fill level for USB in synchronous mode with frequency                     |       |

|                   | updating turned on                                                               | 81    |

| 4.11              | Buffer fill level for USB in synchronous mode with frequency                     |       |

|                   | updates turned off                                                               | 82    |

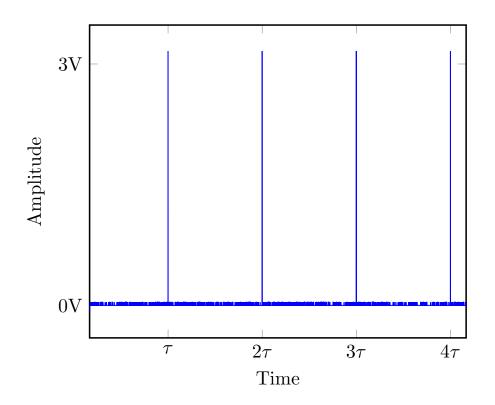

|                   | PSoC IMO clock pulses registered per SOF.                                        | 82    |

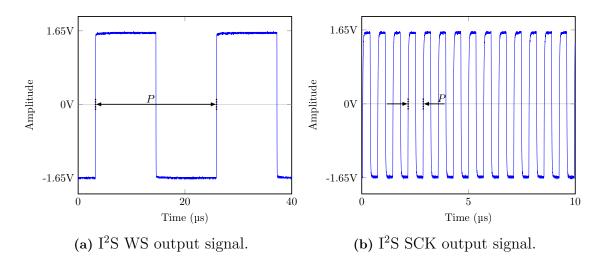

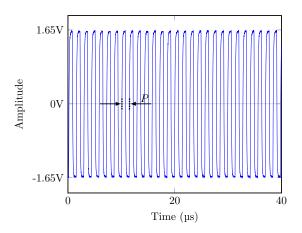

|                   | Capture of one measurement each for the $\mathrm{I}^2\mathrm{S}$ output signals  | 84    |

|                   | Capture of one measurement for the $I^2S$ input signal                           | 84    |

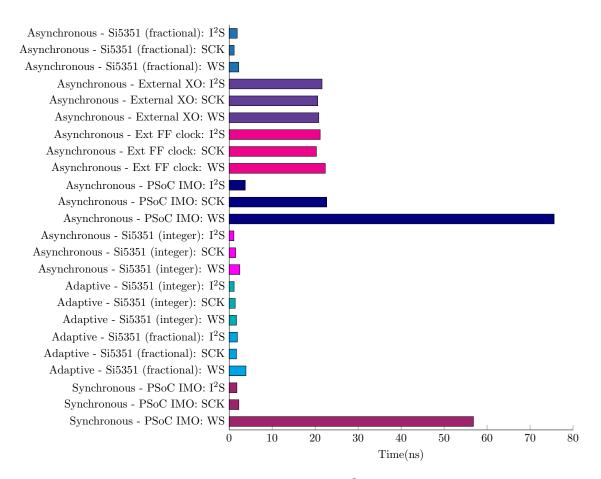

| 4.15              | Period peak-to-peak jitter for the I <sup>2</sup> S component input and SCK      |       |

|                   | and WS output clocks for each of the implementations                             | 88    |

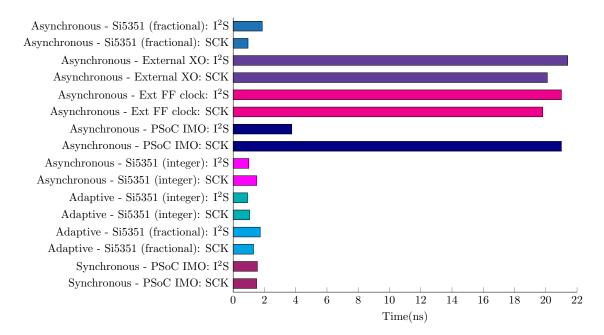

| 4.16              | Cycle-to-cycle peak jitter for the I <sup>2</sup> S component input and SCK      |       |

|                   | output clocks for each of the implementations                                    | 88    |

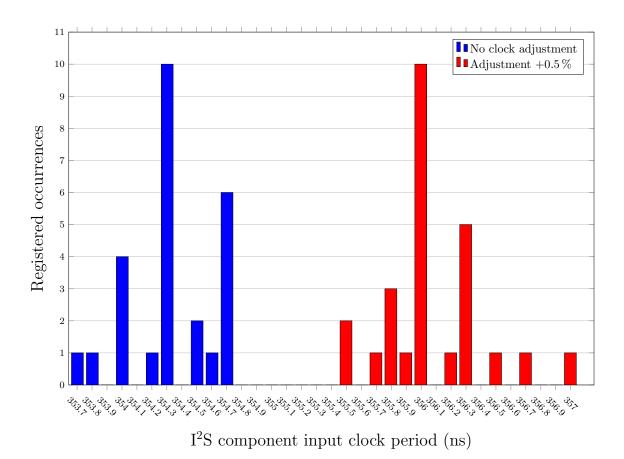

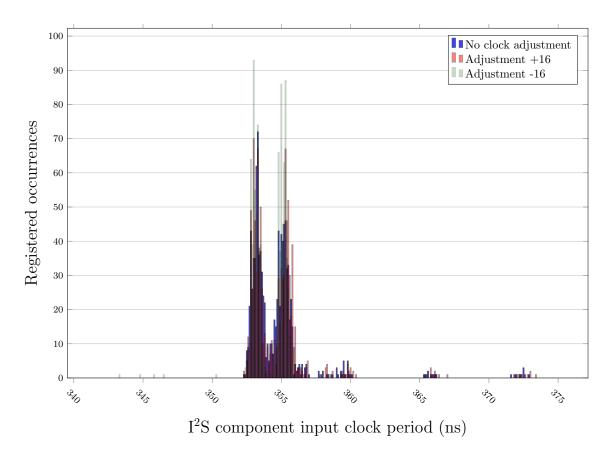

| 4.17              | Period histogram for two adjacent adjustment levels for the $I^2S$               |       |

|                   | component input clocks in USB adaptive mode with the multi-                      |       |

|                   | synth set to integer mode                                                        | 89    |

| 4.18              | Period histograms with and without clock adjustments for the                     |       |

|                   | I <sup>2</sup> S component input clock in USB asynchronous mode using the        |       |

|                   | IMO together with the fractional divider as clock source                         | 91    |

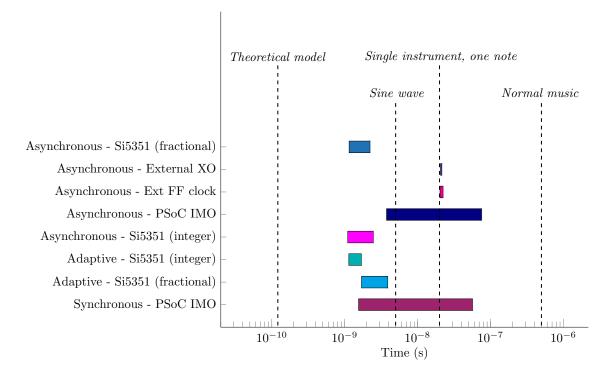

| 4.19              | The range of period jitter peak-to-peak values for all three $I^2S$              |       |

|                   | component clocks compared to the theoretical jitter audibility                   |       |

|                   | model and the jitter audibility thresholds determined by listening               |       |

|                   | tests                                                                            | 92    |

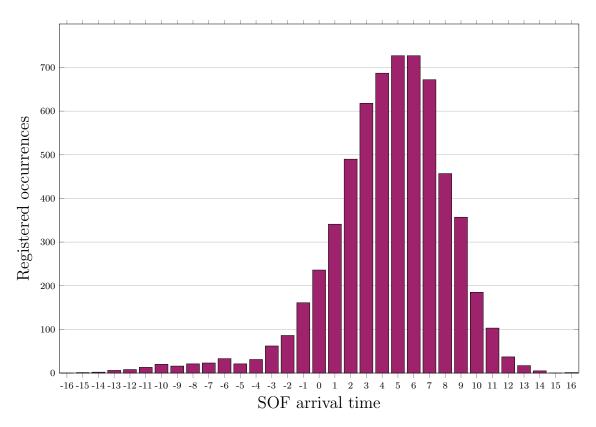

| 4.20              | Start-of-frame packets received by the PSoC USBFS component.                     | 93    |

| 4.21              | Histogram of SOF arrival time variation referenced to IMO clock                  |       |

|                   | data from Figure 4.12                                                            | 93    |

| C 1               |                                                                                  |       |

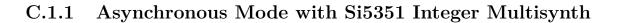

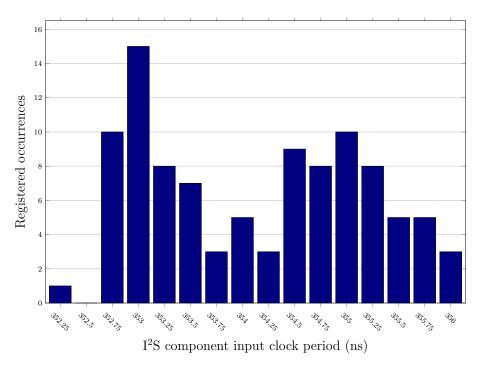

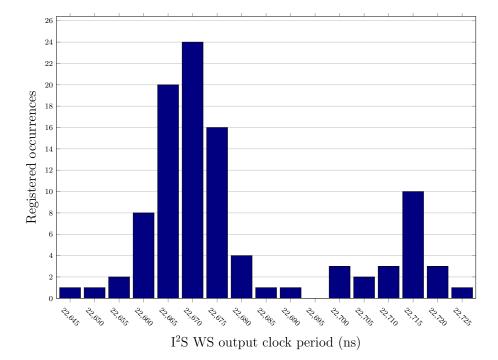

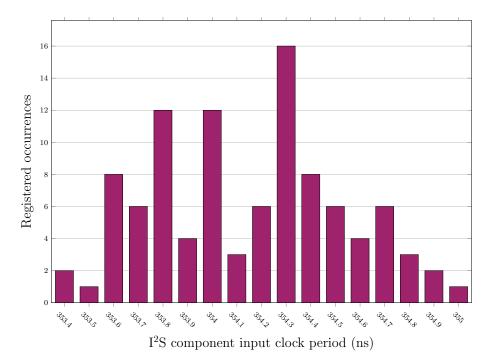

| C.1               | I <sup>2</sup> S component input clock period jitter histogram for asynchronous  | 371   |

| <i><i>C a</i></i> | mode USB with the Si5351 multisynth set to fractional mode.                      | XI    |

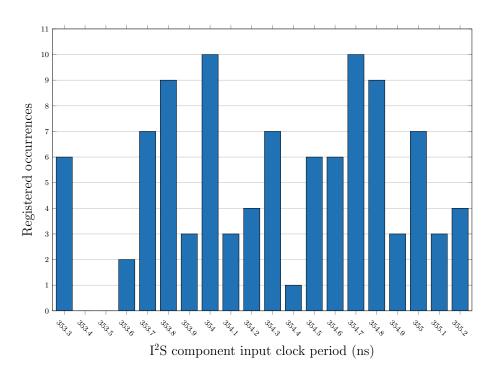

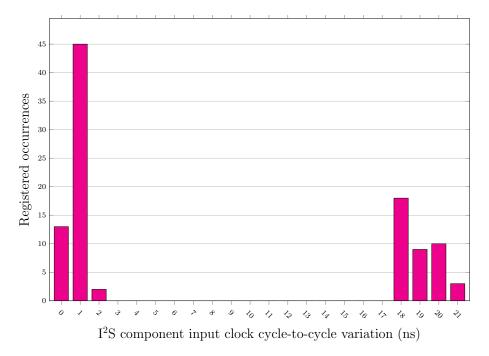

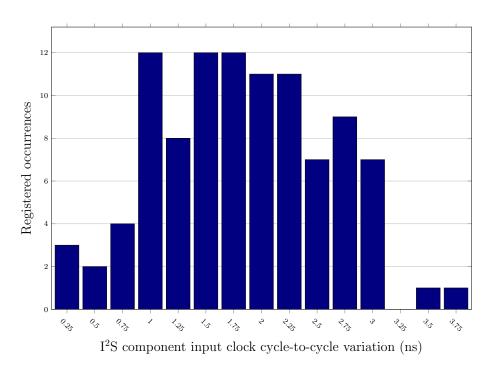

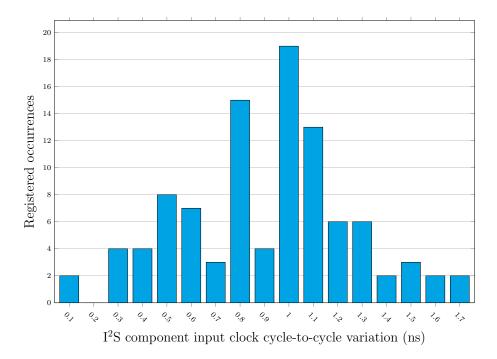

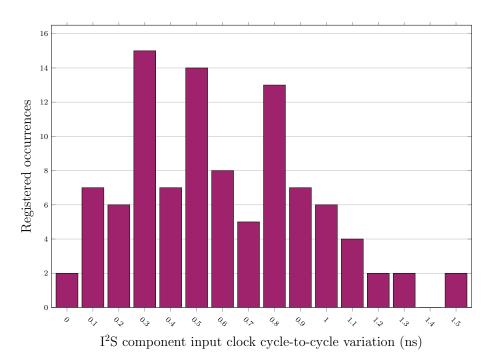

| C.2               | I <sup>2</sup> S component input clock cycle-to-cycle jitter histogram for asyn- |       |

|                   | chronous mode USB with the Si5351 multisynth set to fractional                   | 3711  |

| <b>C</b> a        | mode.                                                                            | XII   |

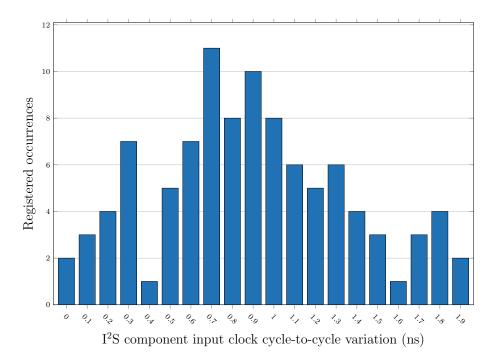

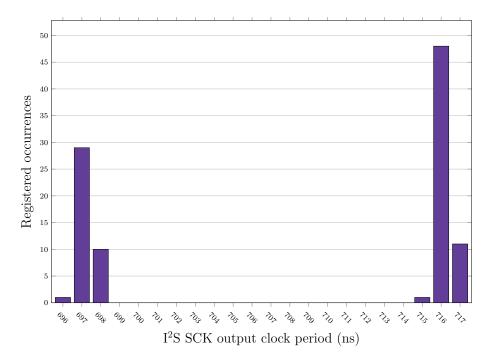

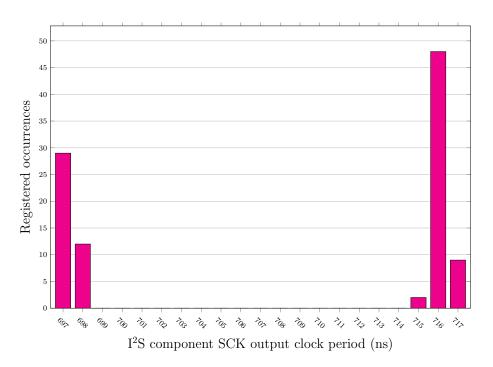

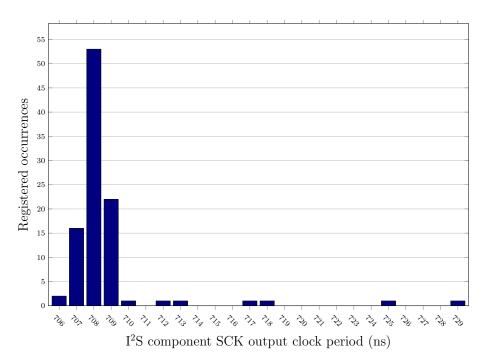

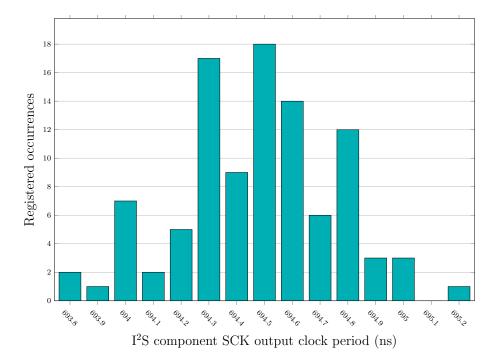

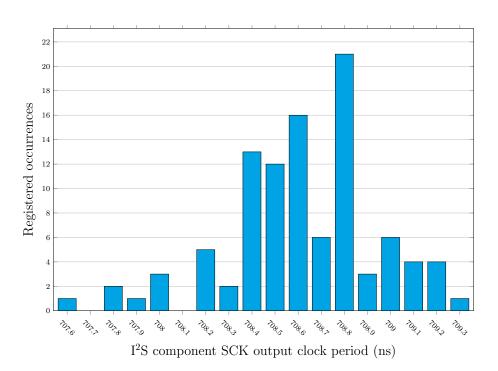

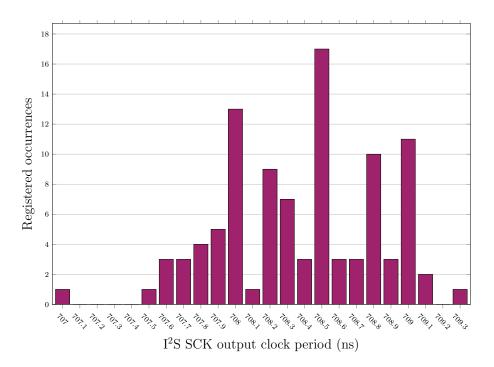

| C.3               | I <sup>2</sup> S SCK signal period jitter histogram for asynchronous mode        |       |

| ~ .               | USB with the Si5351 multisynth set to fractional mode                            | XII   |

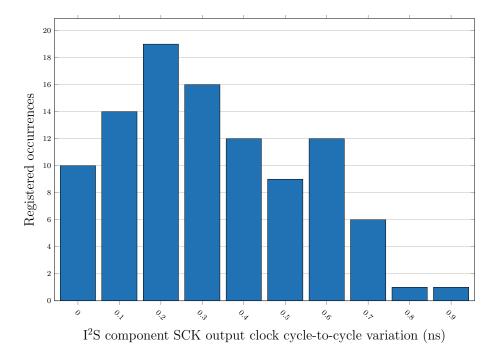

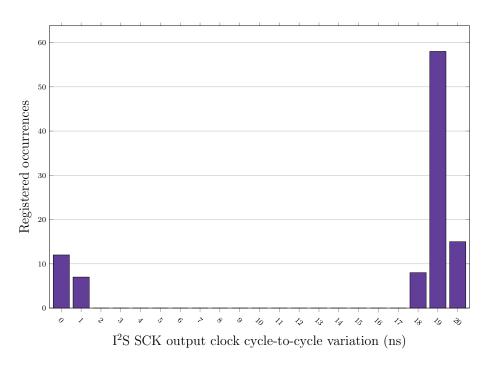

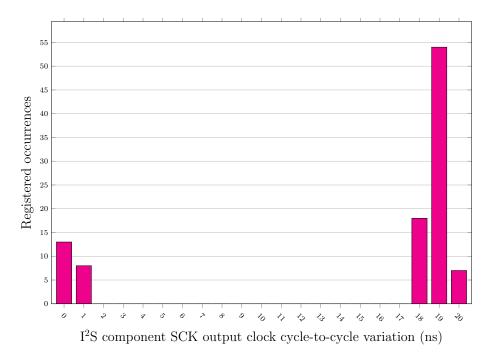

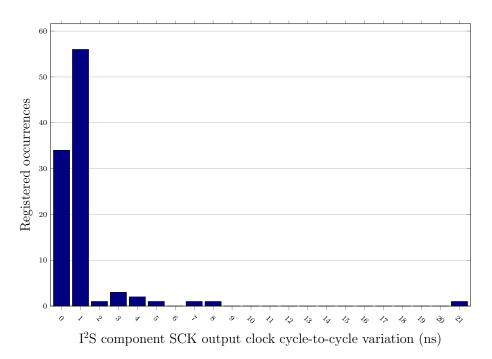

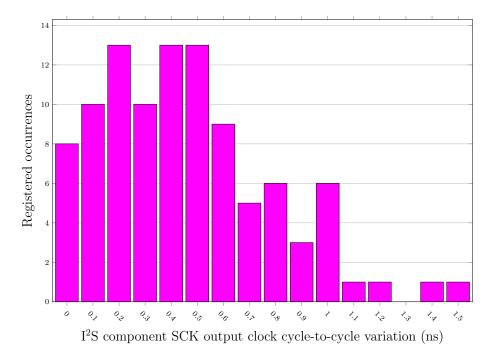

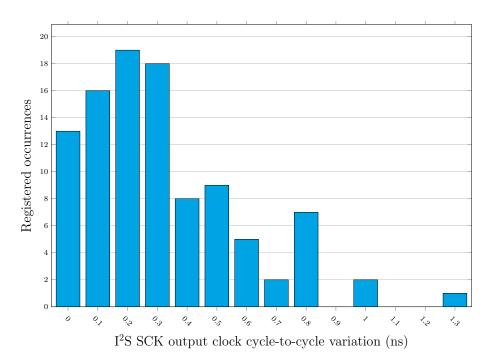

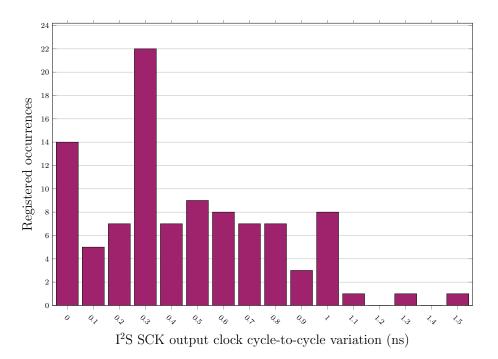

| C.4               | I <sup>2</sup> S SCK signal cycle-to-cycle jitter histogram for asynchronous     | 37777 |

|                   | mode USB with the Si5351 multisynth set to fractional mode.                      | XIII  |

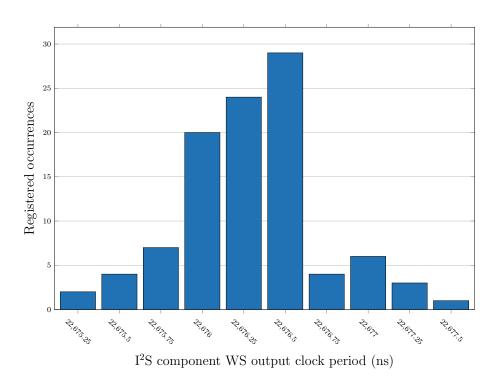

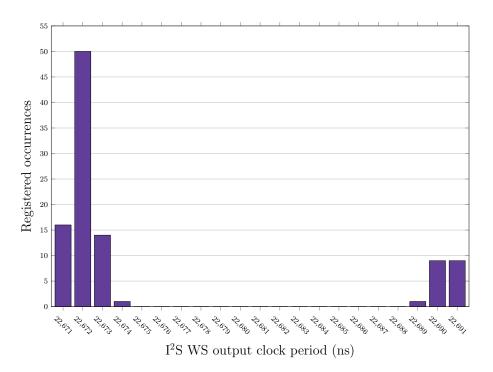

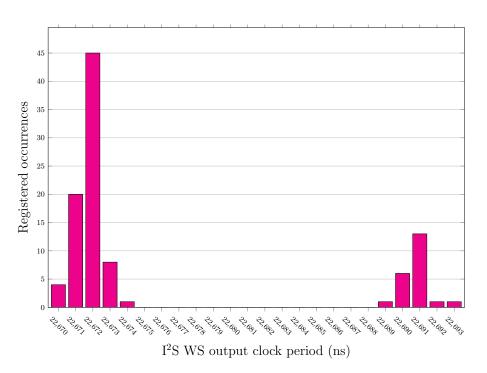

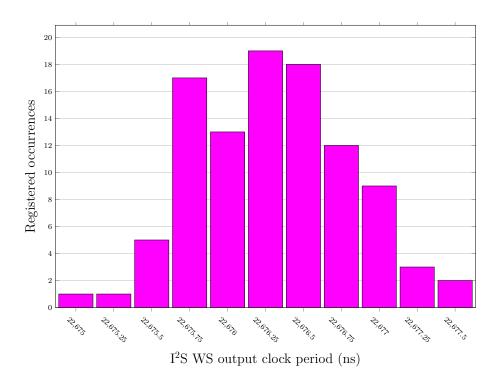

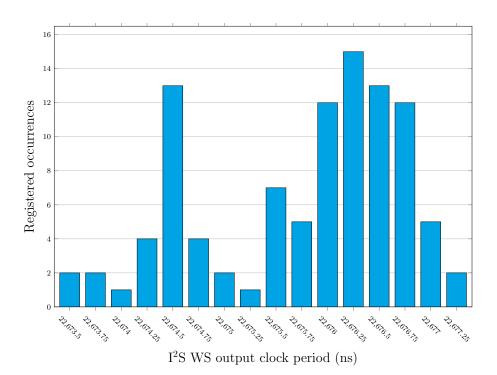

| C.5               | I <sup>2</sup> S WS signal period jitter histogram for asynchronous mode         |       |

|                   | USB with the Si5351 multisynth set to fractional mode                            | XIII  |

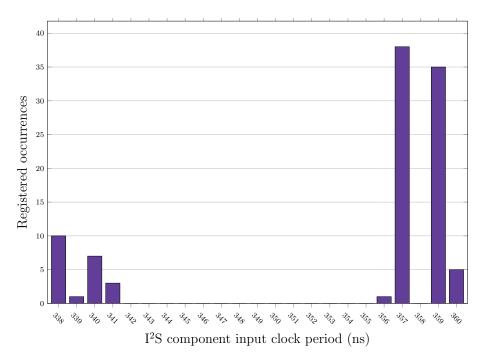

| C.6               | I <sup>2</sup> S component input clock period jitter histogram for asynchronous  |       |

|                   | mode USB using the external XO as source clock                                   | XIV   |

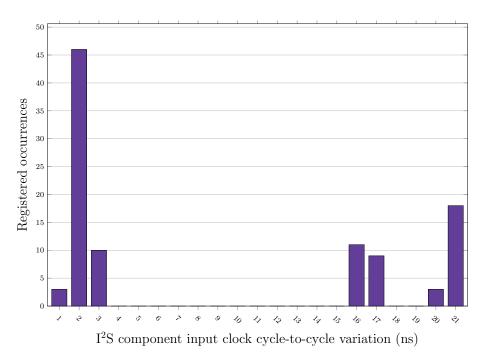

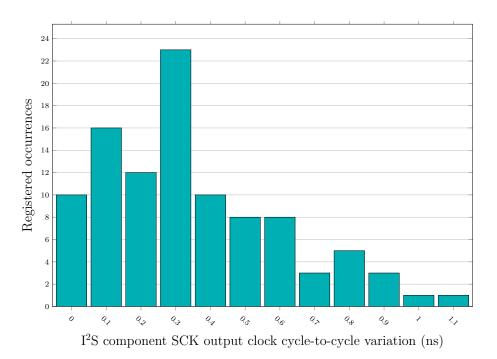

| C.7               | I <sup>2</sup> S component input clock cycle-to-cycle jitter histogram for asyn- |       |

|                   | chronous mode USB using the external XO as source clock                          | XIV   |

| C.8      | I <sup>2</sup> S SCK signal period jitter histogram for asynchronous mode USB using the external XO as source clock.                                                                                            | XV            |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|          | I <sup>2</sup> S SCK signal cycle-to-cycle jitter histogram for asynchronous mode USB using the external XO as source clock                                                                                     | XV            |

|          | I <sup>2</sup> S WS signal period jitter histogram for asynchronous mode<br>USB using the external XO as source clock.                                                                                          | XVI           |

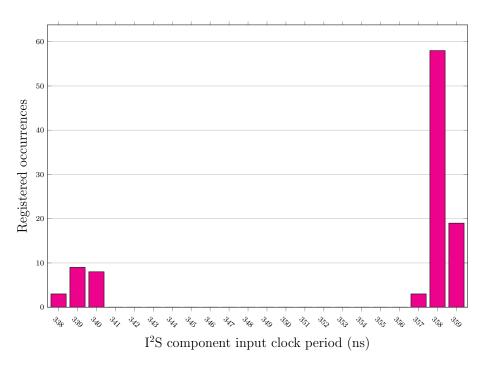

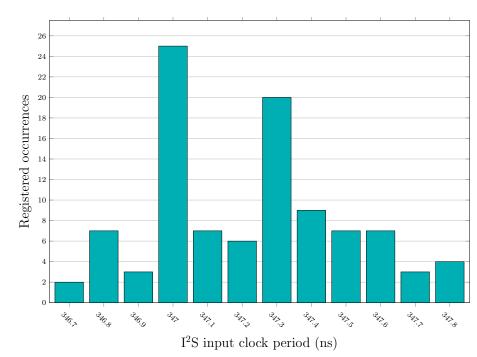

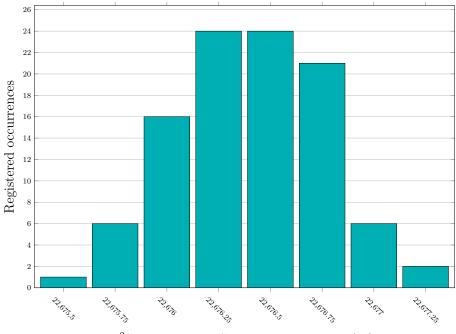

| C.11     | I <sup>2</sup> S component input clock period jitter histogram for asynchronous<br>mode USB using the external fixed frequency clock board as<br>source clock                                                   | XVI           |

| C.12     | $I^2S$ component input clock cycle-to-cycle jitter histogram for asynchronous mode USB using the external fixed frequency clock                                                                                 |               |

| C.13     | board as source clock                                                                                                                                                                                           | XVII          |

| $C_{14}$ | USB using the external fixed frequency clock board as source<br>clock. $\ldots$                                                | XVII          |

| 0.14     | I <sup>2</sup> S SCK signal cycle-to-cycle jitter histogram for asynchronous<br>mode USB using the external fixed frequency clock board as<br>source clock                                                      | XVIII         |

| C.15     | $I^2S$ WS signal period jitter histogram for asynchronous mode<br>USB using the external fixed frequency clock board as source                                                                                  |               |

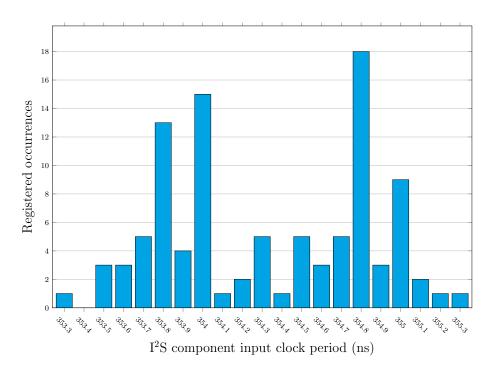

| C.16     | clock                                                                                                                                                                                                           | XVIII         |

|          | mode USB using the IMO as source clock together with the frac-<br>tional divider component.                                                                                                                     | XIX           |

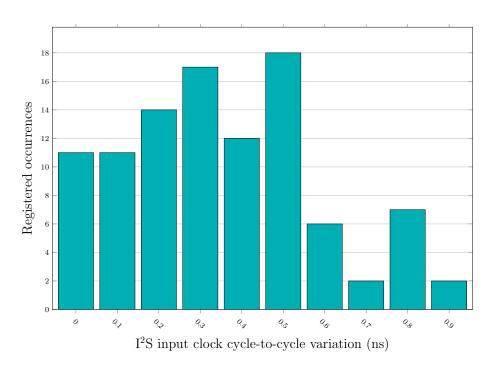

| C.17     | I <sup>2</sup> S component input clock cycle-to-cycle jitter histogram for asyn-<br>chronous mode USB using the IMO as source clock together with<br>the fractional divider component.                          | XIX           |

| C.18     | I <sup>2</sup> S SCK signal period jitter histogram for asynchronous mode USB using the IMO as source clock together with the fractional                                                                        |               |

| C.19     | divider component                                                                                                                                                                                               | XX            |

| $C_{20}$ | mode USB using the IMO as source clock together with the frac-<br>tional divider component. $\dots \dots \dots$ | XX            |

| 0.20     | USB using the IMO as source clock together with the fractional divider component.                                                                                                                               | XXI           |

| C.21     | $I^2S$ component input clock period jitter histogram for asynchronous mode USB with the Si5351 multisynth set to integer mode                                                                                   | XXI           |

| C.22     | $\rm I^2S$ component input clock cycle-to-cycle jitter histogram for a<br>synchronous mode USB with the Si5351 multisynth set to integer                                                                        |               |

| C.23     | mode                                                                                                                                                                                                            | XXII          |

| C.24     | USB with the Si5351 multisynth set to integer mode. $\dots$ I <sup>2</sup> S SCK signal cycle-to-cycle jitter histogram for asynchronous mode USB with the Si5251 multisynth set to integer mode.               | XXII<br>XXIII |

|          | mode USB with the Si5351 multisynth set to integer mode                                                                                                                                                         | ΛΛΠΙ          |

| C.25 I <sup>2</sup> S WS signal period jitter histogram for asynchronous mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| USB with the Si5351 multisynth set to integer mode. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XXIII                    |

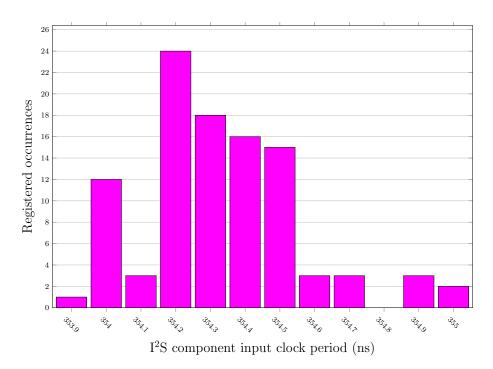

| C.26 $I^2S$ component input clock period jitter histogram for adaptive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| mode USB with the Si5351 multisynth set to integer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XXIV                     |

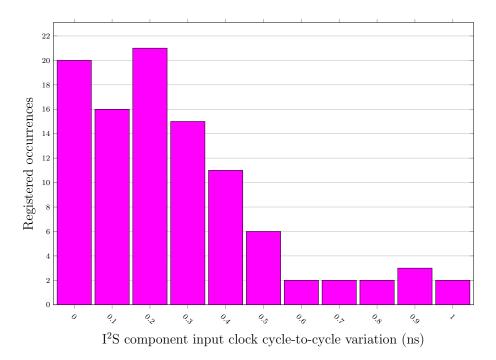

| C.27 $I^2S$ component input clock cycle-to-cycle jitter histogram for adap-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| tive mode USB with the Si5351 multisynth set to integer mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XXIV                     |

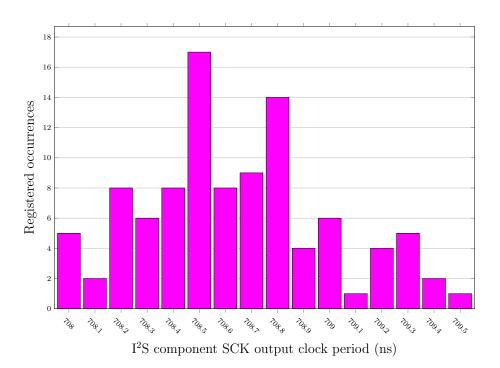

| C.28 I <sup>2</sup> S SCK signal period jitter histogram for adaptive mode USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |