# CHALNAERS VANCE 1829

Modelling and analysis of Shunt-connected Voltage Source Converter for voltage dip mitigation

## PAOLO CILONA

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2010

#### THESIS FOR THE DEGREE OF MASTER SCIENCE

# Modelling and analysis of Shunt-connected Voltage Source Converter for voltage dip mitigation

PAOLO CILONA

Department of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2010

Modelling and analysis of Shunt-connected Voltage Source Converter for voltage dip mitigation PAOLO CILONA

Department of Electric Power Engineering

Chalmers University of Technology

#### Abstract

Distribution Static Synchronous Compensator (D-STATCOM) is a Custom Power Device based on a Voltage Source Converter (VSC) shunt connected to the grid. By injecting a controllable current, it can improve the quality of the load current, e.g. compensating harmonic currents or fluctuating currents. If a D-STATCOM is equipped with an energy storage, the system is also called Energy Storage Equipment STATCOM (E-STATCOM).

This thesis focuses on the E-STATCOM for mitigating voltage dips. A short description of power quality problems has been done, with particular attention a in-depth study on voltage dip problem and its solution has been conducted. Afterwards the control system for the E-STATCOM has been derived. The vector current- and voltage-controllers have been designed and their behaviour has been studied. The impact of controller bandwidths and of model parameters has been investigated. The dual vector current- voltage-controllers (DVCC DVVC) have been designed in order to improve the performance con the control system also under unbalanced conditions. All results are verified in MATLAB and simulated in PSCAD/EMTDC.

The system has been tested to mitigate both balanced and unbalanced voltage dips, with several types of loads.

Index Terms: Power Electronics, Power Quality, Current Controller, Voltage Controller, Voltage Dip (Sag), Voltage Source Converter (VSC), shunt compensation, dual vector controller, PLL.

#### Acknowledgements

This work has been carried out at Department of Electric Power Engineering, Chalmers University of Technology in Göteborg that I want acknowledge.

I would like to special thanks my supervisor Doctor Massimo Bongiorno for his support and encouragement during the work. Thanks for his patient discussions in each meeting, for his constant helpfulness and for having given me the opportunity to come to Sweden and live this great experience.

I would like to thank the staff at the Division of Electric Power Engineering for the friendly atmosphere they created.

Last, but surely not least, I would like to thank my family and in particular my parents for their love support throughout the years.

Paolo Cilona Gothenburg, Sweden March, 2010

# Contents

| $\mathbf{A}$ | bstra | nct                                                        | VII  |

|--------------|-------|------------------------------------------------------------|------|

| $\mathbf{A}$ | ckno  | wledgements                                                | IX   |

| $\mathbf{C}$ | onte  | nts                                                        | XII  |

| 1            | Inti  | roduction                                                  | 1    |

|              | 1.1   | Background and motivation                                  | . 1  |

|              | 1.2   | Aim and outline of this thesis                             | . 2  |

| 2            | Pov   | ver Quality and Custom Power                               | 3    |

|              | 2.1   | Introduction                                               | . 3  |

|              | 2.2   | Characterization of electric power quality                 | . 4  |

|              | 2.3   | Power Quality Problems                                     |      |

|              | 2.4   | Power Electronic Application in Power Distribution Systems | . 10 |

|              | 2.5   | Conclusions                                                |      |

| 3            | Vol   | tage Dips and Mitigation Methods                           | 15   |

|              | 3.1   | Analysis of voltage dip                                    | . 15 |

|              | 3.2   | Voltage dip mitigation                                     |      |

|              |       | 3.2.1 Power System Improvements                            |      |

|              |       | 3.2.2 Increasing Equipment Immunity                        |      |

|              |       | 3.2.3 Mitigation Devices                                   |      |

|              | 3.3   | Conclusion                                                 |      |

| 4            | Cor   | ntrol System for Shunt-Connected VSC                       | 33   |

|              | 4.1   | Introduction                                               |      |

|              | 4.2   | Description of electrical system                           |      |

|              | 4.3   | Control System                                             |      |

|              |       | 4.3.1 PLL-Type estimator                                   |      |

|              |       | 4.3.2 Vector Current-Controller(VCC)                       |      |

|              |       | 4.3.3 Vector Voltage-Controller(VVC)                       |      |

|              | 4.4   | Saturation and integration anti-windup                     |      |

|              | 4.5   | Stability analysis                                         |      |

|              |       | 4.5.1 Impact of the controllers bandwidth                  |      |

|              |       | 4.5.2 Impact of model parameters                           |      |

|              | 4.6   | Dual Cascade Controller                                    |      |

|              | 4.7   | DC-link model                            | . 73       |

|--------------|-------|------------------------------------------|------------|

|              | 4.8   | Conclusions                              | . 74       |

| 5            | Sim   | ulation Results                          | <b>7</b> 5 |

|              | 5.1   | Introduction                             | . 75       |

|              | 5.2   | Mitigation of symmetrical voltage dips   | . 75       |

|              | 5.3   | Mitigation Improvement                   | . 80       |

|              | 5.4   | Mitigation of unsymmetrical voltage dips | . 89       |

|              | 5.5   | Induction machine load                   | . 94       |

|              | 5.6   | Conclusions                              | . 100      |

| 6            | Con   | nclusions                                | 101        |

| Re           | efere | nces                                     | 103        |

| $\mathbf{A}$ | Tra   | nsformation for three-phase systems      | 107        |

|              |       | Transformation to fixed coordinates      | . 107      |

|              | A.2   | Transformation to synchronous coordinate | . 109      |

| В            | Nor   | emalized (Per-Unit) Values               | 113        |

|              |       |                                          |            |

# Chapter 1

### Introduction

#### 1.1 Background and motivation

Power quality phenomena include all possible situations in which the waveform of the supply voltage or load current deviate from the sinusoidal waveform at rated frequency with amplitude corresponding to the rated rms value for all three phases of a three-phase system. But poor quality of the current taken by many customers together will ultimately result in low quality of the power delivered to other customers: e.g. both harmonics and unbalanced currents ultimately cause distortion and, respectively, unbalance in the voltage as well. [1]

Among power quality problems voltage dips are one of most important. Voltage dips are sudden drops in voltage with duration between half a cycle and some seconds, mainly caused by short circuits and starting of large motors. The interest in voltage dips is due to the problems they cause on several types of equipment. As an example adjustable-speed drives, process-control equipment, and computers are especially notorious for their sensitivity. Some pieces of equipment trip when the rms voltage drops below 90% for longer than one or two cycles. Such a pieces of equipment might trip tens of times a year. The cost to US industry of voltage dips is estimated to be 10 billion US\$ per year. The cost of a single severe voltage dip to one semiconductor manufacturer in Singapore is estimated to be 1 million Singapore\$ per event. [2]

Voltage dips at equipment terminal can be due to short-circuit faults hundreds of kilometers away in the transmission system. To solve this problem, several different Custom Power devices have been proposed. The term Custom Power has been defined as "the concept of employing power electronic (static) controllers in 1 kV through 38 kV distribution systems for the purpose of supplying a compatible level of power quality necessary for adequate performance of selected facilities and processes". A "Custom Power Controller" is thus defined, accordingly, as "an active power electronic switch or inverter with the ability to perform current interruption and voltage regulating functions in the distribution system to improve power quality".

Many of which have at their heart a Voltage Source Converter (VSC) connected to the grid. Voltage dips can be mitigated by injecting a controllable current into the grid with a shunt-connected VSC. This device is called distribution STATCOM or D-STATCOM. If a D-STATCOM is equipped with an energy storage, the system is also called Energy Storage Equipment STATCOM (E-STATCOM). The E-STATCOM is used as active filter and voltage regulation.

By injecting a current in the point of connection, a shunt-connected VSC can also boost the voltage in that point during a voltage dip. The VSC must be controlled properly to inject the necessary current into the grid in order to compensate for the voltage dip. Since some sensitive loads can shut down because of a dip that lasts some hundreds of ms, the speed of response of the device is a decisive factor for successful compensation. Moreover, most voltage dips are unbalanced, and therefore another requirement for successful dip compensation is a fast detection of the grid voltage unbalance and a high-performance control of the VSC [3].

#### 1.2 Aim and outline of this thesis

The aim of this thesis is to improve, analyze and test, via simulation, control algorithms for shunt-connected VSC, for mitigation of balanced and unbalanced voltage dips. The first part of this work has a focus on power quality problems and in particular on voltage dip, and its main mitigation methods. In the second part a detailed analysis of shunt-connected VSC will be carried out. In Chapter 4 the control system for shunt-connected VSC will be derived, both for balanced and unbalanced conditions. In Chapter 5, the control system will be tested in order to mitigate balanced and unbalanced voltage dips for different kinds of load.

# Chapter 2

## Power Quality and Custom Power

#### 2.1 Introduction

Even a few years back, the main concern for customer was the reliability of electric power supply. Here we indicate as reliability the continuity of electric supply. It is not only reliability that the consumers wants these days, quality is also very important. Both electric utilities and consumers are becoming increasingly concerned about the quality of electric power. For example, a consumer that is connected to the same bus that supplies a large motor load may have to face a severe dip in his supply voltage every time the motor load is switched on. This may be unacceptable to most customers. There are also very sensitive loads such as hospitals, processing plants, air traffic control, financial institutions and numerous other data processing and service providers that required clean and uninterrupted power. In several processes such as semiconductor manufacturing or food processing plants, a batch of product can be ruined by a voltage dip of very short duration. Such customers are very concern of such dips since each event will result in an economical loss.

There are three major reasons for the increased concern on power quality [4]:

- Newer-generation load equipment, with microprocessor-based controls and power electronic devices, is more sensitive to power quality variations than was equipment used in the past.

- The increasing emphasis on overall power system efficiency has resulted in continued growth in the application of devices such high-efficiency, adjustable-speed motor drives and shunt capacitors for power factor correction to reduces losses. This is resulting in increasing harmonic levels on power systems and has many people concerned about the future impact on system capabilities.

- End-users have an increased awareness of power quality issues. Utility customers are becoming better informed about such issues as interruptions, dips, harmonics and switching transients and are challenging the utilities to improve the quality of power delivered.

The reason for the increased interest in power quality can be summarized as follows [5]:

- Metering: Poor power quality can affect the accuracy of utility metering.

- **Protective relays:** Poor power quality can cause protective relays to malfunction.

- **Downtime:** Poor power quality can result in increased costs due to the preceding effects.

- Electromagnetic compatibility: Poor power quality can result in problems with electromagnetic compatibility and noise.

#### 2.2 Characterization of electric power quality

The term electric power quality broadly refers to maintaining a near sinusoidal power distribution bus voltage at rated magnitude and frequency. In addition, the energy supplied to a customers must be uninterrupted from the reliability point of view.

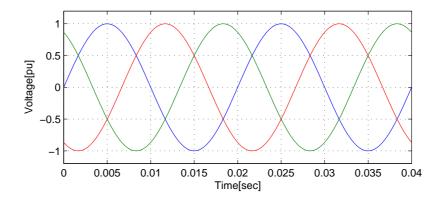

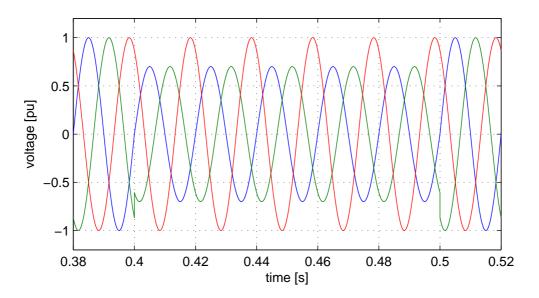

Ideal power quality for the source of energy to an electrical load is represented by the three-phase waveforms of voltage shown in Figure 2.1. The amplitude, frequency, and any distortion of the waveforms must remain within prescribed limits. When the voltages shown in Figure 2.1 is applied to electrical loads, the load currents will have frequency and amplitudes dependent on the impedance or other characteristics of the load. If the waveform of the load current is also sinusoidal, the load is termed "linear". If the waveform of the load current is distorted, the load is termed "nonlinear". The load current with distorted waveform can produce distortion of the voltage in supply system, which is an indication of poor power quality [5].

Most PQ problems occur in distribution systems. In most metropolitan cities, the distribution feeders run underground in the central business districts. In most other places, the feeders run overhead. As a result these lines can easily come in contact with trees. Furthermore, they are likely to be hit by lightning or suffer from interference from birds and smaller animals, causing arching, momentary transients in voltages or voltage dip/swell.

A single customer can impose its harmonics and the effect of unbalanced loads on other customers. Furthermore, switching on of a large induction motor can cause a large inrush current to flow in that circuit causing a voltage dip in other parts of the system. Based on the above discussions, we can summarize that there are two different categories of causes for the deterioration in PQ [2]. The first category contains natural causes such as

- Faults or lighting strikes on distribution feeder.

- Falling of trees or branches on distribution feeders during stormy conditions.

• Equipment failure.

The second category contains the man made causes that may be due to load or feeder line operation. Some of these causes are

- Transformer energization, capacitor or feeder switching.

- Power electronic loads, adjustable speed drives (ASD) etc.

- Arc furnaces and induction heating systems.

- Switching on or off of large loads.

Figure 2.1: Ideal three-phase voltage waveform.

The PQ standards vary among countries. However, it is needless to say that poor quality affects almost all consumers. It is therefore important to list the terms and definitions that are used with power quality. In particular, we shall consider the following

- Transients A transient is that part of change in a system variable that disappears during transition from one steady-state operating condition to another. Transients can be classified into two categories: impulsive transients and oscillatory transients. According to IEEE Std.1159-1995 [6], an impulse transients is a sudden non-power frequency change in the steady-state condition of voltage or current that is unidirectional in polarity (primarily either positive or negative) while, an oscillatory transient is a sudden, non-power frequency change in the steady-state condition of voltage or current that includes both positive or negative polarity value.

- Short duration voltage variations Any variation in the supply voltage for duration not exceeding one minute is called a short duration voltage variation. Usually such variations are caused by faults, energization of large loads that require large inrush currents and intermittent loose connection in the power wiring. Short duration variations are further classified as voltage dips, voltage swells and interruptions. According to IEEE Std.1159-1995 [6], a voltage dip

is defined as a decrease between 0.1 to 0.9 pu in the RMS voltage at the power frequency with duration from 0.5 cycles to 1 minute. Voltage swells are defined as the increase of a fundamental frequency voltage for a short duration. Voltage swells are not as common as voltage dips. An interruption occurs when the supply voltage decreases to less then 0.1 per unit for a period of time not exceeding 1 minute.

- Long duration voltage variations These are defined as the rms variations in the supply voltage at fundamental frequency for periods exceeding 1 minute. These variations are classified into over-voltages, under-voltages and sustained interruptions. An over-voltage (or under-voltage) is a 10% or more increase (or decrease) in rms voltage for more than 1 minute. When the supply voltage is zero for a period of time in excess 1 minute, the long duration voltage variation is called sustained interruption.

- Voltage unbalance This is the condition in which the voltages of the three phases of the supply are not equal in magnitude. Furthermore, they may not even be equally displaced in time. Severe unbalance (grater than 5%) can result during single phasing conditions when the protection opens up one phase of a three-phases supply.

- Waveform distortions This is the steady-state deviation in the voltage or current waveform from an ideal sine wave. These distortions are classified as DC offset, harmonics and notching. The presence of a load drawing DC current results in a DC component of the current in the secondary of a distribution transformer. This current will cause a DC bias in the sinusoidal flux of a transformer core. This increased peak value of the flux may push the transformer towards saturation.

Power electronic loads like UPS, adjustable speed drives etc usually cause harmonics in power system. A measure of harmonic content in a signal is the total harmonic distortion (THD). The percentage THD in a voltage is given by

$$THD[\%] = \frac{\sqrt{\sum_{n=2}^{\infty} V_n^2}}{V_1} \cdot 100 \tag{2.1}$$

where  $V_n$  denotes the magnitude of the  $n^{th}$  harmonic voltage and  $V_1$  is the magnitude of the fundamental voltage.

Notching is a periodic voltage distortion due to operation of power electronic converts when current commutates from one phase to other. During this period there is a momentary short circuit between the two phases that distorts voltages. The maximum voltage during notches depends on the system impedance.

• Voltage fluctuations These are systematic random variations in supply voltages. A modulation of the amplitude in the supply voltage is called voltage

flicker. This is caused by rapid variations in current magnitude of loads such as arc furnaces.

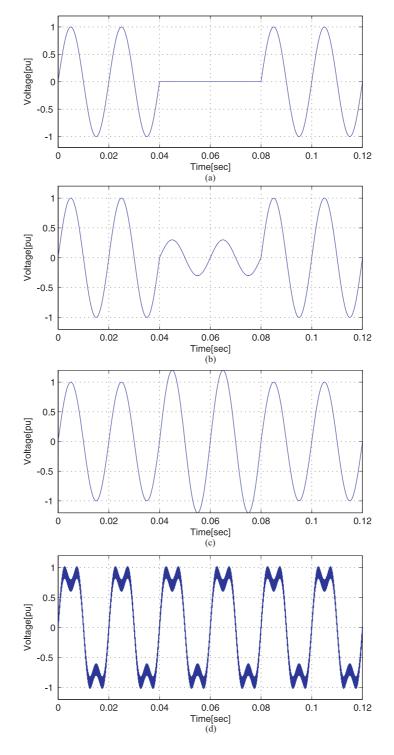

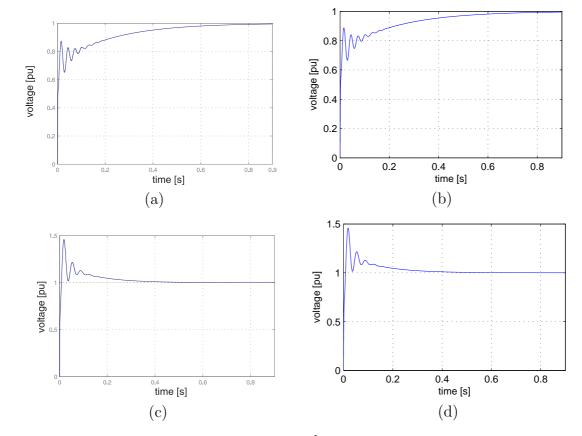

Figure 2.2 shows a typical power disturbance.

Figure 2.2: Typical power disturbances. (a)Interruption, (b)Dip, (c)Swell and (d)Harmonics

Following table reports a summary of PQ problems and their causes  $\left[2\right]$

Table 1.1 Power quality problems and their causes

| Broad                            | Specific                | Methods of                                    | Typical Causes                                           |

|----------------------------------|-------------------------|-----------------------------------------------|----------------------------------------------------------|

| Categories                       | Categories              | Characterization                              |                                                          |

| Transients                       | Impulsive               | Peak magnitude, rise time and duration        | Lightning strike, transformer energization, capacitor    |

|                                  | Oscillatory             | Peak magnitude, frequency components          | Line or capacitor or load switching                      |

| Short duration voltage variation | Sag                     | Magnitude, duration                           | Ferro-resonant transformer, single line-to-ground faults |

|                                  | Swell                   | Magnitude, duration                           | Ferro-resonant transformer, single line-toground faults  |

|                                  | Interruption            | Duration                                      | Temporary (Self-clearing) faults                         |

| Long duration voltage variation  | Under-voltage           | Magnitude, duration                           | Switching on loads, capacitor de-energization            |

|                                  | Over-voltage            | Magnitude, duration                           | Switching off loads, capacitor energization              |

|                                  | Sustained interruptions | Duration                                      | Faults                                                   |

| Voltage un-<br>balance           |                         | Symmetrical components                        | Single-phase loads, single-phasing condition             |

| Waveform distortion              | Harmonics               | THD, Harmonic spectrum                        | Adjustable speed drives and other non-linear loads       |

|                                  | Notching                | THD, Harmonic spectrum                        | Power electronic converters                              |

|                                  | DC offset               | Volts, Amps                                   | Geo-magnetic disturbance, half-wave rectification        |

| Voltage<br>flicker               |                         | Frequency of occurrence, modulating frequency | Arc furnace, arc lamps                                   |

#### 2.3 Power Quality Problems

Of the term and definitions of PQ that are listed in the previous section, some of the major concerns of both customers and utility are

- Poor load power factor Consider a distribution system in which a source is supplying an inductive load through a feeder. The feeder has a resistance of  $R_s$  and a reactance of  $X_s$ . The feeder current is denoted by  $I_s$ , the voltage is denoted by  $V_l$  and the power factor angle is denoted by  $\theta_l$ . Now suppose the load power factor is poor,i.e., the load has a large X/R ratio. Then the load angle will be large. This implies that the reactive component of the current is large and hence the magnitude of the load current is also large. This will not be only cause a significant drop in the feeder voltage but there will also be a large decreasing of the active power for the load. Therefore, to operate the feeder in an optimal condition, the power factor at the load should be maintained near unity. In a ideal situation, the load power factor should be unity. However this may always not be achievable.

- Harmonic contents in loads Power electronic loads are the major source of harmonic generation in power system. Consider an example where a new main frame computer system has been installed in a multistoried office building. At the same time, to protect the computer, a very large uninterrupted supply (UPS) has also been installed. The UPS employs power electronic switches and as a result in can cause interferance to the loads that are connected in parallel with the UPS. Assuming that all the loads of a office building are placed on the same bus and that the AC filter of the UPS is not adequate, the UPS can cause screens of many smaller computer to flicker or roll and can even cause these computers to freeze. It can also cause other electronic circuits to malfunction. For example, it can change the timing sequence of the elevator control circuit.

- Notching in load voltages With rectifier loads there are commutation periods where the line to line voltage falls o zero. This effect is due to the finite inductance in the supply. Thus this causes a finite time for the current to fall to zero in one phase and transfer to another.

- DC offset in load voltages There are two main implications of the presence of a DC current in an electricity supply system. Usually at distribution level, a supply voltage system is equipped with a transformer that changes the voltage levels in accordance with the need of the consumers. It was mentioned earlier that a DC current can offset the flux excursions in a distribution transformer. As a result the magnetic core of a transformer gets heavily saturated resulting in excessive heating and distortion. The other aspect of DC current is the earth path. The return path for a DC current can often involve current through the earth. This will sometimes involve the DC current passing through buried structures such as pipes or reinforced steel. The DC current greatly enhances corrosion of metallic structures as it carries the metallic ions in the direction of the current flow.

- Unbalanced loads An unbalanced load produces the voltage unbalance. The larger the unbalanced current, the larger is the unbalance. The voltage unbalance can be decomposed into a positive sequence voltage, negative sequence and zero sequence voltage. This results in a torque reduction and in a vibration at the shaft.

- Disturbance in Supply Voltage As we have discussed before there can be various form of a disturbances in supply voltage such as interruption, distortion, over-voltage/under-voltage, dip/swell, flicker etc. These can have an adverse impact on the customers. For example, even small duration voltage interruption can cause relay tripping, thereby completely stopping a process line. Even a short duration outage can cause defects in the process. A few cycle voltage dip can force motors to stop thereby running a process.

# 2.4 Power Electronic Application in Power Distribution Systems

Custom power provides an integrated solution to the present problems that are faced by the customers and power distributors. Through this technology the reliability of the power delivered can be improved. The custom power devices are basically of two types: reconfiguring type and compensating type. The network reconfiguring equipment can be GTO based or thyristor based. They are usually used for fast current limiting and current braking during faults. They can also prompt a fast load transfer to an alternate feeder to protect a load from voltage dip/swell or fault in the supplying feeder. The following devices are members of the family of network reconfiguring devices [2]

• Solid State Current Limiter (SSCL) This is a GTO based device that inserts a fault current limiting inductor in series with the faulted circuit as soon the fault is detected. The inductor is removed from the circuit once the fault is cleared. The following figure shown a schematic diagram of SSCL

Figure 2.3: Schematic diagram of a SSCL.

• Solid State Circuit Breaker (SSCB) This device can interrupt a fault current very rapidly and can also perform auto-reclosing function. It has almost the same topology as that of an SSCL except that the limiting inductor

iss connected is series with an opposite poled thyristor pair. This device, based on a combination of GTO and thyristor switches, is much faster than its mechanical counterpart.

• Solid State Transfer Switch (SSTS) This is usually a thyristor based device that is used to protect sensitive loads from dip/swell. It can perform a sub-cycle transfer of the sensitive load from a supplying feeder to an alternate feeder when a voltage dip/swell is detected in the supplying feeder. An SSTS can also be connected as a bus coupler between two incoming feeder. The following figure shown a schematic diagram of SSTS

Figure 2.4: Schematic diagram of a SSTS.

The compensating devices are used for active filtering, load balancing, power factor correction and voltage regulation. The active filters, which eliminate the harmonic currents, can be connected in shunt. The active filters, which eliminate the harmonic voltages, can be connected in series. Some of these devices are used as load compensator, in this mode they correct the unbalance and distortions in the load currents such that compensated load draws a balanced sinusoidal current from the AC system. Some other are operated to provide balanced, harmonic free voltage to the customers. The family of compensating devices has following members

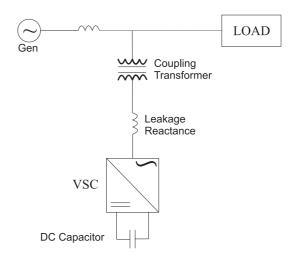

• **D-STATCOM** This is a shunt-connected VSC which structure is shown in the following figure. This can perform load compensation, power factor correction, harmonic filtering, etc. when connected at the load terminals.

Figure 2.5: A D-STATCOM connected to a power system.

It can also perform voltage regulation when connected to a distribution bus. In this way it can keep the bus voltage constant against any unbalance or distortion in the distribution system. D-STATCOM is derived from STATCOM used in the transmission system; they have a similar structure. D-STATCOM must be able also to inject a unbalanced and harmonically distorted current to eliminate unbalance or distortions in the load current or the supply voltage.

• Dynamic Voltage Restorer (DVR) This is a series-connected VSC (also called Static Series Compensator (SSC)) which structure is shown in Figure 2.6.

The main purpose of this device is to protect sensitive load from dip/swell. This is accomplished by rapid series voltage injection to compensate for the drop/rise in the supply voltage. Since this series device, it can also be used as a series active filter. The DVR may have to inject unbalanced voltages to maintain the voltage at the load terminal in case of an unbalanced dip in the supply side. Furthermore when there is a distortion in the source voltage, the DVR may also have to inject a distorted voltage to counteract the harmonic voltage.

Figure 2.6: A DVR connected to a power system.

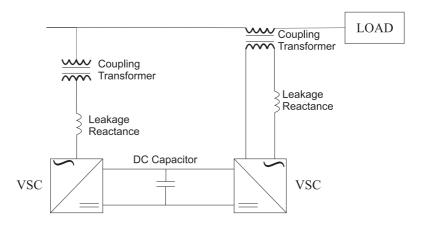

• Unified Power Quality Conditioner (UPQC) This is a very versatile device that can inject current in shunt and voltage in series simultaneously in a dual control mode (see Figure 2.7). Therefore it can perform both the functions of load compensation and voltage control at the same time. As in the case of D-STATCOM or DVR, the UPQC must also inject unbalanced and distorted voltages and currents.

Figure 2.7: Schematic diagram of a UPQC

#### 2.5 Conclusions

In this chapter a small description about power quality problems has been carried out. Moreovea small introduction about power electronic applications in power distribution systems has been presented. This work will focus on voltage dips mitigation through a shunt-connected VSC converter. The next chapter will present an overview of voltage dips and different solutions for voltage dip mitigation.

# Chapter 3

# Voltage Dips and Mitigation Methods

Power quality and reliability are essential for proper operation of industrial processes that involve critical and sensitive loads. Short-duration power disturbances, such as voltage dips, swells and short interruptions, are major concerns for industrial customers.

Due to wide usage of sensitive electronic equipment in process automation, even voltage dips which last for only few hundreds of milliseconds way cause production stops with considerable associated costs; these costs include production losses, equipment restarting, damaged or low-quality product and reduced customer satisfaction.

The high costs associated with these disturbances explain the increasing interest towards voltage dip mitigation methods. The cost of the mitigation intervention has to be compared with the loss of revenue and takes into account all economic factors involved.

This chapter will present an overview of voltage dips and different solutions for voltage dip mitigation, like power system improvements, load immunity and installation of mitigation devices will be treated.

#### 3.1 Analysis of voltage dip

According to IEEE Std.1159-1995, a voltage dip is defined as a decrease between 0.1 to 0.9 pu in the RMS voltage at the power frequency with duration from 0.5 cycles to 1 minute. Typically the dip is characterized through the remaining voltage during the event. This is then given as a percentage of the nominal voltage. Thus, a 70% dip in a 230 V system means that the voltage dropped to 161 V. As mentioned in the previous chapter, a voltage dip can be caused by different events that can occur in the power system like transformer energizing, switching of capacitor banks, starting of large induction motors and short-circuit faults in the transmission and

distribution system. In this report, only voltage dips due to short-circuit will be considered [3].

Faults on the feeder can be initiated by [2]

- Lightning strike.

- Tree or branches falling on conductors.

- Animals across lines.

- Wind causing conductors to clash together.

- Digging equipment breaking cables.

The statistic of overhead lines indicate that

- 70% of the faults are single line to ground.

- 15% of the faults are double line to ground.

- 10% of the faults are line to line.

- 5% of the faults are three phase faults.

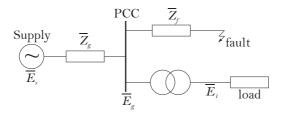

To quantify the dip magnitude in radial systems, the voltage divider model, shown in Figure 3.1 can be used, where  $Z_g$  is the grid impedance and  $Z_f$  is the fault impedance between the point of common coupling (PCC) and the fault [3]. The PCC is the point from which both the fault and the load are fed.

Figure 3.1: Single-line diagram to display voltage division during voltage dips.

The voltage at the PCC is found from:

$$\overline{E}_g = \frac{\overline{Z}_f}{\overline{Z}_f + \overline{Z}_g} \overline{E}_s \tag{3.1}$$

From (3.1) it is possible to observe that the voltage dip magnitude depends on the fault location (since the impedance on the distance between the point in the power system where the fault occurs and the PCC) and the grid impedance. This equation can be used to calculate the dip magnitude as a function of the distance to the fault.

Therefore, if  $Z_f = zd$ , with z the impedance of the feeder per unit length and d the distance between the fault and the PCC, leading to [7]:

$$\overline{E}_g = \frac{zd}{zd + \overline{Z}_g} \overline{E}_s \tag{3.2}$$

From this equation we can obtain the distance at which a fault will lead to a dip of a certain magnitude E. If we assume equal X/R ratio of source and feeder, we get the following equation:

$$d_{crit} = \frac{\overline{Z}_g}{z} \times \frac{E}{1 - E} \tag{3.3}$$

This distance is often called "critical distance". Suppose that a piece of equipment trips when the voltage drops below a certain level(the critical voltage). The definition of critical distance is such that each fault within the critical distance will cause the equipment to trip. The critical distance has been calculated for different voltage levels, using typical fault levels and feeder impedances. The data used and the results obtained are summarize in Table 3.1 for the critical voltage of 50%. Note how the critical distance increases for higher voltage levels. A customer will be exposed to much more kilometres of transmission lines than of distribution feeder [7].

Nominal Voltage Short-Circuit Level Feeder Impedance Critical Distance  $400 \ V$ 20 MVA $230 \ m\Omega/km$ 35 m $11 \ kV$ 200~MVA $310 \ m\Omega/km$  $2 \ km$  $33 \ kV$ 900 MVA  $340 \ m\Omega/km$  $4 \ km$  $132 \ kV$ 3000~MVA $450 \ m\Omega/km$  $13 \ km$  $400 \ kV$ 10000~MVA $290 \ m\Omega/km$  $55 \ km$

Table 3.1 Critical distance for faults at different voltage levels

A short circuit in the power system not only causes a drop in a voltage magnitude, but also change in the phase angle of the voltage. This sudden change in phase angle is called a "phase-angle jump". The phase-angle jump is visible in the time-domain plot of the dip as a shift in voltage zero-crossing between the pre-event and the during-event voltage. With reference to Figure 3.1 and (3.1), the phase-angle jump is the argument of  $\overline{E}_g$ , thus the difference in argument between  $Z_f$  and  $Z_g + Z_f$ . If impedances  $Z_g$  and  $Z_f$  have equal X/R ratio, there will be no phase-angle jump in the voltage at PCC. The phase-angle jump is given by

$$\psi = \arg(\overline{E}_g) = \arctan\left(\frac{X_f}{R_f}\right) - \arctan\left(\frac{X_f + X_g}{R_f + R_f}\right)$$

(3.4)

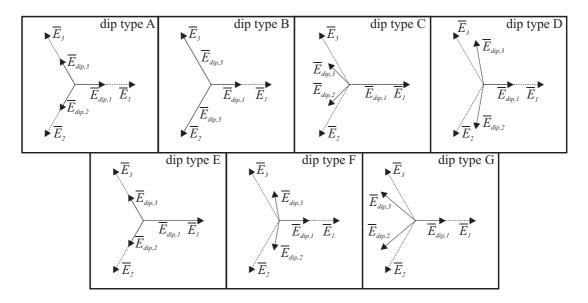

Depending on the type of fault (three-phase, phase-to-phase with or without ground involved, single-phase to ground), the resulting voltage dip at the PCC can be one of six types reported in Figure 3.2 [8].

Figure 3.2: Voltage dip classification "A" to "G". Phasors three-phase voltage before (dotted) and during fault (solid) are displayed.

The load is usually supplied through a distribution transformer, connected in  $\Delta/Y$ . The transformer swaps the phases and removes the zero-sequence component because of the delta connection. This results in a transformation of the dip characteristic as listed in Table 3.1 (right column). It can be concluded that voltage dips that affect the load downstream a  $\Delta/Y$ -transformer can only be of type A, C, D and F. The voltage dip type A is a drop in a voltage in all three phase (balanced dip). The voltage dip type C is characterized by a drop in two phases with the third phase voltage almost undisturbed. The voltage dip type D is characterized by a larger drop in one phase and smaller drops in the other two phases. The voltage dip type F is in fact a particular case of type C and D [9]. However, in some applications, such as control of VSC connected to the grid, it can be preferable to characterize the voltage dip in terms of the remaining positive-sequence voltage and the unbalance, expressed as magnitude of negative-sequence voltage in percentage of the pre-fault voltage [3]. Therefore, this characterization will not be used in this report.

Table 3.1 Voltage dip classification and propagation through  $\Delta/Y$ -transformers.

| Fault          | Dip seen at PCC | Dip seen by the load |

|----------------|-----------------|----------------------|

| 3-phase fault  | Type A          | Type A               |

| 1-phase fault  | Type B          | Type C               |

| 2-phase fault  | Type E          | Type F               |

| phase-to-phase | Type C          | Type D               |

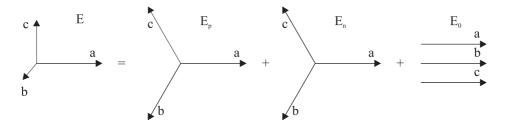

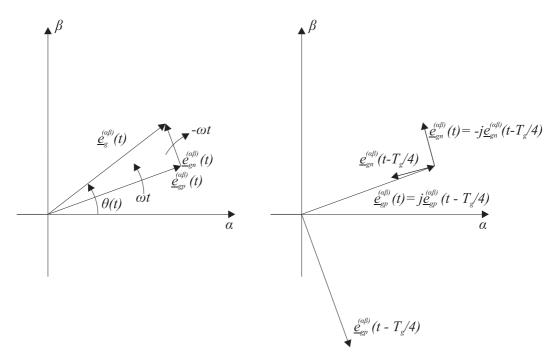

If the voltage amplitude of three phases are unequal, the resulting voltage vector can be expressed as the sum of two vectors interpreted as positive- and negative-sequence component vectors. The magnitude of the positive sequence  $(E_p)$  and the negative sequence  $(E_n)$  of the grid voltage for dip types "A" through "G" are calculated using synchronous coordinate (see Appendix A.) and summarized in Table 3.3, where is the phase-to-phase RMS grid voltage. It shown that dips "C" and "D" have the same positive and negative sequence magnitudes. The same applies

for dips "E", "F" and "G". However they may affect the system in different ways according to Table 3.4, at which the positive and negative sequence components in the dq-coordinate system have been calculated. It shows that dips "C" and "D" result in different negative sequence dq-components. The same also holds for dip types "F" and "G", while dips "E" and "G" are exactly the same since they both result in the same positive and negative sequence components. This classification is useful in understanding the effect of unbalanced voltage dips on the system [10].

Table 3.3 Positive and negative sequence magnitudes of grid voltage for dip types "A" through "G".

| Dip type | $E_p$                                     | $E_n$                                    |

|----------|-------------------------------------------|------------------------------------------|

| A        | $EE_g$                                    | 0                                        |

| В        | $\frac{E}{3}\sqrt{4+4E_g\cos\psi+E_g^2}$  | $\frac{E}{3}\sqrt{1-2E_g\cos\psi+E_g^2}$ |

| C, D     | $\frac{E}{2}\sqrt{1+2E_g\cos\psi+E_g^2}$  | $\frac{E}{2}\sqrt{1-2E_g\cos\psi+E_g^2}$ |

| E, F, G  | $\frac{E}{3}\sqrt{1+4E_g\cos\psi+4E_g^2}$ | $\frac{E}{3}\sqrt{1-2E_g\cos\psi+E_g^2}$ |

Table 3.4 Positive and negative sequence components of grid voltage in dq-coordinates for dip types "A" through "G".

|          | 1                             | 1 / 1                     | 0                                 |                           |

|----------|-------------------------------|---------------------------|-----------------------------------|---------------------------|

| Dip type | $e_{dp}$                      | $e_{qp}$                  | $e_{dn}$                          | $\frac{e_{qn}}{0}$        |

| A        | $EE_g\cos\psi$                | $EE_g\cos\psi$            | $e_{dn}$                          | 0                         |

| В        | $\frac{E}{3}(2+E_g\cos\psi)$  | $\frac{E}{3}E_g\sin\psi$  | $-\frac{E}{3}(1 - E_g \cos \psi)$ | $-\frac{E}{3}E_g\sin\psi$ |

| С        | $\frac{E}{2}(1+E_g\cos\psi)$  | $\frac{E}{2}E_g\sin\psi$  | $\frac{E}{2}(1 - E_g \cos \psi)$  | $\frac{E}{2}E_g\sin\psi$  |

| D        | $\frac{E}{2}(1+E_g\cos\psi)$  | $\frac{E}{2}E_g\sin\psi$  | $-\frac{E}{2}(1-E_g\cos\psi)$     | $-\frac{E}{2}E_g\sin\psi$ |

| E        | $\frac{E}{3}(1+2E_g\cos\psi)$ | $\frac{2E}{3}E_g\sin\psi$ | $\frac{E}{3}(1 - E_g \cos \psi)$  | $\frac{E}{3}E_g\sin\psi$  |

| F        | $\frac{E}{3}(1+2E_g\cos\psi)$ | $\frac{2E}{3}E_g\sin\psi$ | $-\frac{E}{3}(1-E_g\cos\psi)$     | $-\frac{E}{3}E_g\sin\psi$ |

| G        | $\frac{E}{3}(1+2E_g\cos\psi)$ | $\frac{2E}{3}E_g\sin\psi$ | $\frac{E}{3}(1 - E_g \cos \psi)$  | $-\frac{E}{3}E_g\sin\psi$ |

#### 3.2 Voltage dip mitigation

There are various mitigation methods for the voltage dip. Thus we can distinguish three main categories:

- Power System Improvements

- Increasing Equipment Immunity

- Mitigation Devices

#### 3.2.1 Power System Improvements

Power system improvements include the mitigation through intervention on the power system, considering both changes in the electrical components of the system and in its structure.

Reducing the number of faults Reducing the number of short-circuits in a system not only reduces the dip frequency, but also the frequency of long interruptions. This is thus a very effective way of improving the quality of the supply and many customers suggest this as the obvious solution when a voltage dip problem occurs [7]. Fault prevention actions may include the institution of tree trimming policies, the addition of lightning arresters, insulator washing and the addition of animal guards. Insulation on transmission systems cannot withstand the most severe lightning strokes, but lines which are often subject to lightning-induced faults should be carefully investigated for improvement of the insulation level. Faults due to lightning can be reduced by lowering the ground resistance at the foot of the tower for overhead static wires. Other measures include the use of recently introduced special wires, which are covered by a thin layer of insulation material, or the installation of additional shielding wires, placed in such a way that they are more likely to be hit by a lightning stroke than the phase conductors. A considerable reduction in the number of faults per year can otherwise be achieved by replacing overhead lines by underground cables, which are less affected by adverse weather. The fault rate of an overhead line is much higher than that of an underground cable, but in case of fault the repair time of the latter is longer [11].

Changing the power system By implementing changes in the supply system, the severity of the event can be reduced. However, the costs may become very high, especially for transmission and subtransmission voltage levels. In industrial systems, such improvements more often outweigh the costs, especially when already included in the design stage. Some examples of mitigation methods are given in [7]. Other improvements in the power system design include:

• Install a generator near the sensitive load. The generators will keep up the voltage during a dip. The reduction in voltage drop is equal to the percentage contribution of the generator station to the fault current.

- Split buses or substations in the supply path to limit the number of feeders in the exposed area.

- Install current-limiting coils at strategic places in the system to increase the electrical distance to the fault. The drawback for this method is that this may make the event worse for other customers.

- Feed the bus with sensitive equipment from two or more substations. A voltage dip in one substation will be mitigated by the in feed from the other substations. The more independent the substations are, the more mitigation effect.

Reducing the fault-clearing time Reducing the fault clearing time does not reduce the depth of the dips, but only their duration. The ultimate reduction of fault clearing time is achieved by using current-limiting fuses or modern static circuit breakers, able to clear a fault within half-cycle. Additionally, several types of fault-current limiters have been proposed that do not actually clear the fault, but significantly reduce the fault current magnitude within one or two-cycles. One important restriction of all these devices is that they can only be used for lowand medium-voltage levels systems. The maximum operating voltage is a few tens of kilovolts [7]. The fault-clearing time is not only the time needed to open the breaker, but also the time needed for the protection to make a decision. To achieve a proper reduction in fault-clearing time, it is necessary to reduce any grading margins, thereby possible allowing for a certain loss of selectivity. Some caution has to be taken, however, when applying these new protection devices in existing distribution systems. If only some of the protective devices were replaced with fast acting breakers, it would not be possible to co-ordinate them with previously existing downstream protective devices [11].

#### 3.2.2 Increasing Equipment Immunity

Case studies and power quality surveys show that sensitive equipment include both low-power electronics (computers, process-control devices, consumers-electronics) and high-power electronics (for AC and DC drives). It has been reported that an installation using only electromechanical control could tolerate a dip down to 60% voltage without problems, while a completely automated factory could be disrupted by a dip to 85% [11]. Improvement of equipment voltage tolerance thresholds appears at the most effective solution against voltage dips in the long term. This is especially true for short-duration and shallow dips which can hardly be mitigated by means of the utility-side solutions. Unfortunately, customers can only require a specific voltage tolerance level for very large industrial equipment, and these are usually tailored for specific applications. In most cases, the customer has no direct contact with the manufacturer and can in no way intervene to modify equipment sensitivity to voltage disturbances [11].

#### 3.2.3 Mitigation Devices

Customer solutions usually involve power conditioning for sensitive loads. Different devices are currently available for the mitigation of power quality problems. The installation of these devices is getting more and more popular among industrial customers due to the fact that it is that only place where the customers has control over the situation. There are several methods that can be used.

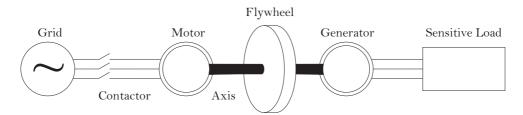

Motor-generator sets Motor-generator sets stores energy in a flywheel. It consists of a motor supplied by the grid, a synchronous generator supplying the load and the flywheel, all connected to the common axis (as shown in Figure 3.3). The rotational energy stored in the flywheel can be used to perform steady-state voltage regulation and to support voltage during disturbances. This system has high efficiency, low initial costs and enables long-duration ride through (several seconds) but can only be used in industrial environments, due to its size, noise and maintenance requirements [11].

Figure 3.3: Three-phase diagram of motor-generator set with flywheel to mitigate voltage dips.

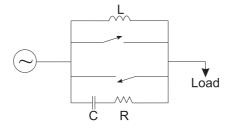

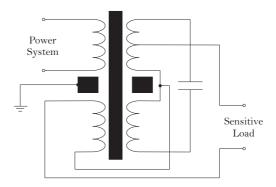

Transformer-based mitigation devices A Constant Voltage, or ferro-resonant, Transformer (CVT) works in a similar manner to a transformer with a 1:1 turns ratio which is excited at a high point on its saturation curve, thus providing an output voltage which is not affected by input voltage variations. In the actual design, as shown in Figure 3.4, a capacitor is needed to set the operating point above the knee of saturation curve during normal operation. This solution is suitable for low-power, constant loads: variable loads can cause problems, due to the presence of this tuned circuit on the output.

Figure 3.4: Typical circuit for a ferro-resonant transformer.

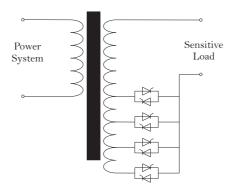

Electronic tap changers (Figure 3.5) can be mounted on a dedicated transformer for the sensitive load, in order to change its turns ratio according to change in the input voltage. They can be connected in series the distribution feeder and placed between the supply and the load. Part of the secondary winding supplying the load is divided into a number of sections, which are connected or disconnected by fast static switches, thus allowing regulation of the secondary voltage in steps. This should allow the output voltage to be brought back to a level above 90% of the nominal value, even for severe voltage dips. Thyristor-based switches which can only be turned on once per cycle are used, therefore the compensation is accomplished with a time delay of at least one half cycle.

Figure 3.5: Transformer with electronic tap changers.

Autotransformer Switched by Hysteresis Voltage Control AC converters consist of two solid-state switches per phase and require reactive elements such as a capacitor and an inductor. Since the current in the AC converters flows in both directions, static switches and diodes are serially connected to allow both directions current. A new compensation scheme with a new control method is used [12]. The scheme configuration is shown in Figure 3.6. In this configuration an autotransformer is used as a boosting transformer instead of a two-winding transformer. The autotransformer does not offer electrical isolation between primary side and secondary side but has advantages of high efficiency with small volume.

This voltage dip supporter works for only a few seconds and remains in the offstate most of its operation time. Since the switch remains in the off-state for most of the time and must withstand the voltage across it. Therefore, the voltage across the switch becomes an important factor. The voltage across the switch in the offstate is equal to one half of the input voltage.

The model consists of the single IGBT switch in a bridge configuration, a thyristor bypass switch, output filters, an autotransformer, and the system controller. In normal conditions, the IGBT switch is off and the power flows through anti-parallel thyristor as a bypass switch. This bypass switch connects the input power to the load unless the dip condition is present. When voltage dip occurs, the bypass switch turns off and the switching command turns on the IGBT switch. Utilizing autotransformer, the IGBT improves the output voltage in such a way that the voltage

Control Block

Reference Voltage

Bypass switch

Switching

Command

L

O

Load Voltage

across the load remains constant.

Input Voltage

Figure 3.6: Overall structure of voltage dip compensator.

To prevent the switching noise effect of IGBT and thyristor on the load current and voltage waveforms, two filters (a capacitor filter and a notch filter) utilized. To keep the power switches safe, an RC snubber circuit is designed. The snubber circuit of IGBT switch consists of a resistor and a capacitor. The snubber suppresses the peak voltage across the IGBT switch when the IGBT turns off. When the IGBT switch turns off, the current flowing in the IGBT in the on-state instantly diverts to the snubber circuit. The energy stored in the current path is transferred into the snubber capacitor and resistor.

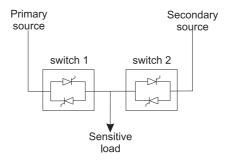

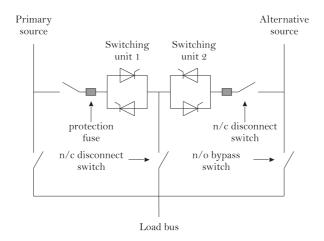

**Static Transfer Switch** The Static Transfer Switch (STS) consists of two three-phase static switches, each constituted in turn of two antiparallel thyristor per phase, as shown in Figure 3.7, where the single-line diagram of an STS is displayed [3]. The usual configuration of the STS, shown in Figure 3.7, consists of [1]:

- two three-phase static switches, each constituted in turn by by two-antiparallel thyristors per phase, which actually perform the fast transfer of power between the two sources;

- two three-phase mechanical bypass switches, which are operated as standard mechanical switches to perform a slower back-up transfer, when the STS cannot operate due to overload conditions or when it is out of service for maintenance or testing;

- isolating switches, needed to disconnect the STS from the distribution system for maintenance and testing.

Figure 3.7: Single-line diagram of Static Transfer Switch (STS).

The STS has to transfer the load from the preferred source to the alternative source automatically and rapidly when a reduced voltage is established in the preferred source and while the alternative source meets certain quality requirements. Formerly available only for low voltages, STS systems are now advertised for higher voltages and protected load ratings, which make them for high-power industrial applications: they would be capable to protect loads up to  $35\ MVA$  supplied at a voltage of  $35\ kV$ . Ratings of a commercial STS are reported in Table  $3.5\ [1]$

| Table 3.5 | Ratings | of | commercial | STS | S | ystem. |

|-----------|---------|----|------------|-----|---|--------|

|           |         |    |            |     |   |        |

| Model     | Voltage   | Continuous     | Power  |

|-----------|-----------|----------------|--------|

|           | Class     | Current Rating |        |

| DSTSIS200 | $15 \ kV$ | $200 \ kA$     | 5~MVA  |

| DSTSIS600 | $15 \ kV$ | $600 \ kA$     | 15~MVA |

| DSTS2S200 | $25 \ kV$ | $200 \ kA$     | 8~MVA  |

| DSTS25600 | $25 \ kV$ | $600 \ kA$     | 26~MVA |

| DSTS35200 | $35 \ kV$ | $200 \ kA$     | 11~MVA |

| DSTS3S600 | $35 \ kV$ | $600 \ kA$     | 35~MVA |

Transfer under normal operating conditions may also be needed in particular cases and must be allowed. However, the need for transfer usually arises because of an upstream fault causing a reduction of the preferred source voltage for a limited time interval, after which the load is switched back to the main supply. It has been observed that, with this arrangement, the load current flows continuously through the thyristors and this causes high losses and heating [13].

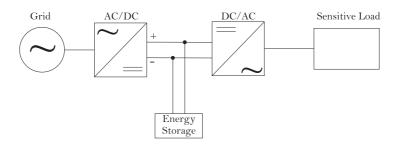

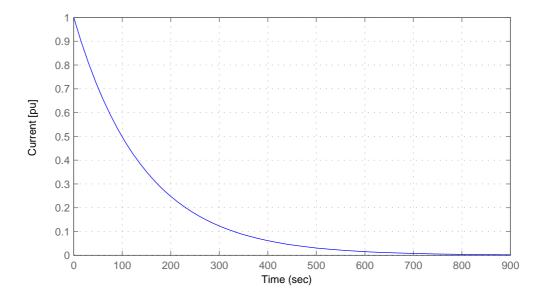

Uninterruptible Power Supply An Uninterruptible Power Supply (UPS) consists of a diode rectifier followed by an inverter, as shown in Figure 3.8 [3] [11]. The energy storage is usually a battery connected to the DC link. During normal operation, the power coming from the AC supply is rectified and then inverted to feed the load. The battery remains in standby mode and only keeps the DC-bus voltage constant. During a voltage dip or an interruption, the energy released by the battery

keeps the voltage at the DC bus constant. Depending on the storage capacity of the battery, it can supply the load for minutes or even hours. Low cost, simple operation and control have made the UPS the standard solution for low-power, single phase equipment, like computers. For higher-power loads the costs associated with losses due to the two conversions and maintenance of the batteries become too high and, therefore, a three-phase, high power UPS is not economically feasible.

Figure 3.8: Single-line diagram of Uninterruptible Power Supply (UPS).

Series-connected VSC The basic idea is to inject a voltage  $\underline{e}_c(t)$  of desired amplitude, frequency and phase between the PCC and the load in series with the grid voltage. A single-phase diagram of the main components of the SSC is depicted in Figure 3.10. The SSC injects by means of three single-phase transformers three voltages in the grid, synchronized in such a way that the load voltage magnitude and phase are constant at any instant to maintain the operation of the load [14].

Figure 3.9: Single-line diagram of SSC.

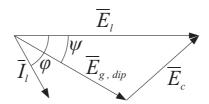

The SSC in mainly used for voltage dip mitigation. The device maintains the load voltage  $\underline{e}_l(t)$  to the pre-fault condition by injecting a voltage of appropriate amplitude and phase. Figure 3.11 shows the phasor diagram of the series injection principle during voltage dip mitigation, where  $\overline{E}_c$  is the phasor of the voltage injected by the compensator,  $\overline{I}_l$  is the phasor of the load current and where  $\varphi$  is the angle displacement between load voltage and current,  $\overline{E}_{g,dip}$  is the grid voltage phasor during the dip and  $\psi$  is the phase angle jump.

Figure 3.10: Mitigation of voltage dips using SSC.

The dynamic performance of the SSC is important to start compensation without a sensible delay. Thus, the response time of the dip detection and voltage compensation must be short; consequently, the bandwidth of the control algorithm should be high.

In the single-line diagram of the SSC, shown in Figure 3.10, the grid voltage, current and angular frequency are denoted by  $\underline{e}_g(t), \underline{i}_g(t)$  and  $\omega$ , respectively.  $R_g$  and  $L_g$  denote the equivalent resistance and inductance of the grid,  $\underline{u}(t)$  and  $\underline{i}_r(t)$  are the voltage and current of the VSC. The load voltage is denoted by  $\underline{e}_l(t)$ . At the point of common coupling (PCC), the SSC is connected to the power system. The LC-filter consists of a series inductor with inductance  $L_f$  and resistance  $R_f$  and a shunt capacitor with capacitance  $C_f$ . The energy storage provides the required power to compensate the identified voltage dip.

In order to be able to restore both magnitude and phase of the load voltage to the pre-fault conditions, the SSC has to inject both active and reactive power [3]. Assuming that the load voltage and the current in pre-fault condition are both equal to 1 pu, the power injected by the device during voltage dip mitigation is equal to

$$\overline{S}_{inj} = \overline{E}_c \overline{I}_l^* = (\overline{E}_l - \overline{E}_{g,dip}) \overline{I}_l^* = (1 - \overline{E}_{g,dip} e^{\jmath \psi}) e^{\jmath \varphi} =$$

$$= \cos \varphi + \jmath \sin \varphi - (E_{g,dip} \cos(\varphi + \psi) + \jmath E_{g,dip} \sin(\varphi + \psi))$$

(3.5)

Observe that the power absorbed by the load is given by

$$\overline{S}_{load} = P_{load} + jQ_{load} = \overline{E}_{l}\overline{I}_{l}^{*} = e^{j\varphi} = \cos\varphi + j\sin\varphi$$

(3.6)

Therefore, the active and reactive power injected by the SSC are given by

$$P_{inj} = \left[1 - \frac{E_{g,dip}\cos(\varphi + \psi)}{\cos\varphi}\right] P_{load}$$

(3.7)

$$Q_{inj} = \left[1 - \frac{E_{g,dip}\sin(\varphi + \psi)}{\sin\varphi}\right]Q_{load}$$

(3.8)

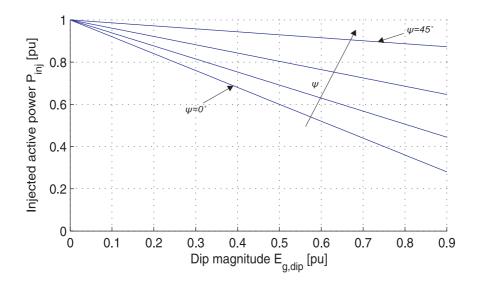

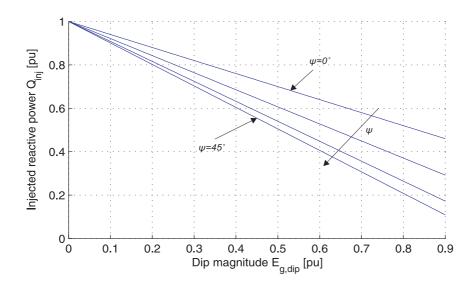

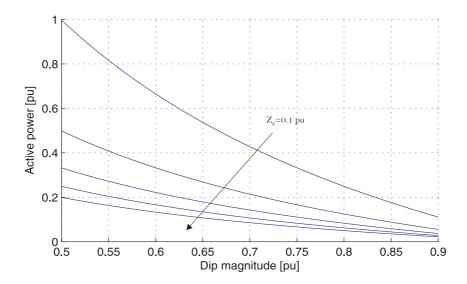

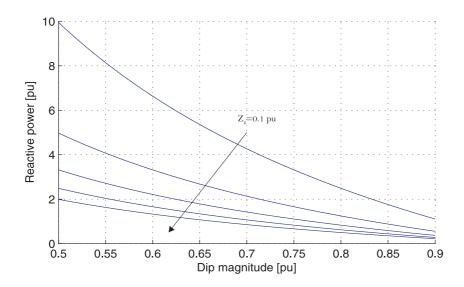

Figure 3.12 and 3.13 display the active and the reactive power injected by the SSC during voltage dip mitigation for different phase-angle jump (0°, 15°, 30°, 45°) under the assumption of load impedance  $\overline{Z}_l$  equal to 1 pu with power factor 0.8 inductive.

Figure 3.11: Active power injected vs. dip magnitude during voltage dip mitigation for different phase-angle jump.

Figure 3.12: Reactive power injected vs. dip magnitude during voltage dip mitigation for different phase-angle jump.

The maximum injected voltage is limited by the size of the converter and the rating of the series transformer. The voltage rating of the converter is chosen on the basis of the maximum dip to compensate for. Existing SSCs are usually sized for 50% maximum voltage injection with duration of 500 ms.

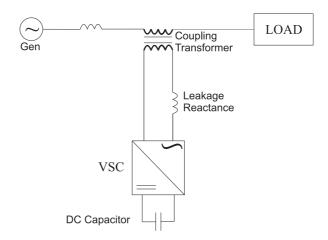

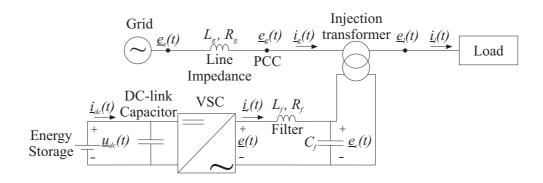

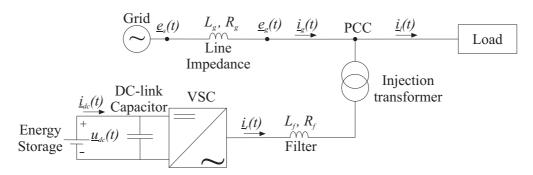

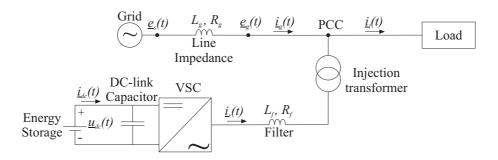

**Shunt-connected VSC** The typical configuration of a shunt-connected VSC with energy storage (as seen also called E-STATCOM) is shown in Figure 3.14. The device consists of a VSC, an injection transformer, an AC filter and a DC-link capacitor.

Figure 3.13: Single-line diagram of shunt-connected VSC.

The grid voltage and current are denoted by  $\underline{e}_s(t)$  and  $\underline{i}_g(t)$ , respectively. The voltage at the point of common coupling (PCC), which is also equal to the load voltage, is denoted by  $\underline{e}_q(t)$  and the load current by  $\underline{i}_l(t)$ .

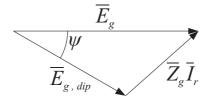

The converter acts as a controllable current source connected in parallel with the load. The system can instantaneously compensate voltage dips by regulating the load voltage using the injected current from the converter and the voltage drop across line inductance, as shown in the phasor diagram in Figure 3.15. The voltage phasor at PCC is denoted by  $\overline{E}_g$ ,  $Z_g$  is the line impedance,  $\overline{E}_{g,dip}$  is the grid voltage phasor during the dip and  $\psi$  is the phase-angle jump of the dip.

Figure 3.14: Mitigation of voltage dips using shunt-connected VSC.

From the diagram it is possible to understand that when the shunt-connected VSC is used to mitigate voltage dips, it is necessary to provide an energy storage for injection of active power in order to avoid phase-angle jumps of the load voltage. If only reactive power is injected, it is possible to maintain the load voltage amplitude  $\overline{E}_g$  to the pre-fault conditions but not its phase. Therefore, the voltage dip mitigation capability of a shunt-connected VSC depends on the rating of the energy storage, on the grid impedance  $Z_g$  and on the rating in current of the VSC. To restore the load voltage to the pre-fault conditions (without introducing phase-jump), the following condition must be fulfilled [3]

$$\overline{E}_g = \overline{E}_{g,dip} + \overline{Z}_g \overline{I}_r \tag{3.9}$$

Observe that if the line impedance is small to achieved the mitigation the current  $\underline{i}_r(t)$  must be big (major cost of the system), instead if the line impedance is big to

achieve the mitigation the current  $\underline{i}_r(t)$  must be small (minor cost of the system). But if the line impedance is big, the voltage at PCC will be more variable with the consequence that the system will be more sensitive by the faults. Active and the reactive power injected by the device can be calculated in per unit as

$$P_{inj} = \frac{\cos \varphi_l}{Z_l} - \frac{E_s(E_{s,dip}\cos(\varphi_g - \varphi_s) - \cos(\varphi_g - \varphi_s + \psi))}{E_{s,dip}Z_g}$$

(3.10)

$$Q_{inj} = -\frac{\sin \varphi_l}{Z_l} + \frac{E_s(E_{s,dip}\sin(\varphi_g - \varphi_s) - \sin(\varphi_g - \varphi_s + \psi))}{E_{s,dip}Z_g}$$

(3.11)

where the source voltage, the load impedance and the line impedance are expressed as  $\overline{E}_s = E_s e^{j\varphi_s}$ ,  $Z_l = Z_l e^{j\varphi_l}$  and  $Z_g = Z_g e^{j\varphi_g}$ , respectively.

Figures 3.16 and 3.17 show the amount of active and reactive power, respectively, injected by the shunt-connected VSC to maintain the voltage at its pre-fault value. In order to compare the SSC and the E-STATCOM, we consider the case of mitigation of voltage dips with magnitude higher than 50% (i.e., the remaining voltage is equal or higher than 50% of the rated voltage). The load impedance  $Z_l$  has been set to 1 pu with power factor of 0.8, while different values for the line impedance  $Z_g$  (from 0.1 pu to 0.5 pu in steps of 0.1 pu) have been considered. For the grid impedance, it has been assumed that  $X_g$ =0.995 $Z_g$  and  $R_g$  = 0.1 $X_g$ , which results in an impedance angle of 84.29°. It is interesting to observe that, since the line impedance is mainly reactive ( $R_g < X_g$ ), the amount of active power injected is significantly smaller than the reactive power. Moreover, the injected power increases for smaller values of the line impedance. This is not surprising, since smaller line impedance means a stronger grid. Thus, it will be necessary to inject a larger amount of current to increase the voltage at the PCC.

As it is possible to observe, the amount of reactive power is bigger than the use of SSC. Actually if the grid impedance is equal to 0.1 pu the amout of reactive power required is not smaller than 1.0 pu.

Figure 3.15: Active power injected by shunt-connected VSC vs. dip magnitude during voltage dip mitigation for different line impedances  $\overline{Z}_g$ .

Figure 3.16: Active power injected by shunt-connected VSC vs. dip magnitude during voltage dip mitigation for different line impedances  $\overline{Z}_g$ .

#### 3.3 Conclusion

In this chapter, a brief overview of voltage dips, with their origin and classification has been given. Different methods for voltage dip mitigation have been described. The installation of mitigation devices at the system-equipment interface appears as the most attractive short-term solution for customers, who rarely have the chance to request either specific tolerance levels for equipment or an improved power supply. A summary of the cost and capability of the most common devices is shown in Table 3.3 [15].

Table 3.3 Comparison of Custom-Power Equipment for Correcting Dips.

| Device                    | Cost, U.S. \$  | Capability     |

|---------------------------|----------------|----------------|

| Shunt-connected VSC       | 50-200 /kVA    | dips to $70\%$ |

| Static transfer switching | 500 - 1000 / A |                |

| Series-connected VSC      | 150-250~kVA    | dips to $50\%$ |

| UPS                       | 750-1500~kVA   |                |

Among the mitigation methods presented, the use of custom power devices seems the most efficient. In particular among the custom power the SSC is the most used for voltage dip mitigation. But the use of SSC presents some problems.

If a fault occurs at downstream of the device, the fault current goes through the VSC, therefore the components must be designed properly considering these events. Another problem is due to the transformer saturation. When a voltage dip is detected, the SSC injects a voltage into the mains by applying a voltage on the secondary side of the injection transformer. The flux in the injection transformer is constituted by an AC term that varies with the grid frequency and a DC term that depends on the angle of the grid voltage at the beginning of the dip. If the initial phase of the injected voltage is equal to  $\pi/2 + n\pi$ , with n any integer, the transformer flux can reach up to twice the steady-state value. Therefore, if the transformer is not properly designed, saturation can occur and the magnetizing current can become very large. As a result, the VSC can be damaged due to overcurrent. To avoid saturation under all conditions, the transformer has to be sized to handle two times the normal steady-state flux requirement at maximum RMS injection voltage without saturating [16]. Another problem is that if during the dip a feeder, where there is the sensitive load, is open by the protection, SSC can't work not supplying the sensitive load.

The E-STATCOM does not have all these problems. It is mainly used as a active filter, but if the cost of the power electronic components will became smaller than today and if the power required by the E-STATCOM will be easily available, this system can replace the SSC for voltage dip mitigation.

In the next chapter, the E-STATCOM, and especially its control system, will be described in detail.

## Chapter 4

# Control System for Shunt-Connected VSC

#### 4.1 Introduction

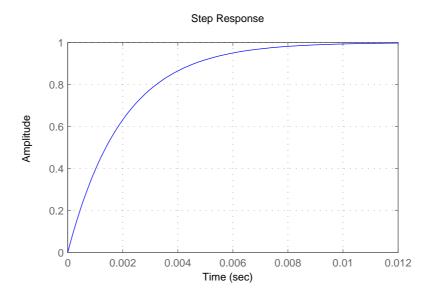

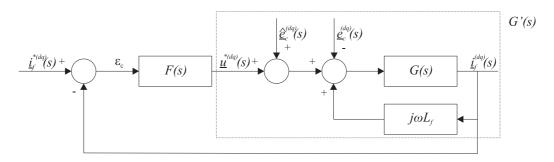

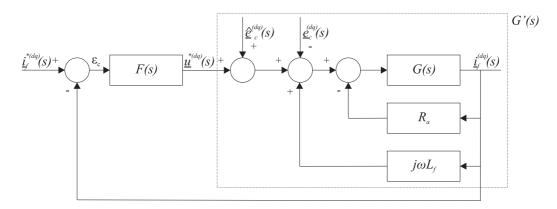

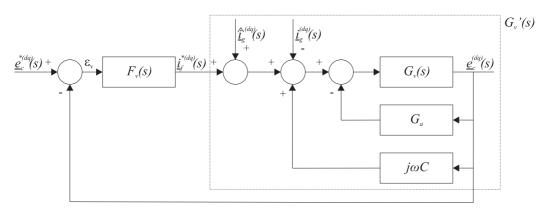

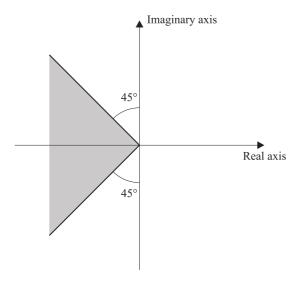

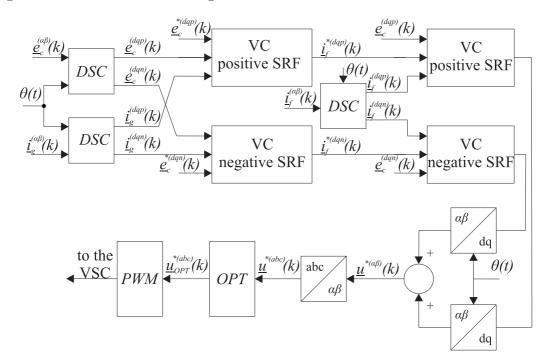

In the previous chapter, different voltage dip mitigation methods have been described. In this chapter a specific on about the control system for Shunt-Connected VSC for voltage dips mitigation will be carried out. The control system consists of two controllers: a vector current-controller and a vector voltage-controller. These controllers will be connected in cascaded under the assumption that the inner loop (vector current controller) is much faster than the outer loop (vector voltage controller). Stability analysis considering the impact of the controller bandwidths and the impact of the model parameters will be carried out.

Improvements of the standard control system in order to control positive and negative sequence independently will be presented by a dual vector current- and voltage-controller.

## 4.2 Description of electrical system

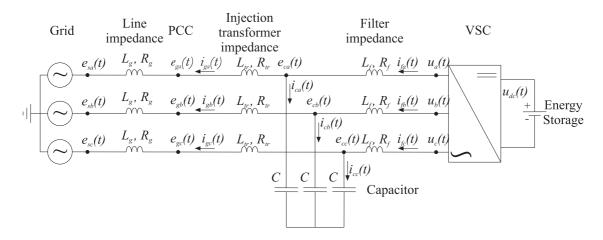

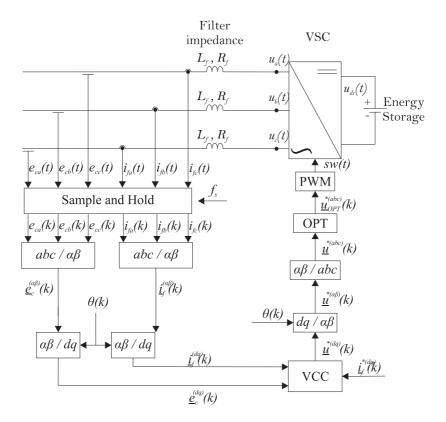

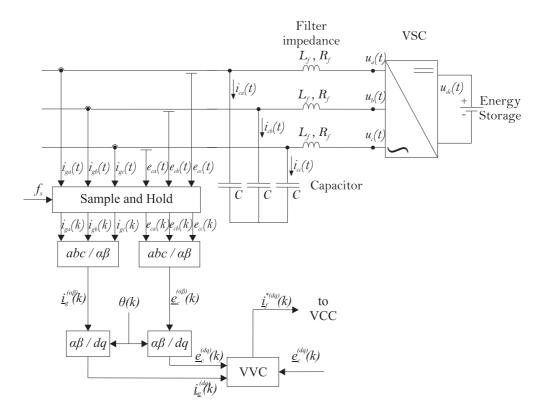

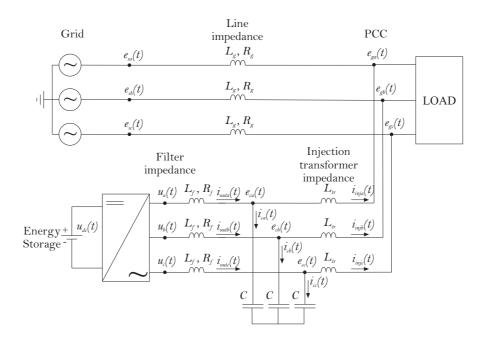

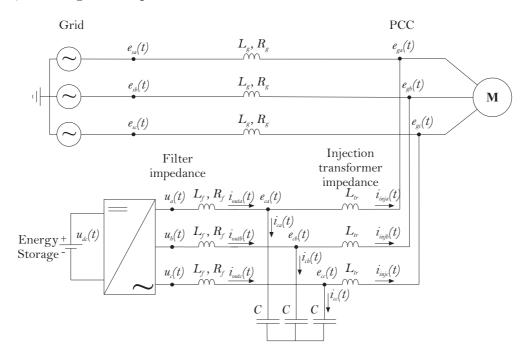

To derive the control system, it is necessary to describe how the shunt-connected VSC acts to mitigate voltage dips. The electrical system is shown in Figure 4.1. The grid voltages are denoted by  $e_{sa}(t)$ ,  $e_{sb}(t)$  and  $e_{sc}(t)$ . The line impedance is modelled as a resistance  $R_g$  and inductance  $L_g$ . The voltages at the point of common coupling (PCC) are denoted by  $e_{ga}(t)$ ,  $e_{gb}(t)$  and  $e_{gc}(t)$ . The injection transformer impedance has a resistance  $R_{tr}$  and inductance  $L_{tr}$ . The inductance and resistance of the AC-filter reactor are denoted by  $R_f$  and  $L_f$  respectively. A capacitor C is added in between the filter reactor at the VSC output and the transformer, with the twofold purpose of making the voltage at the PCC more stable and filtering the harmonic voltage components in the VSC output voltage.

Figure 4.1: Main electrical circuit of Shunt-connected VSC.

As a result, the filter inductor, the capacitor and the transformer inductor make an LCL-filter. The control objective is to maintain the voltage at the PCC constant. By observing the electrical scheme, if the transformer impedance is neglectable, it is possible to reach this purpose by maintaining the voltage across the capacitor constant.

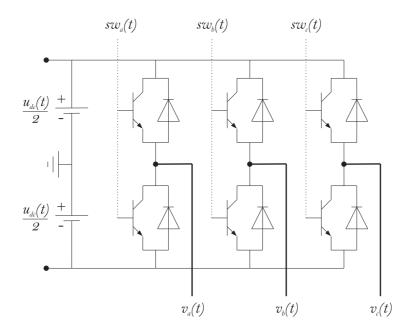

Figure 4.2 shows a three-phase VSC. The valves in the phase-legs of the VSC (usually insulated gate bipolar transistors, IGBTs) are controlled by the switching signals  $sw_a(t)$ ,  $sw_b(t)$  and  $sw_c(t)$ . The DC-link voltage is denoted by  $u_{dc}(t)$ . The switching signal can be equal to  $\pm 1$ . When  $sw_a(t)$  is equal to 1, the upper valve in the phase a is turned on while the lower valve in the same leg is off. Therefore, the potential  $v_a(t)$  is equal to half of the DC-link voltage  $(u_{dc}(t)/2)$ . Vice versa, when the switching signal is equal to -1, the upper valve is off and the lower one is on and, thus,  $v_a(t)$  is equal to  $-u_{dc}(t)/2$ .

Figure 4.2: Three-phase Voltage Source Converter (VSC).

It is possible to describe the three-phase system of the inverter output voltage as an equivalent two-phase system, with two perpendicular axes, denoted as  $\alpha$  and  $\beta$ . It is convenient to consider these axes as the real and imaginary axes in a complex plane. With the complex two-phase representation, the three-phase/two-phase transformation is given by

$$\underline{v}^{(\alpha\beta)}(t) = v_{\alpha} + \jmath v_{\beta} = K\left(v_a + v_b e^{\jmath \frac{2\pi}{3}} + v_c e^{\jmath \frac{4\pi}{3}}\right) \tag{4.1}$$

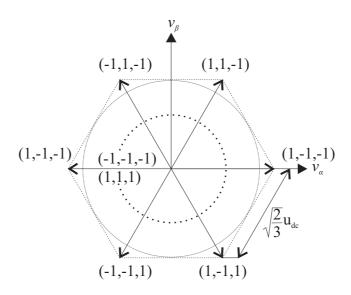

where K is a scaling constant. The complex quantity  $\underline{v}^{(\alpha\beta)}(t)$  is called space vector. The scaling constant K can be chosen arbitrarily. Depending on the application, one choice can be more convenient than another. There are three standard selections (Appendix A); in this work K is equal to  $\sqrt{3/2}$  (power-invariant transformation). The three switching signals  $sw_a$ ,  $sw_b$  and  $sw_c$  can be combined in eight ways. The resulting voltage vectors for these combinations draw a hexagon in  $\alpha\beta$  plane. Figure 4.3 shows the eight realizable voltage vectors and their switching combinations for the two level VSC. As an example, a vector  $\underline{v}(sw_a, sw_b, sw_c)$  with switching states  $sw_a = 1$ ,  $sw_b = -1$  and  $sw_c = 1$  is represented as (1,-1,1). Due to the selected parameter K, the maximum modulus of the voltage vector is

$$\underline{v}(t) = \sqrt{\frac{2}{3}} \cdot u_{dc} \tag{4.2}$$

which is attained for all switching states except (1,1,1) and (-1,-1,-1), which both yield to the zero vector. The maximum sinusoidal output voltage of the VSC corresponds to the maximum circle inside the hexagon. The radius of the circle is the maximum line-to-line voltage

$$|\underline{v}_{max}| = |\underline{v}| \cos\left(\frac{\pi}{6}\right) = \sqrt{\frac{2}{3}} \frac{\sqrt{3}}{2} \cdot u_{dc} = \frac{u_{dc}}{\sqrt{2}} \approx 0.707 u_{dc} \tag{4.3}$$

To obtain the switching signals for the VSC, Pulse Width Modulation technique (PWM) has been adopted. The maximum output voltage amplitude from the VSC when using sinusoidal PWM is given by [17]

$$\underline{v}(t) = \sqrt{\frac{2}{3}} \cdot \frac{u_{dc}}{2} \approx 0.61 u_{dc} \tag{4.4}$$

shown in Figure 4.3 with the dot circle.

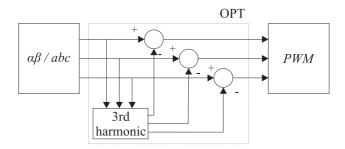

Therefore, by using PWM the VSC it is not utilized to its maximum. It is possible to use several methods for increasing the maximum output voltage with the same DC-Link. As an example, waveforms of zero-sequence can be added to the sinusoidal reference voltage to the PWM. One common choice is to add a 3rd harmonic of 25% the amplitude of the fundamental frequency component to all reference signals [18].

Figure 4.3: Space-vector diagram.

The following figure shows the method used to increase the maximum output voltage.

Figure 4.4: Block diagram for increasing the maximum output voltage.

The 3rd harmonic is calculated

$$H_3 = \frac{\max(u_a^*, u_b^*, u_c^*) + \min(u_a^*, u_b^*, u_c^*)}{2}$$

(4.5)

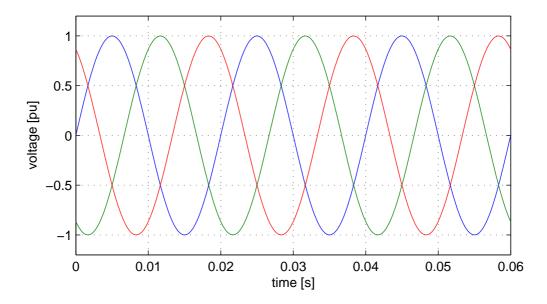

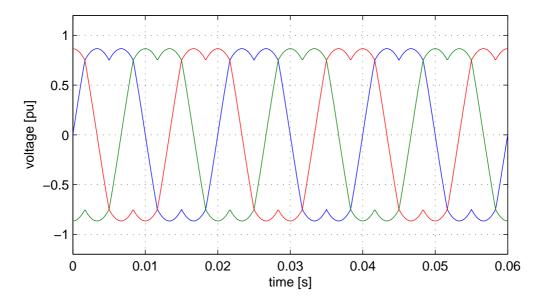

If the same deviation  $H_3$  is subtracted from all reference signals (Figure 4.5), a zero-sequence component is added. The resulting three-phase voltages are depicted in Figure 4.6. It is possible to observe that the maximum output voltage increases by 15.5% without increasing the DC-link. The principle drawback of this method is that a 3rd harmonic is injected into the grid. This is avoided by not connecting the AC side of the VSC to ground.

Figure 4.5: Three-phase voltage system without 3rd harmonic injection.

Figure 4.6: Three-phase voltage system with 3rd harmonic injection.

## 4.3 Control System

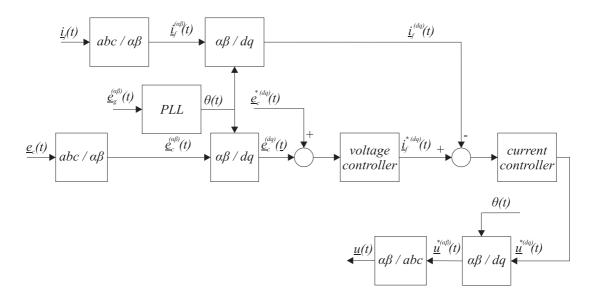

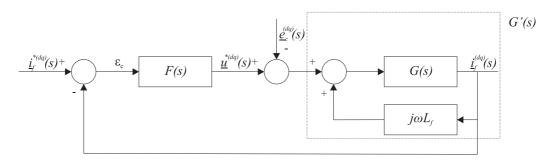

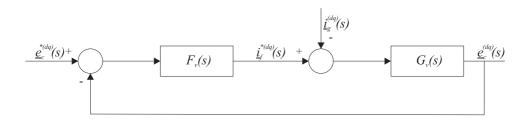

As mentioned earlier in this chapter, the control system consists of two controllers: a vector current-controller and a vector voltage-controller. These controllers will be connected in cascaded under the assumption that the inner loop (vector current controller) is much faster then the outer loop (vector voltage controller). The vector voltage controller produces a reference signal proportional to the output VSC current in order to maintain the voltage above the capacitor constant to the desired value, while the vector current controller produces a reference signal proportional to the VSC output voltage in order to track the reference VSC output current. Figure 4.7 shows the block diagram of the implemented control system.

Figure 4.7: Block diagram of the implemented control system.

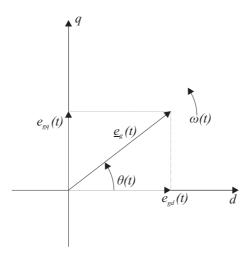

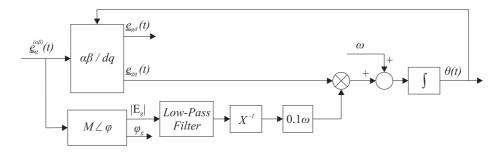

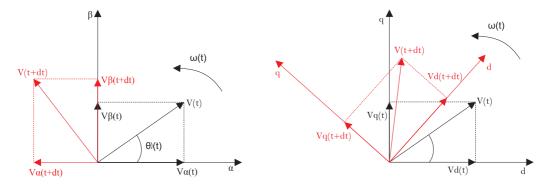

The control system will be derived in the synchronous coordinate, applying the equations in Appendix A. In this way a three-phase system can be expressed by a two-phase system whose components will appear as DC quantities, in steady-state. As seen in Appendix A in order to obtain the dq- coordinates, voltages and currents will be transformed to fixed coordinate  $\alpha\beta$  and then to synchronous coordinate dq-. To calculate the dq- coordinates it is necessary calculate the transformation angle  $\theta(t)$  (Figure 4.8) that will be calculate with a Phase-Looked Loop (PLL).

Figure 4.8: Vector  $\underline{e}_q(t)$  in dq – coordinates.

The dq transformation is not only useful for analysis, but also for implementation of control algorithms, since it is easier to design controllers for DC quantities instead of AC quantities.

One of the most important advantages in using DC quantities is for correct operations of PI controller. The transfer function of a the PI controller is given by

$$G(s) = k_p + \frac{k_i}{s} \tag{4.6}$$

where  $k_p$  is the proportional gain and  $k_i$  is the integral gain.

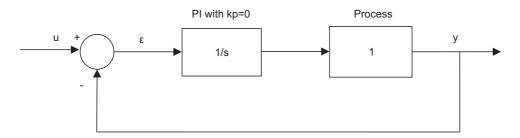

The proportional gain acts like a simple amplitude gain and it works properly at any frequency. The integral gain works properly only with DC quantities. To have an idea of the integral response, we can consider the block diagram shown in Figure 4.9. The error  $\varepsilon$  is given by

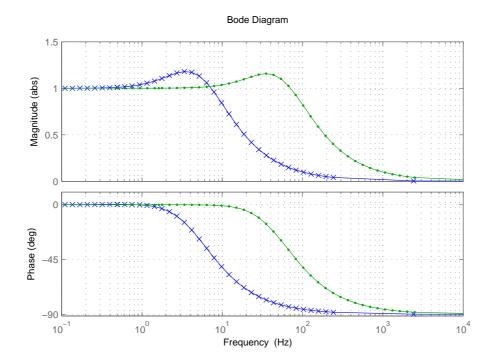

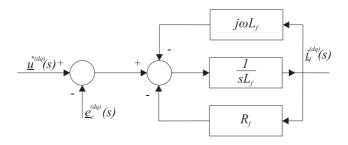

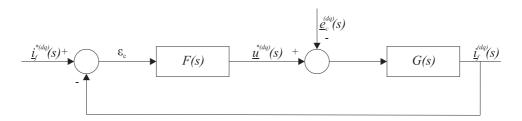

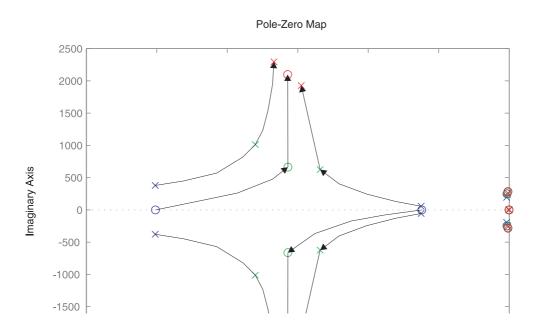

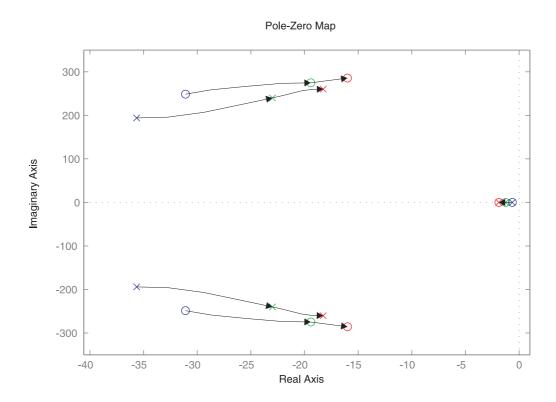

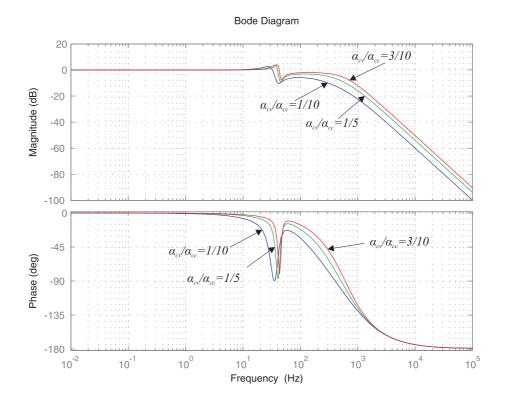

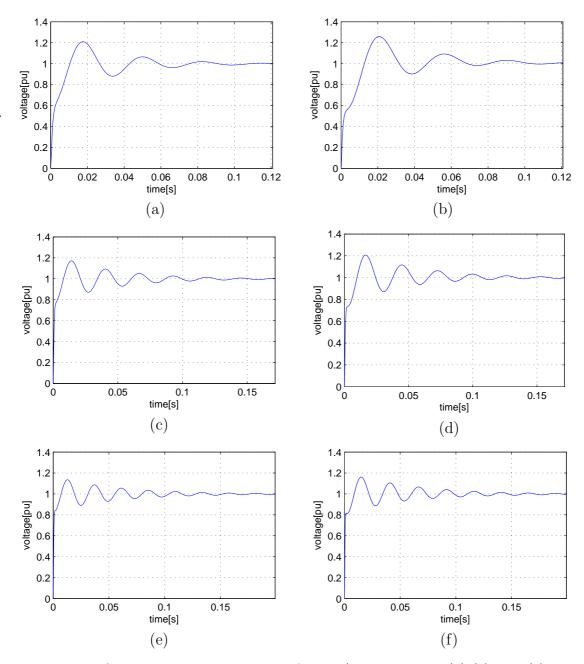

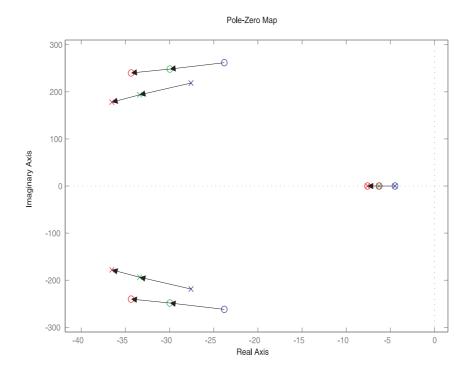

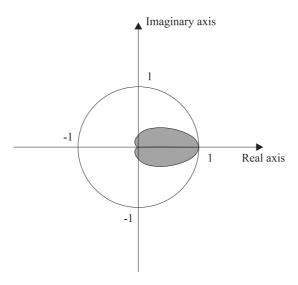

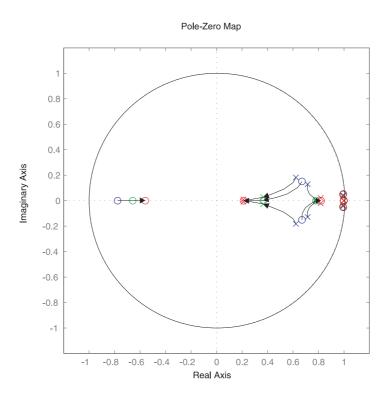

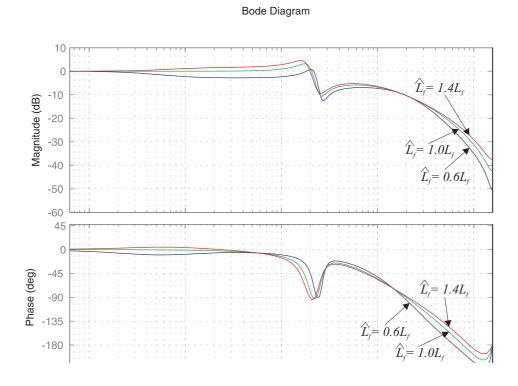

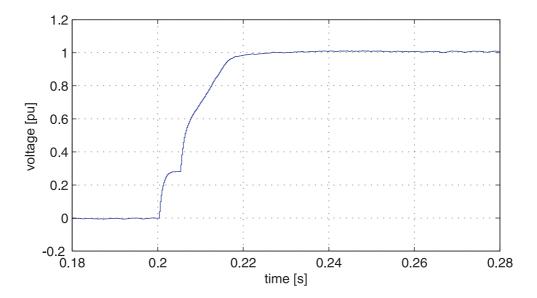

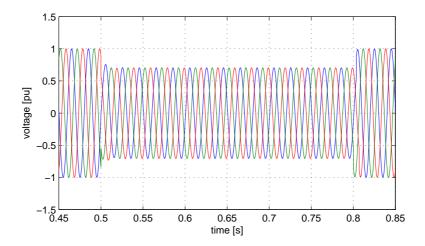

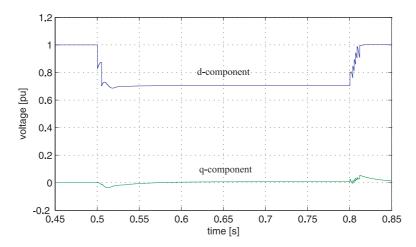

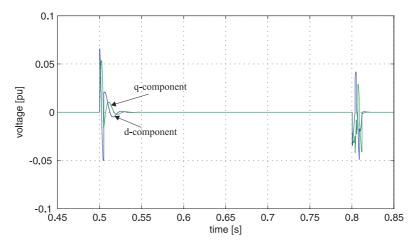

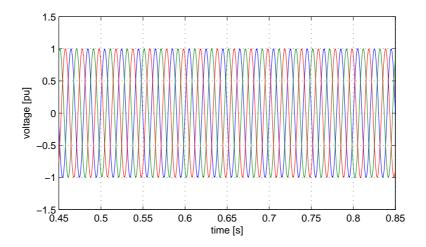

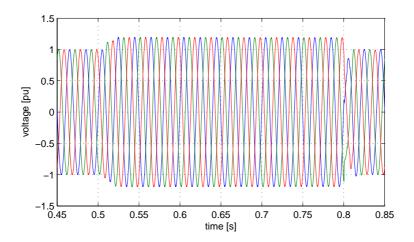

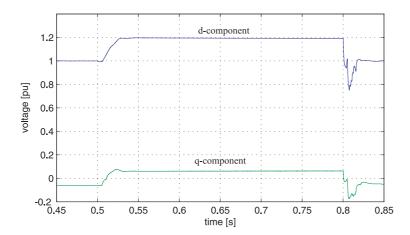

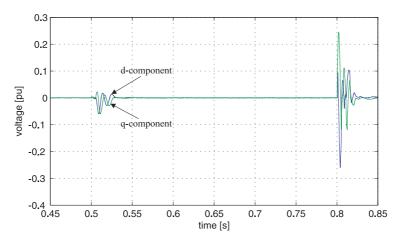

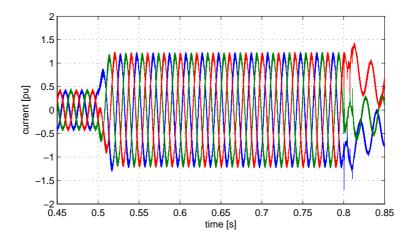

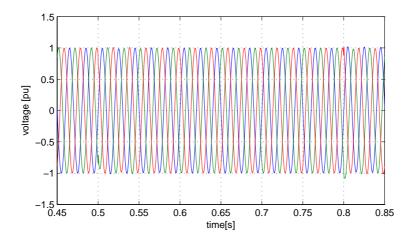

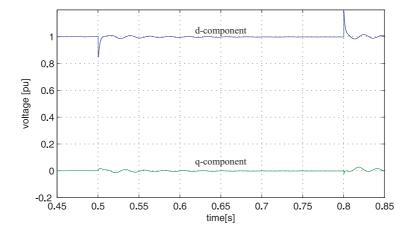

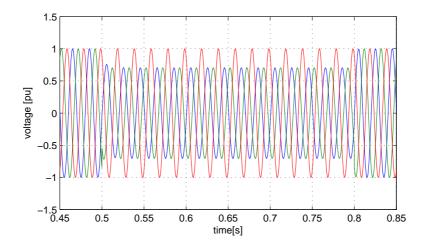

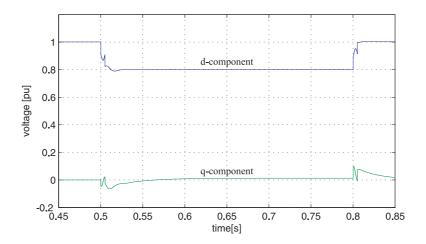

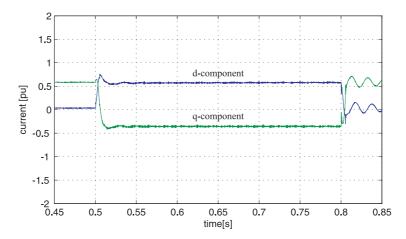

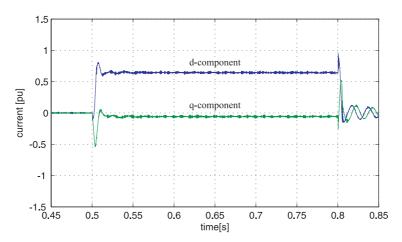

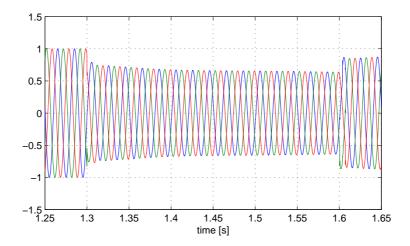

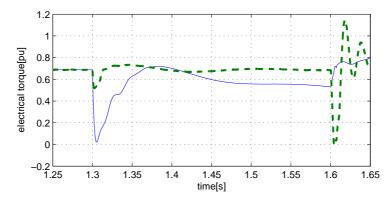

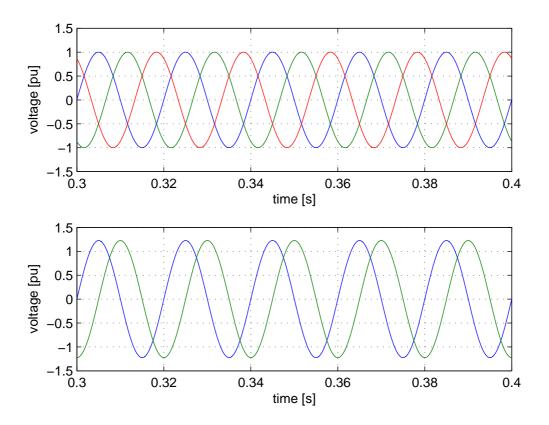

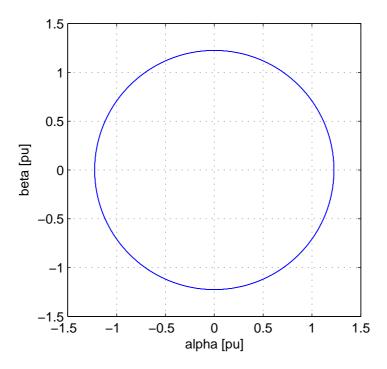

$$\varepsilon = u - \varepsilon(\frac{1}{s}) \Rightarrow u = \varepsilon \left(1 + \frac{1}{s}\right) = \varepsilon \left(\frac{s+1}{s}\right)$$