# **Chapter 1**

# Introduction

### 1.1 Quantum electrical circuit

Superconducting electrical circuits are known as quantum electrical circuit and used for quantum information processing. They behave quantum mechanically since all Cooper pairs in a superconducting circuit condense into a single quantum state, furthermore no dissipation [1] [14]. In a normal electrical circuit there are no Cooper pairs. Large number of unpaired electrons has different microscopic degrees of freedom which leads to dissipation and decoherence by interacting with the environment. On the other hand, in a superconducting electrical circuit there is only single degree of freedom which ensures better quantum coherence. Using Josephson junctions in superconducting circuits, quantum two level systems can be used as qubits to perform quantum computation.

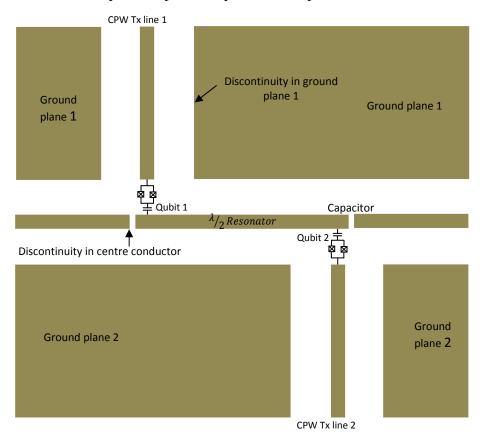

Fig.1.1: Schematic of two qubit quantum electrical circuit with discontinuities in the centre conductor making  $up \ a \lambda/2$  resonator, and several disconnected ground planes.

#### 1.1.1 Integration of quantum electrical circuit

For future quantum information processing specially for fabricating of a multi qubit quantum processor it is required to integrate quantum electrical circuit with other superconducting microwave passive circuit elements. In order to perform read out of multi qubit quantum processor a multiple number of resonators, for controlling the qubits, a large number of transmission lines are also required. As superconducting quantum electrical circuit are fabricated based on CPW technology, integration of all these circuit elements require lots of bending and discontinuities of the centre conductors and the corresponding ground planes.

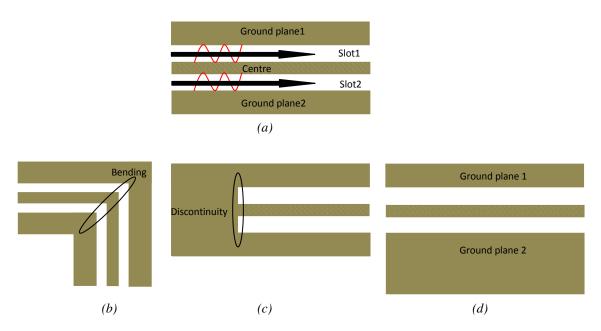

*Fig.1.2: CPW with (a) symmetrical structure (b) 90° bending (c) discontinuity (CPW short) and (d) asymmetry of the finite ground plane.*

A schematic of two qubit quantum electrical circuit is shown in Fig.1.1 where there are four discontinuities in ground plane and two discontinuities in centre conductor. If the circuit consist of more than two qubits then number of bending and discontinuities increases proportionally.

### **1.2** Parasitic modes in quantum electrical circuits

A CPW is a coupled slotline having two slots (slot1 and slot2 in Fig.1.2 (a)) coupled by the centre conductor.

If the wavelength  $(\lambda_s)$  of the signal current is larger compare to the slot length, parasitic modes could be excited at the broken ground planes. In Fig.1.1, signal current propagates from the left side of the Ground plane 1 cannot find a conductive path to reach the right side of the Ground plane 1 having a broken ground there. Hence, signal current bounces from the discontinuity and can't find a return path to circulate [15] [16]. This interrupted current generates parasitic modes at the discontinuity. In addition, the gap between the broken ground planes makes it a slotline mode waveguide. Thus, signal mode converts into a slotline mode and could be coupled with the desired CPW mode.

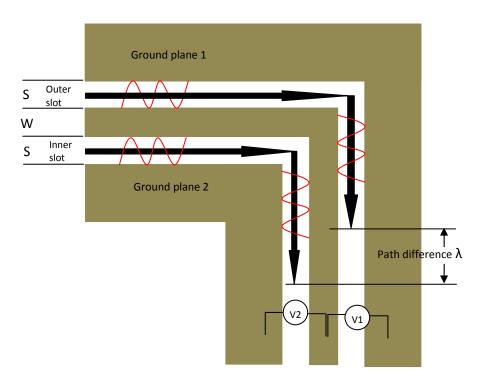

If the wavelength of the signal current  $(\lambda_s)$  is smaller than the slot length, parasitic modes might also be excited. As long as there is no bending or discontinuity, the structure is symmetric and the electric field waves travel with the same propagation speed through slot1 and slot2 maintaining 0° phase difference. If there is any bending, for example 90° CPW bending (see Fig.1.2 (b)), the symmetry of the structure is broken and the field waves encounter phase difference travelling longer distance through outer slot compare to inner slot (see Fig.1.3). As a result, after passing the bending, there is a net path difference of the two electric field waves between the inner and the outer slot [2]. This net path difference creates a phase difference which generates two different potentials  $v_1$  and  $v_2$  between the centre conductor and the two locally isolated ground planes. Hence, a net potential difference  $(v_1 - v_2)$  is developed between two ground planes. This unequal ground potential excites parasitic modes which could be coupled with the desired CPW mode propagating throughout the circuit.

Fig.1.3: Path difference of electric field wave (red) between inner and outer slot after bending.

Beside this, if there is asymmetry in the finite ground plane co-planar waveguide structure (see Fig.1.2 (d)) then CPW like mode (c-mode) and slotline-like mode (pi-mode) are excited [3] which can also be coupled with the CPW mode.

#### 1.2.1 Suppressing parasitic modes in quantum circuits using air-bridge

The easiest way to suppress higher order parasitic modes in superconducting co-planar waveguide is by using air-bridges [4] [5]. Air-bridge equalizes the potential of the two isolated ground planes, thus preventing excitations of modes at the discontinuity of the ground plane.

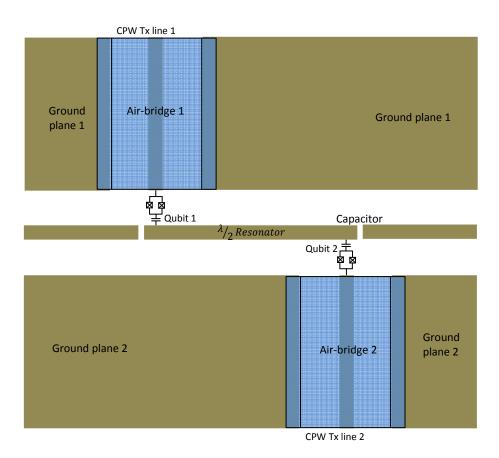

An air-bridge that crosses over the centre conductor adds a shunt capacitance to the transmission line. This shunt capacitance causes an undesired reflection from the point where it is connected. If the height of the air-bridge is chosen in such a way that the value of the shunt capacitance becomes very small, then the reflection becomes negligible. For a two qubit quantum electrical circuit such as the one in Fig.1.1, it is possible to equalize the ground potentials using air-bridges (see Fig.1.4). Thus prevents excitation of ground plane modes since it allows the current to flow uninterrupted through the ground planes. Air-bridge1 equalizes potential between left and right part of the ground plane 1, air-bridge 2 equalizes left and right part of the ground plane 2.

Fig.1.4: Schematic of two qubit quantum electrical circuit with long and high air-bridges.

The height of these two air-bridges must be chosen in such a way so that signal transmission through transmission line 1 and transmission line 2 remains unaffected.

# Chapter 2

## Goal and scope of the project

The goal of this project has been to design, fabricate and test superconducting air-bridges for quantum electrical circuits. Superconducting co-planar waveguides are used in quantum electrical circuit for qubit design due to a number of advantages. The most prominent reason is to be able to integrate qubits easily with CPW without making any via holes. Despite these advantages the most serious problem of using CPW is getting un-desired parasitic modes which are always present in complex microwave circuit even in superconducting state. Since a co-planar waveguide is two coupled slotlines, there always exist slotline modes with the coplanar mode [5]. As long as the circuit has no bending, discontinuity or asymmetry at the finite ground plane or structure, the slotline mode doesn't get excited. However, if there is any bending, discontinuity or asymmetry in the structure, the slotline modes are prone to get excited and couple with the CPW mode at the points of discontinuities [6]. In this case, electric field waves propagate through two slots experience path difference at the discontinuity or bending point which causes the phase difference and the electric fields between the two ground planes become unequal which creates finite potential difference between two isolated ground planes [2] [7]. Beside this, if a finite ground plane CPW with asymmetric structures is used, then CPW like mode (c mode) and slotline like mode (pi mode) is excited in addition to the CPW modes and slotline modes [3]. These undesired parasitic modes are very disturbing for quantum electrical circuits as well as qubits and causes problems during quantum measurement.

During practical circuit design it is difficult to keep two slot lengths exactly the same and to make the structure exactly symmetrical. Even for a single qubit circuit, the structure becomes complicated as there are several different components such as microwave resonators; feed lines for coupling to the qubit and controlling it. This makes the CPW structure consist of bendings and discontinuities. As a result, unwanted parasitic modes always exist in the qubit circuit which can easily interfere with the resonator frequencies. A qubit can be coupled with this unwanted resonance coming from the slot lines instead of the real resonance of the cavity, which creates problem of controlling and reading out the qubit properly. The problem is quite severe when more than one qubit are coupled with the resonator, since the number of bendings, discontinuities, and asymmetries of finite ground planes increase with the increasing number qubits in the circuit. If more than one resonator is used in the circuit then unwanted modes are extremely disturbing as it is hard to distinguish which frequency comes from the resonator or the slotline modes and tuning the qubits to the correct resonant frequency becomes guesswork. To get rid of the parasitic modes, wire bonding is often required to equalize ground potential and suppress the slotline modes. Since at high frequency, voltage and current waves vary spatially through co-planar waveguide structure, equalizing the ground potential using small bonding wire only neutralize the offset ground potential locally at this point. If unequal ground potentials come from bending and discontinuities of the co-planar waveguide then in order to equalize this it is required to put the air-bridge at the point of bending, discontinuity [13]. In this case one small air bridge close to every bending, discontinuity is required. On the other hand if there is asymmetry of the finite ground plane then unequal ground potential is continuous and remains throughout the structure [3]. In this case bonding wire is unable to equalize the ground potential distributed throughout the structure. In addition, if small air-bridges are used, then the slotline modes can reappear within couple of thousands micron of the air-bridge [3].

In order to solve the problem, small air-bridges must be connected with regular interval keeping small relative distance in between them or one large air-bridge can be placed throughout the whole finite ground plane. Small air-bridges placed with regular interval can produce standing wave modes between two air-bridges and signals propagate through it suffer repeated reflection and transmission at the place where those air-bridges are connected. In that case the transmission line would show poor performance with substantial signal loss. In case of using large air-bridges, the added shunt capacitance is so large that input reflection is large resulting in insertion loss. However, so far, at the cryogenic temperature the characteristics of aluminum air-bridges on CPW have not been reported anywhere. How aluminum air-bridges placed at regular interval can produce standing wave at cryogenic temperature and how insertion loss of large air-bridge can be changed with cryogenic temp are still to be investigated. Our goal has been to design large superconducting air-bridge with minimum insertion loss and use them in quantum circuits. Although bonding wire can equalize potential only at the place where it is connected but it has negligible insertion loss. On the other hand, long air-bridge can equalize the potential throughout the structure but it has large insertion loss  $(S_{21})$ . Hence, our goal was to increase the height of the air-bridge in such a way so that added shunt capacitance is very small and corresponding insertion loss is negligible in the superconducting state.

# **Chapter 3**

# **Theoretical background**

### 3.1 The coplanar waveguide transmission line

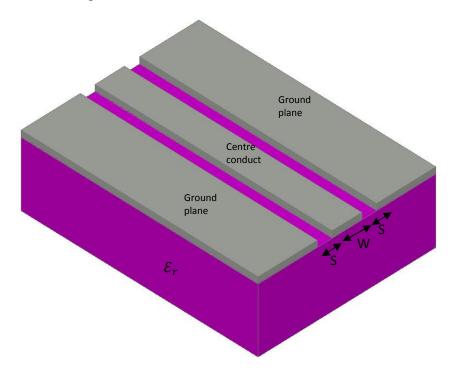

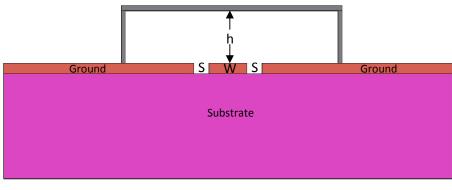

A Co-Planar Waveguide (CPW) is a thin film transmission line on low loss dielectric substrate. It consists of a center strip conductor and two ground plane conductors adjacent and parallel to it (see Fig.3.1).

*Fig.3.1:* A Coplanar waveguide (gray) on top of a substrate (pink). The centre conductor width is W and the gaps between the centre strip and the ground planes are S.

As shown in Fig.3.1, there is a gap (S) between the center strip and the ground planes. The characteristic impedance  $Z_o$  of CPW depends on relative dielectric constant ( $\mathcal{E}_r$ ) of the substrate and the ratio of center conductor width (W) to the gap width (S) i.e. W/S ratio. Using the zeroth-order quasi-static approximation characteristic impedance ( $Z_o$ ) and phase velocity ( $v_{ph}$ ) can be calculated [8] as

$$Z_{o} = \frac{1}{C_{cpw}v_{ph}}$$

(3.1)

$$v_{\rm ph} = \left(\frac{2}{\mathcal{E}_{\rm eff}+1}\right)^{1/2} c \tag{3.2}$$

Where,  $C_{cpw}$  is the capacitance per unit length of CPW which can be calculated by using conformal mapping technique,  $\mathcal{E}_{eff} = \frac{\mathcal{E}_r + 1}{2}$  is the effective dielectric constant of the substrate and c is the velocity of light in free space.

The propagation constant ( $\beta$ ) of the CPW transmission line is given by following expression

$$\beta = \frac{2\pi}{\lambda_{\rm s}} \sqrt{\mathcal{E}_{\rm eff}} \tag{3.3}$$

Where,  $\lambda_s$  is the wavelength of the signal.

The attenuation of the signal that propagates through the CPW depends on the attenuation due to dielectric losses ( $\alpha_d$ ) in the substrate and attenuation due to conductor losses ( $\alpha_c$ ) in the center conductor and ground planes. Hence the total attenuation is the sum of these two attenuations;  $\alpha = \alpha_{d+}\alpha_c$ .

#### 3.1.1 Superconducting coplanar waveguide

In a superconducting co-planar waveguide there is no loss for dc current but there is some conductor loss for RF frequencies. The attenuation constant is very small compared to the same normal metal CPW with the same geometry and characteristic impedance. Superconducting co-planar waveguides are used as quantum electrical circuits, especially for making high quality factor superconducting resonators.

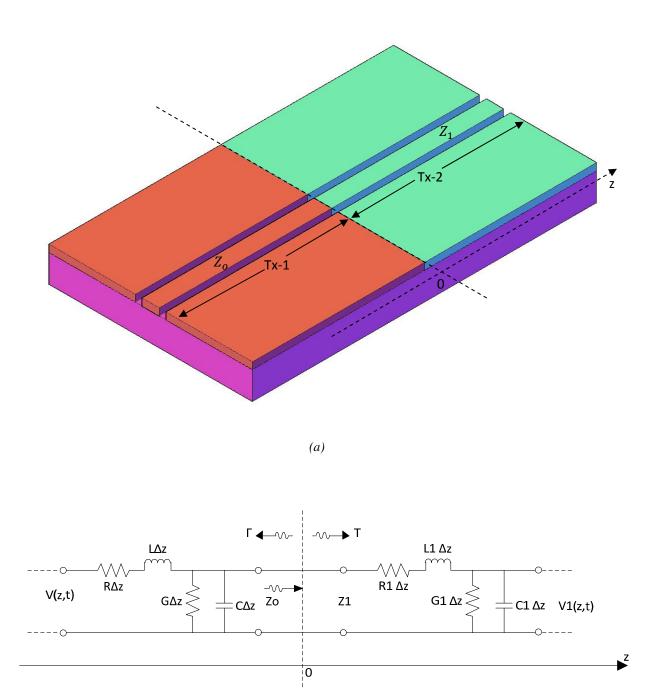

#### 3.1.2 Transmission and reflection coefficient of a CPW transmission line

If a CPW transmission line Tx-1(orange) having characteristic impedance  $Z_o$  is terminated with another CPW transmission line, Tx-2 with characteristic impedance  $Z_1$  then TX-2 acts as a load for Tx-1 (see Fig.3.2 (a)). Some portion of the incident signal power coming from transmission line, Tx-1 will be reflected from the interface and some will be transmitted to transmission line, Tx-2. The equivalent circuit of this CPW can be represented by distributed circuit elements (see Fig.3.2 (b)). The reflection co-efficient ( $\mathbb{Z}$ ) and the transmission coefficient (T) of this CPW for having mismatch of the characteristic impedance are defined by equation 3.4-a, 3.4-b.

Reflection co-efficient,

$$\Gamma = \frac{Z_1 - Z_0}{Z_1 + Z_0} \tag{3.4-a}$$

Transmission co-efficient,

$$\mathsf{T} = 1 - \Gamma \tag{3.4-b}$$

If the two characteristic impedances are the same  $(Z_1 = Z_o)$ , then the equivalent circuit elements, resistance R1=R, inductance L1=L, capacitance C1=C, conductance G1=G must be

same and there is no impedance mismatch at the interface. As a result, the reflection coefficient would be zero and the transmission coefficient would be 1. All the signal power coming from Tx-1 would be absorbed in Tx-2. This is called perfect matching of the load.

(b)

Figure.3.2: A CPW transmission line (a), and its equivalent circuit, where R=series resistance per unit length in  $\Omega/m$ , L=series inductance per unit length in H/m, G=shunt conductance per unit length in S/m, C=shunt capacitance per unit length in F/m (b).

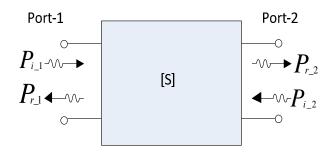

#### 3.1.3 Scattering parameters

Figure 3.3: A two port network having signal power incident and reflected from port-1 and port-2.

From the measurement point of view one usually use the scattering parameters to describe the reflection and transmission coefficients. For a two port network of Fig.3.3 the incident power wave at port-1 is  $P_{i_{1}}$  and reflected power wave from port-1 is  $P_{r_{1}}$ , if the incident power wave at port-2 is  $P_{i_{2}}$  and reflected power wave from port-2 is  $P_{r_{2}}$  then scattering parameter can be defined as

$$S_{11=\frac{P_{r_{-1}}}{P_{i_{-1}}}=\frac{Reflected power wave at port-1}{Incident power wave at port-1}|_{P_{i_{-2}}=0}}$$

$$S_{21=\frac{P_{r_{-2}}}{P_{i_{-1}}}=\frac{Transmitted power wave at port-2}{Incident power wave at port-1}|_{P_{i_{-2}}=0}}$$

The reflection ( $\Gamma$ ) and transmission coefficient (T) are equivalent to  $S_{11}$  and  $S_{21}$  respectively.

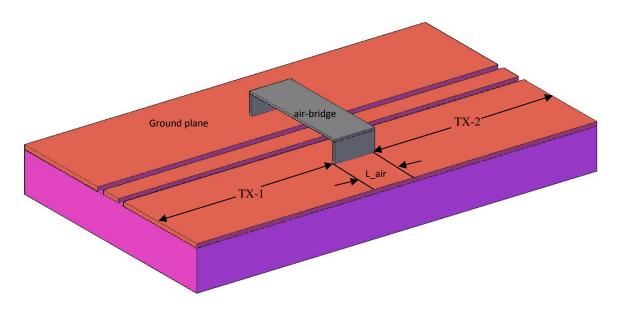

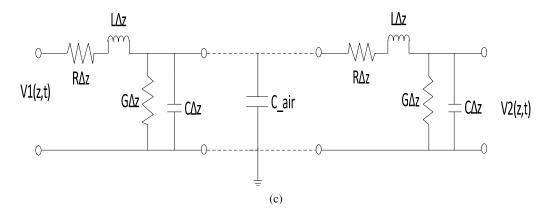

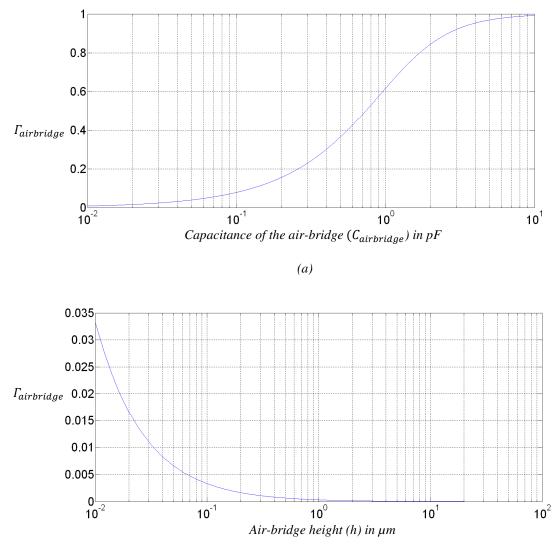

### **3.2** Reflection coefficient of a CPW transmission line including an airbridge

If an air-bridge is connected with a CPW (as in Fig.3.4 (a)), then it can be modeled using a lumped element shunt capacitance (see Fig.3.4(c)). Though Tx-1 and Tx-2 are perfectly matched, the characteristic impedance of Tx-2 seen by Tx-1 would be different having the additional shunt capacitance in parallel.

If the added shunt capacitance of the air-bridge is  $C_{airbridge}$  then new characteristic impedance can be written using equation (3.1) as

$$Z_{1\_airbridge} = \frac{1}{(C_{cpw} + C_{airbridge})v_{ph}}$$

(3.5)

If the reflection co-efficient of the CPW transmission line at the interface where the airbridge is connected is  $\Gamma_{airbridge}$  then using equation (3.4-a) we can write the reflection for the air-bridge as

$$\Gamma_{airbridge} = \frac{Z_{1\_airbridge} - Z_0}{Z_{1\_airbridge} + Z_0}$$

(3.6)

$$\Rightarrow \Gamma_{airbridge} = -\frac{1}{1+2\frac{C_{cpw}}{C_{airbridge}}}$$

(3.7)

Equation (3.6) can be written in terms of  $C_{cpw}$  and  $C_{airbridge}$  in equation (3.7) using equation (3.1), (3.5). Minus sign in equation (3.7) indicates reflected voltage returns with inverted

(*a*)

*Fig.3.4: (a)* A CPW line with air-bridge; (b) CPW with air-bridge (Cross-sectional view). (c) Equivalent circuit of CPW transmission line including air-bridge.

amplitude. The value of added shunt capacitance ( $C_{airbridge}$ ) can be estimated using parallel plate capacitor equation (3.8).

$$C_{airbridge} = \frac{\varepsilon_o \varepsilon_{eff} A}{h}$$

(3.8)

Where h is the height of the air-bridge and A is the cross-sectional area of the air-bridge,  $A=L\times W$ , L=Length of the air-bridge, W=Width of the air-bridge.

For an air-bridge with L=500 $\mu$ m, W=60 $\mu$ m, h=10 $\mu$ m the estimated capacitance would be 26fF, where permittivity in free space,  $\mathcal{E}_o = 8.854 \times 10^{-12}$  F/m and effective dielectric constant for air,  $\mathcal{E}_{eff} = 1$ .

$$\Gamma_{airbridge} = -\frac{1}{1+2 \frac{C_{cpw} h}{\varepsilon_0 \varepsilon_r \cdot A}}$$

(3.9)

Putting the value of  $C_{airbridge}$  from equation (3.8) in equation (3.7), we can rewrite the reflection coefficient ( $\Gamma_{airbridge}$ ) in terms of air-bridge height, h and cross-sectional area, A, in equation (3.9). If the height of the air-bridge is small enough compare to its length (or width) then added shunt capacitance would be very large in equation (3.8) and corresponding reflection co-efficient ( $\Gamma_{airbridge}$ ) would be very high according to equation (3.9). On the other hand, if the height of the air-bridge is larger compare to its cross-sectional area then reflection coefficient  $\Gamma_{airbridge}$  would be very small. From equation (3.9) we can see by choosing the height of the air-bridge very large compare to its length we can get almost no reflection from the interface where air-bridge is connected. This will be verified by simulation later in Chapter 4.

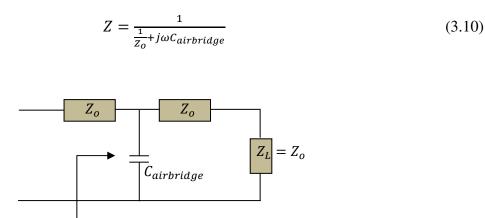

In order to estimate the reflection coming from the air-bridge ( $\Gamma_{airbridge}$ ), we can assume CPW as a lossless transmission line with characteristic impedance,  $Z_o = \frac{L}{c}$ . The impedance of the air-bridge with the rest of the transmission line [see Fig.3.5] can be written in equation (3.10).

Fig.3.5: Impedance of the air-bridge connected in parallel with a lossless transmission line.

(b)

Fig.3.6: Reflection coefficient of the air-bridge ( $\Gamma_{airbridge}$ ) connected in parallel with a lossless transmission line Vs (a) capacitance of the air-bridge ( $C_{airbridge}$ ), (b) height of the air-bridge (h).

Using equation (3.10) and (3.4-a), reflection coefficient for the air-bridge can be written as

$$\Gamma_{airbridge} = -\frac{1}{1 + \frac{2}{j\omega C_{airbridge} Z_0}}$$

(3.11)

Where  $\omega$ =angular frequency of the signal.

$$\omega = 2\pi f \tag{3.12}$$

Putting the value of  $C_{airbridge}$  in equation (3.11) from equation (3.8) we can rewrite equation (3.11) in terms of air-bridge height (h) and cross-sectional area, A, equation(3.13).

$$\Gamma_{airbridge} = -\frac{1}{1 + \frac{2}{j\omega \mathcal{E}_0 \mathcal{E}_{eff} Z_0}(\frac{h}{A})}$$

(3.13)

Assuming  $Z_o = 50\Omega$  and f=5 GHz we get reflection coefficient ( $\Gamma_{airbridge}$ ) with respect to air-bridge capacitance ( $C_{airbridge}$ ) and air-bridge height (see Fig.3.6). From Fig.3.6 (a) we can see if the value of the capacitance is increased reflection will also increase and reflection is decreased with the increasing height of the air-bridge (see Fig.3.6 (b)).

# **Chapter 4**

# Design and simulation of air-bridge

## 4.1 AXIEM 3D electromagnetic simulator

It is important to simulate the CPW with air-bridges prior to fabrication in the process lab, to get an overview of what the height of the air-bridge should be to get minimum reflection from the transmission line. In order to simulate the real structure, which was designed using AutoCAD (see Fig.4.1) and fabricated in the process lab, we used AXIEM 3D Electro Magnetic (EM) simulator, a built in 3D EM solver of the AWR design environment. AXIEM uses Method-Of-Moments (MOM) technique to simulate any multi-layered dielectric structure with thick metal. Its unique hybrid meshing technique divides the EM structure into a large number of triangular and rectangular elements and optimizes the meshing to maximize accuracy with minimum number of unknowns. Hence, it can solve any complicated multilayered dielectric structure with minimum simulation time and good accuracy.

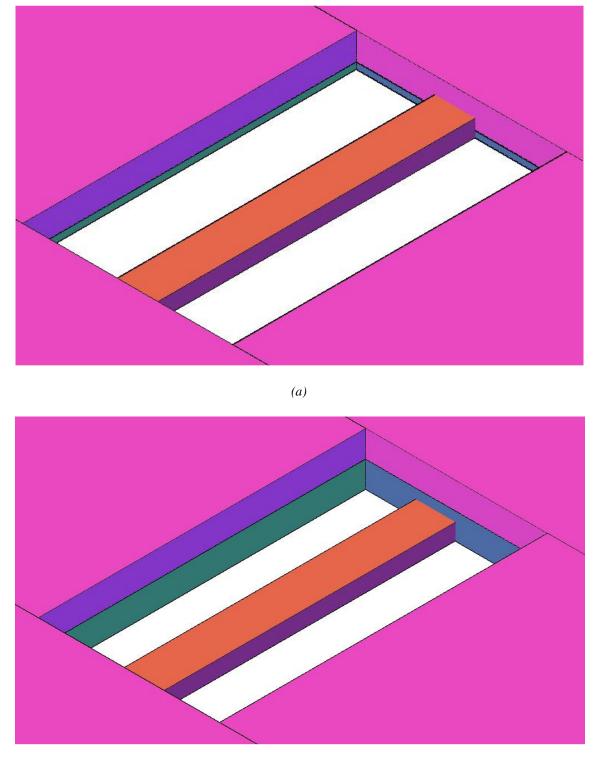

### 4.2 Modeling the air-bridge using AXIEM

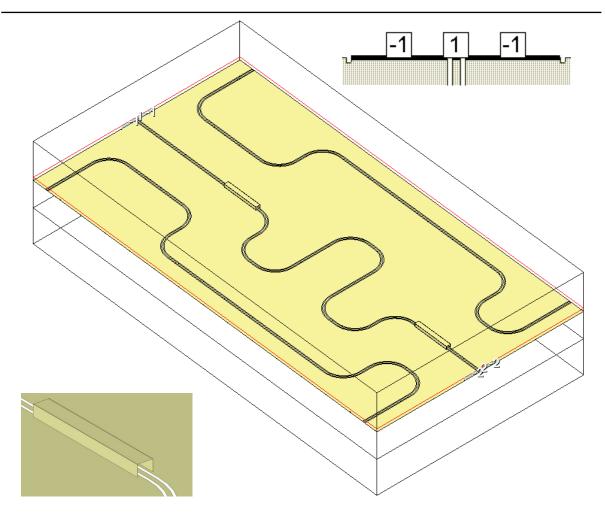

In order to model the device for simulation using AXIEM (see Fig.4.2 (a-c)) we choose 380 µm thick Si wafer with relative dielectric constant 11.9 and loss tangent 0.001. On top of the Si we placed a 400*nm* thick aluminum CPW with very high conductivity ( $3.53 \times 10^{15}$  S/m) for creating a superconducting like CPW structure with almost no attenuation. To represent the height for the air-bridge we choose an 8.5µm thick dielectric layer of air. The thickness of the air-bridge as well as the sidewalls of the air-bridge is chosen as 2µm thick aluminum. There are two dielectric layers of air, each 2mm high for creating the space of top and bottom metallic covers of sample holder. The boundary of top and bottom layer was chosen as perfect conductor for representing the metallic cover of the sample holder. For perfect modeling of the CPW we used differential MW port -1, 1 and -2, 2 (see Fig.4.3). Port -1 and -1 on both sides of port 1 are connected together acting as a ground reference for port 1. Similarly port -2 and -2 on both sides of the port 2 are connected together acting as a ground reference for port 2. The meandering of the AutoCAD structures (see Fig.4.1) is captured in AXIEM which ensures a real structure simulation. The 3D simulating structure is shown in Fig.4.3. There are two air-bridges placed in each transmission line in order to see the effect of standing wave modes between these air-bridges. The relative distance between the two airbridges is chosen to be 5mm which can be approximated as a  $\lambda/2$  resonator with first fundamental mode roughly at 11 GHz using equation (4.1).

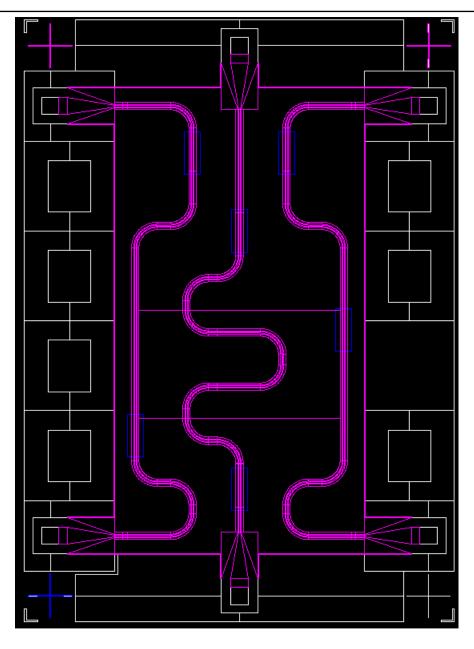

Fig.4.1: Mask design using AutoCAD for CPW with air-bridges. There are three CPW (pink) each having two 500µm long air-bridges (blue) placed a relative distance in between them 3.2mm (left one), 5mm(middle one), 2mm(right one). The mask for gold contact pad (white one).

$$f = \frac{c}{2L\sqrt{\varepsilon}_{eff}} \tag{4.1}$$

Where speed of light,  $c = 3 \times 10^8$  m/s; L= 5mm, is the distance between the two air-bridges and  $\mathcal{E}_{eff}$  is the effective dielectric constant which can be written  $\mathcal{E}_{eff} = \frac{\mathcal{E}_{air} + \mathcal{E}_{si}}{2}$ ; for air,  $\mathcal{E}_{air} = 1$  and for Si,  $\mathcal{E}_{si} = 11.9$ .

| nclosure M   | daterial Defs.   | Dielectric    | Layers   Materials  | EM Layer Map      | ping Line Type    | Display |          |

|--------------|------------------|---------------|---------------------|-------------------|-------------------|---------|----------|

| Dielectric D | efinitions: (use | for dielectri | c layers)           |                   |                   |         |          |

| Name         | Er               |               | TanD                | Color             | Advanced Prope    | erties  | Add      |

| Si           | 112              | 9             | 0,001               |                   |                   |         | Remove   |

|              |                  |               |                     |                   |                   |         | Advanced |

| •            |                  |               |                     |                   |                   |         | •        |

| Conductor    | Definitions: (us | e for condu   | ictors, vias, and/c | r top/bottom bour | dary conditions)  |         |          |

| Name         | Sig              |               | Color               | Add               |                   |         |          |

| Al           | 3,5              | 3E+17         |                     |                   |                   |         | Remove   |

| Al_Air_Brid  | ge 3,5           | 3E+17         |                     |                   |                   |         | Advanced |

|              |                  |               |                     |                   |                   |         | Advanced |

| •            |                  |               |                     |                   |                   |         | Þ.       |

| Impedance    | Definitions: (u  | se for cond   | uctors, vias, and/  | or top/bottom bou | ndary conditions) |         |          |

| Name         | Re               | sSq           | ResF                | React             | Color             |         | Add      |

|              |                  |               |                     |                   |                   |         | Remove   |

|              |                  |               |                     |                   |                   |         |          |

|              |                  |               | orox Open, Inf WG   |                   |                   |         |          |

(a)

| nclosure  | Material Defs. | Dielectric | Layers    | Materials    | EM Layer Map       | ping   | Line Type | Display            |                     |

|-----------|----------------|------------|-----------|--------------|--------------------|--------|-----------|--------------------|---------------------|

|           |                | Dielectric | : materia | ls in the st | ackup (length sp   | ecifie | l in um)  |                    |                     |

|           |                |            | Thick     | ness M       | Aterial Definition | Dr     | aw Scale  |                    | Insert              |

|           |                | 1          | 2000      | A            | ir                 | 1      |           |                    |                     |

|           |                | 2          | 8.5       | A            | ir                 | 5      |           |                    | Delete              |

|           |                | 3          | 380       | S            | i                  | 1      |           |                    |                     |

|           |                | 4          | 2000      | A            | ir                 | 1      |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    | Ŷ                   |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    | Ŷ                   |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    |        |           |                    |                     |

| Substrate | Name:          |            |           |              |                    |        |           |                    |                     |

| SUB       |                | Top Bou    | ndary: 🖡  | Perfect Co   | nductor 👻          | Bot    | om Bounda | y: Perfect Conduct | or 🔻                |

|           |                |            | -         |              |                    |        |           |                    |                     |

|           |                |            |           |              |                    | -      |           |                    |                     |

|           |                |            |           |              | OK                 | Cano   | el        | Help Eleme         | nt Help Vendor Help |

(b)

| nclosure Material      | Defs. Dielect  | ric Layers Materials | EM Layer Ma    | pping Line Type Display |                  |

|------------------------|----------------|----------------------|----------------|-------------------------|------------------|

| daterial properties fo | or conductors, | vias, etc (length sp | ecified in um) |                         |                  |

| Name                   | Thickness      | Material Definition  | Etch Angle     | Roughness               | Insert           |

| Al                     | 0.4            | Al                   | 0              | 0                       | Delete           |

| Al_for_Air_bridge      | 2              | Al_Air_Bridge        | 0              | 0                       | Delete           |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         | _                |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         | _                |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      |                |                         |                  |

|                        |                |                      | ОК             | Cancel Help Elemen      | nt Help Vendor H |

(c) Fig.4.2: (a) Defining dielectric and metal properties in AXIEM. (b) Defining dielectric layers (c) Defining metal thickness and assigning metal properties.

Fig.4.3: AXIEM 3D CPW simulating structure on Si substrate with two 500µm air-bridges 5mm apart. Inset bottom left (air-bridge on CPW), inset top right (a differential port).

## 4.3 Simulation result

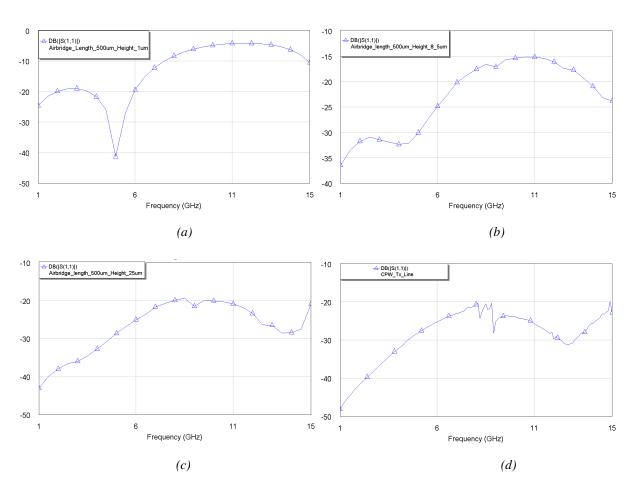

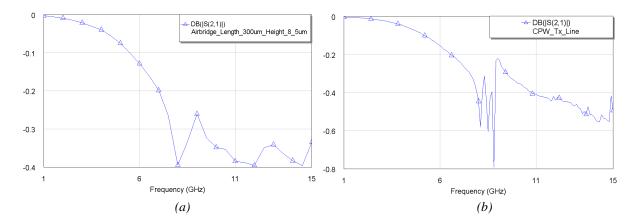

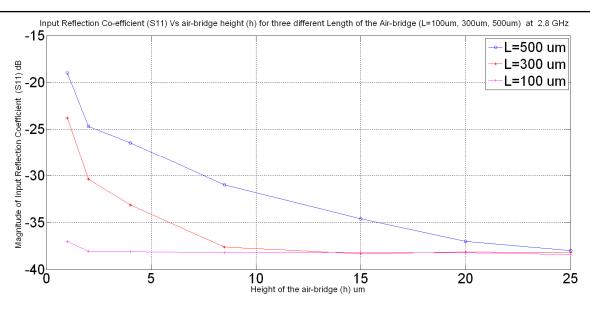

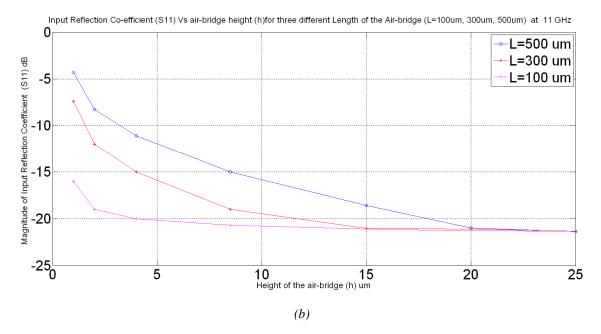

We simulated three different lengths for the air-bridges, 100µm, 300µm, 500µm each 60µm wide. We placed two air-bridges with the same length on the CPW transmission line, keeping a distance between them of 5mm. Seven different heights of the air-bridges 1µm, 2µm, 4µm, 8.5µm, 15µm, 20µm, 25µm were selected to see the effect of input reflection  $(s_{11})$  with air-bridge height. The input reflection  $(s_{11})$  for the 500µm long, 1µm high air-bridge in Fig.4.4 (a) shows that there are two significant reflections at 2.8 GHz and at 11 GHz. These two reflections can be reduced for the same 500µm long air-bridge by increasing their height (see Fig.4.4). The input reflection  $(s_{11})$  of CPW transmission line with air-bridge length 500µm, height 25µm (see Fig.4.4(c)) is almost same as CPW transmission line without any air-bridge (see Fig.4.4 (d)) which is a sign of negligible reflection coming from the 500µm long air-bridge connected in parallel with the CPW transmission line when its height is chosen 25µm or more.

Fig.4.4: AXIEM EM simulation of input reflection co-efficient  $(s_{11})$  for 500 $\mu$ m long, 60 $\mu$ m width air-bridge with height (a) 1  $\mu$ m (b) 8.5 $\mu$ m (c) 25  $\mu$ m (d) CPW without air-bridge.

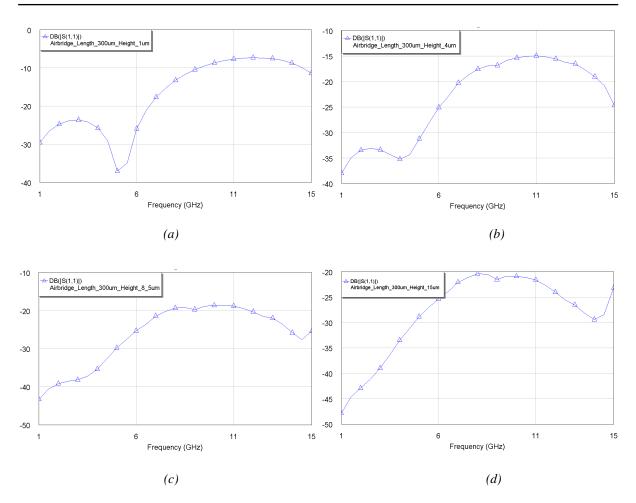

The effect of the air-bridge height on input reflection ( $s_{11}$ ) is shown in Fig.4.5 (a-d) for 300 $\mu$ m long air-bridges. A similar CPW like input reflection ( $s_{11}$ ) was obtained for 300 $\mu$ m long air-bridge at air-bridge height 15 $\mu$ m. The transmission coefficient ( $s_{21}$ ) of CPW with 300µm long, 8.5µm high air-bridge is shown in Fig.4.6 (a) which is very high, close to 0dB. The magnitude of the two reflections at 2.8 GHz and at 11 GHz with air-bridge height (h) is shown in Fig.4.7(a-b) for three different lengths (L=100µm, 300µm, 500µm) of the airbridges. For both frequencies the input reflection  $(s_{11})$  decreases inversely with the increasing height of the air-bridge and becomes independent of the height at large value of h, where the value of added shunt capacitance is close to zero. At the same height of the airbridge, input reflection  $s_{11}$  increases with the increasing air-bridge length (see Fig.4.7 (a-b)) which is clearly due to the increasing size of the added shunt capacitance and supported by the equation (3.10). To get the same minimum input reflection  $(s_{11})$  -21dB at 11 GHz coming from a 100µm long, 8.5µm high air-bridge, the height of the 300µm long air-bridge should be increased to 15µm and 500µm long air-bridge should be increased to 25µm (see Fig.4.7 (b)). Hence, it is clear from the simulation that same minimum amount of input reflection  $(s_{11})$  of the small air-bridge can be obtained from long air-bridge just by increasing their height, h.

Fig.4.5: AXIEM EM simulation of input reflection co-efficient  $(s_{11})$  for 300 $\mu$ m long, 60 $\mu$ m width air-bridge with height (a) 1  $\mu$ m (b) 4  $\mu$ m (c) 8.5  $\mu$ m (d) 15 $\mu$ m.

Fig.4.6: AXIEM EM simulation of transmission co-efficient  $(s_{21})$  for (a) 300 $\mu$ m long, 60 $\mu$ m width air-bridge with height 8.5 $\mu$ m (b) CPW without air-bridge.

*(a)*

Fig.4.7: Magnitude of input reflection  $(S_{11})$  Vs air-bridge height (h) for three different length of the air-bridge  $(L=100\mu m, 300\mu m, 500\mu m)$  (a) reflection at 2.8 GHz (b) reflection at 11 GHz.

# **Chapter 5**

# Fabrication of long and high air-bridge

## 5.1 Challenges of fabricating long and high air-bridges

Fabricating a long and high air-bridge is challenging due to difficulties in keeping the airbridge mechanically stable when its length or width goes above a couple of hundred microns. The probability of the air-bridge collapsing increases with the increasing length and height. If the length of the air-bridge is very large compare to its height (high aspect ratio) then it becomes very difficult to remove the resist beneath the air-bridge. All the above problems can be solved if a long and high air-bridge is fabricated with a thick metal layer. However, a very thick metal layer demands thick liftoff resist which is expensive and not always compatible with other photoresists available in the process lab.

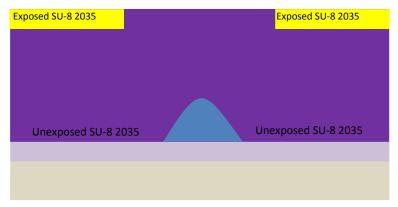

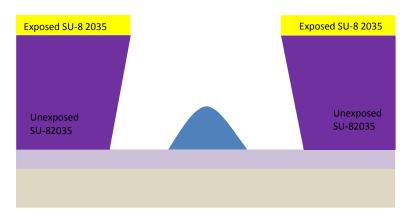

### 5.2 Developing a recipe for fabrication

We developed a process for fabricating long and high air-bridges. In our process, there is a support resist layer for getting the height of the air-bridge and there is an air-bridge layer which is used as a liftoff layer for getting undercut (see Fig.5.1). The process can be used getting large undercut for depositing aluminum up to 4 $\mu$ m. Thick aluminum layer ensures mechanical strength of the air-bridge of length up to couple of *mm* and height up to 15 $\mu$ m. The detailed fabrication methods are demonstrated in the following sections.

## **5.3** Selecting a suitable process for fabrication

Fabrication of the air-bridges on a CPW a multi resists layer process. The process of one layer (resist, developer, ambient) may influence the process of next layer. For example, if someone uses AZ series positive photoresist as an air-bridge support beneath the SU-8 2035 air-bridge layer, then the support layer would be diffused into SU-8 and during development of SU-8 2035 the support layer might be attacked. The photoresist of one layer must be compatible with the next layer, and one resist developer must not attack the other resist layer in order to avoid undesired development. It is very important to choose the proper resist, developer etc. of each layer so that there is no intermixing to the intermediate layer. We choose PMGI SF15 as a support layer in order to avoid intermixing of the support with SU-8 2035 air-bridge layer since they are compatible with each other.

## 5.4 Selecting proper photoresist

### 5.4.1 Selecting a suitable resist for support layer

The height of the air-bridge is determined by the height of support span. Resist with a high viscosity usually gives a thick layer after spin coating. Hence, the supporting photoresist must have high viscosity to ensure the desired height of the air-bridge. The photoresist must be positive to get better support, since positive photoresist gives a positive sidewall profile (see Fig.5.2 (f)) for the support after development which is important for getting nice step coverage of the side wall if 0° angle evaporation is used. Negative photoresist may work, but in this case it is important to ensure that the sidewall profile must not be negative, otherwise the step coverage would be impossible. In the case of negative photoresist, the exposure dose must be chosen in such a way so that the sidewall profile becomes almost vertical. However, here we used the positive resist PMGI SF15 to get support of the air-bridge as it gives a positive sidewall profile and it is also the most viscous positive photoresist available in our lab which ensures the desired height of the air-bridge. SF15 is entirely insoluble into most photoresists and compatible with them. Having high thermal stability makes it perfect for a high temperature metal deposition process, which is another reason selecting this resist for making the air-bridge support. PMGI SF15 is also transparent, which makes it very convenient to perform mask alignment to the intermediate layer.

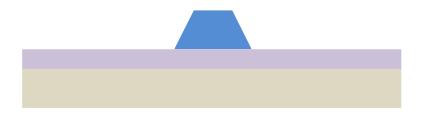

### 5.4.2 Selecting a suitable resist for getting liftoff for thick aluminum film

A long and high air-bridge requires strong mechanical support coming from its sidewalls as well as the thickness of the air-bridges. In our case, the height of these air-bridges is 8.5µm~15µm and length of these air-bridges is 100µm~ 500µm. A thick aluminum layer is essential for making these air-bridges stable. We used 2µm thick aluminum for ensuring proper mechanical strength of the air-bridge. 2µm thick aluminum deposition requires undercut height greater than 2µm but for the purpose of making 8.5µm high air-bridge undercut must be greater than 10.5µm (2µm for aluminum thickness+8.5µm for air-bridge height). Similarly, in order to make 15µm high air-bridge undercut height must be chosen greater than 17µm. A 3D animation of the support and the air-bridge layer with undercut height less than 8.5µm and greater than 10.5µm is shown in Fig.5.1 (a-b).If undercut layer (blue) is chosen less than 10.5µm then liftoff will be impossible since the support layer (orange) and the air-bridge layer (pink) will be joined together by aluminum (see Fig.5.1 (a)). If the undercut layer height is larger than 10.5µm then the support and the air-bridge will be separated by undercut (see Fig.5.1 (b)). We used SU-8 2035 for getting a thick liftoff resist layer which ensures undercut height greater than 10.5µm (17µm for 15µm high air-bridge). Although SU-8 2035 is a negative photoresist, it can be used for a single layer liftoff process by controlling the dose, whereas unexposed SU-8 2035 acts as a sacrificial layer [9].

(b)

Fig.5.1 : 3D animation of the support layer (orange) and air-bridge resist layer (pink) with (a) Undercut (blue) <8.5µm but greater than 2µm (b) Undercut (blue) >8.5µm.

### 5.5 **Processing for the air-bridge support layer**

### 5.5.1 Photolithography for the support layer

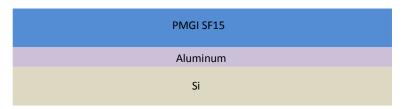

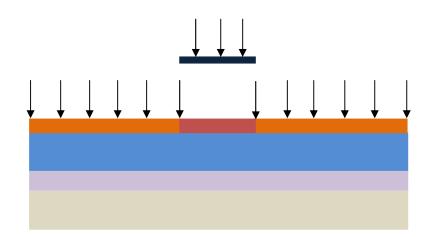

To support the air-bridge we used PMGI SF15 and employed a "Bilayer Lift-Off Process" (see Fig.5.2 (a-g)). In this process PMGI SF15 was coated on top of aluminum @ 2000 rpm for 5s. Although it is not usual to get SF15 thickness greater than 3µm @ 2000 rpm for 45s spinning time, however, we choose the spinning time only 5s to get SF15 layer as thick as 8.5µm. Reducing the spinning time can cause two main problems on the support layer. First, the support layer may suffer uniformity problem. However, uniformity is not a big issue for us if the height of the support layer goes above 8.5µm. Second, there might be some air bubbles trapped in the SF15 resist. These two problems can be solved easily if we keep the wafer with spin coated SF15 on top of the chuck for 10 minutes prior to baking it. In this way, first problem of having poor uniformity can be solved since the resist flows from thicker part to the thinner part until an equilibrium thickness is reached. In this way, a better uniformity will be obtained after 10 minutes. The second problem can be solved since air bubbles will disappear gradually with time. The prebake temperature is chosen to be 160°C which is lower compare to the other recommended prebake temperature of the datasheet. This temperature is chosen to ensure a large amount of undercut which is required to get a flat positive sidewall of the support span (see Fig.5.2 (d)). A comparatively lower temperature increases the dissolution rate, whereas a higher temperature (>160° C) will make the dissolution rate slower. Higher dissolution rate is required for getting the entire SF15 layer beneath the exposed imaging photoresist to be removed, since less aggressive developer MF319 is used for developing both the imaging resist and SF15 simultaneously. If dissolution rate is slower then development time will be longer. A longer development time will overdevelop the imaging resist.

Fig.5.2 (a): PMGI SF15 coating on top of aluminum.

Fig.5.2 (b): Imaging photoresist S1813 coating on top of PMGI SF15.

Fig.5.2 (c): Exposing the imaging photoresist for creating the pattern in the PMGI SF15 support.

*Fig.5.2 (d): After developing both the imaging resists and the PMGI SF15.PMGI develops isotropically, creating a positive sidewall profile.*

Fig.5.2 (e): Flood exposure to remove the imaging resist on top of the PMGI SF15 support.

Fig.5.2 (f): Developing the flood exposed imaging resist to get the PMGI SF15 support Span.

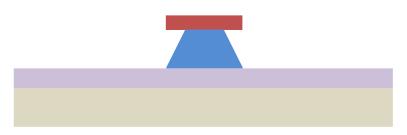

Fig.5.2 (g): Heating PMGI SF15 Support to get a smooth positive sidewall.

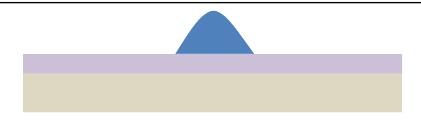

Fig.5.3: MA6 mask aligner used for exposure of the photoresist.

### 5.5.2 Photoresist development

As mentioned before we used less aggressive developer MF319 to develop SF15 support and imaging photoresist. The development time is very crucial from the dissolution point of view since we need to develop the entire 8.5µm thick SF15 which is coated on top of the aluminum (a metal sensitive to MF319). If the development time is a little bit longer than the optimum development time, then MF319 will start attacking the aluminum beneath the SF15 and dissolve it quickly. The development after the flood-exposure using MF319 is also very crucial because if the development time is little bit longer than optimum development time then it will start dissolving SF15 from the top side of the support since the dissolution rate is high.

### 5.5.3 **Reflow for the support**

As mentioned before, the sidewall profile of the air-bridge support is very important for getting desirable step coverage during the aluminum film deposition. The sidewall profile should be positive, flat and round shaped to get better step coverage. A vertical sidewall profile may work for air-bridge height up to 3  $\mu$ m or less but when the height of the air-bridge is greater than 5 $\mu$ m which is usually our case then a vertical sidewall profile of the air-bridge is still a problem from an aluminum deposition point of view as it does not cover the step properly. For a vertical sidewall of the air-bridge one must use angle evaporation for getting better step coverage. But one drawback of angle evaporation is having a poor liftoff process. It is also difficult to ensure uniform thickness of aluminum for the air-bridge using angle evaporation. Hence, heating the created SF15 support span is important since the height of this span is 8.5 $\mu$ m. After heating, the sidewalls become smooth and round shaped (see Fig.5.2 (g)) which ensures better step coverage for metal deposition at 0° angle. It also gives a better thermal stability to SF15 for the subsequent high temperature metal deposition process.

## 5.6 **Processing for the air-bridge layer**

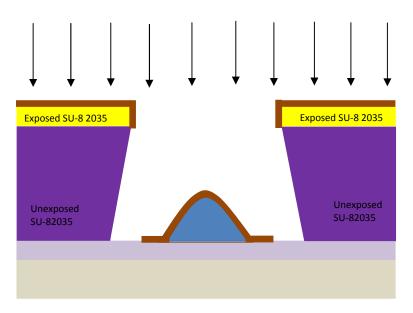

### 5.6.1 Photolithography for the air-bridge layer

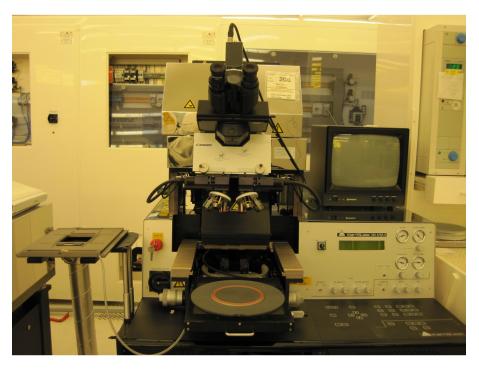

The photolithography process for creating an opening of the air-bridge support is shown in Fig.5.4 (a-d). SU-8 2035 was chosen for the single layer liftoff process. There are two advantages of using SU-8 2035. First, large undercut higher than 10.5µm (or 17µm for 15µm high air-bridge) can be obtained if it is underexposed by UV light or broad band emission. Second, the developer for SU-8 2035 attacks neither aluminum nor the SF15 at all. The only problem if it is cross linked heavily then tough to remove it from the wafer. However, in our case we used underexposed SU-8 2035 which is easily removable by 1165 remover. In the beginning of this process SU-8 2035 was spin coated and prebaked. It was underexposed using broadband emission to get the desired undercut (>10.5µm). The exposure time is very important and must be optimized. For 32.5µm thick SU-8 2035 the required dose is 150  $mJ/cm^2$  (350nm-400nm wavelength UV light) [10]. The output light intensity of the Hg lamp of the MA6 mask aligner shown in Fig.5.3 is 5 mJ/cm<sup>2</sup>/sec. Roughly 30s is required to expose the 32.5µm thick photoresist layer. However, if the exposure time is chosen to be 30s, then no unexposed SU-8 2035 resist will be there to get the desired undercut. On the other hand, if the exposure dose is too short then unwanted cracks will form after development using the SU-8 developer. We optimized the dose to 11s. The dose was chosen such a way so that light absorbed only above 10.5µm (8.5µm for support height+2µm for aluminum thickness) from the bottom of the surface which makes an undercut height more than 10.5µm (see Fig.5.4(c)). The advantage of using broadband emission instead of UV light is that it ensures a negative sidewall profile for the undercut which is desired for the final liftoff process. Broadband emission (250nm-450nm) contains both UV light (350 nm-400 nm) and DUV light (240nm-290nm). The shorter wavelength (higher energy) DUV light absorbs near the top portion of the resist film having high absorption coefficient of it and cannot reach to the bottom portion of the resist film. The top portion of the resist film is exposed by DUV and UV light while bottom portion is exposed only by UV light. As a result the top portion is overexposed while the bottom portion remains underexposed. This creates a negative sidewall profile or T-topping (see Fig.5.4 (d)) [10]. For our case the whole spectrum of light (250nm-450nm) was absorbed only above  $10.5\mu$ m.

*Fig.5.4 (a): Spin coating SU-8 2035 on top of the PMGI SF15 support layer. The resist was prebaked at 65°C (for first 2 minutes) and 95°C (for next 5 minutes).*

Fig.5.4 (b): Underexposed SU-8 2035 using broadband emission.

Fig.5.4(c): Post exposure bake of SU-8 2035.

Fig.5.4 (d): Development of the unexposed SU-8 2035 to get the desired undercut

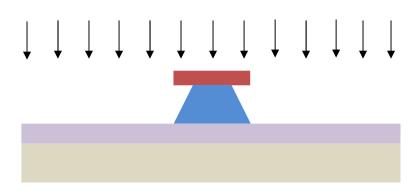

Fig.5.4 (e): Depositing aluminum at  $0^{\circ}$  angle.

Fig.5.4 (f): Final liftoff for removing excess aluminum.

### 5.6.2 Development of the air-bridge layer

After the exposure of SU-8 2035 it was required to bake it at certain temperature. Because of this post exposure bake, only the exposed SU-8 2035 was heavily cross linked and the chemical properties of the unexposed SU-8 2035 remained the same (see Fig.5.4 (c)). During the development of SU-8 2035 using SU-8 developer only the unexposed resist was developed and created the opening of the air-bridge (Fig.5.4 (d)).

## 5.7 Thin aluminum film deposition

To deposit a pure aluminum film on top of the support span we used Plassys electron gun evaporator which is shown in Fig.5.5. It is capable of maintaining  $0^{\circ}$  angle evaporation very precisionly thus prevents any unwanted deposition of aluminum on the SU-8 2035 negative sidewall (see Fig.5.4 (e)). Evaporating thick aluminum film requires high deposition rate. However, if the deposition rate is high enough then thermal loads on top of support also increases which can damage the support resist. As SF15 is thermally very stable, a deposition rate of 1 nm/s can be used to get total aluminum thickness of 2µm. As mentioned before  $0^{\circ}$ angle evaporation was used in order to get uniform thickness of aluminum. In addition to this it ensures an easy liftoff process whereas angle evaporation makes the liftoff hard.

Fig.5.5: Plassys electron gun evaporator used to deposit 2µm thick aluminum film.

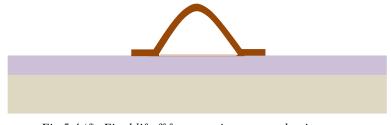

## 5.8 Liftoff and final drying of the air-bridges

In order to remove the excess aluminum on top of the air-bridge layer the sample must be kept in 1165 remover (immersion mode) and heating the remover at 75°C temperature for 90 minutes. Strong shaking and agitation the sample with regular intervals and several times rinsing with 1165 remover from a bottle is also required to remove the uncrosslinked SU-8 2035 resist from the surface thus preventing any further re-deposition on it. If the removal rates drop significantly then used 1165 remover must be replaced by clean 1165 remover to increase the removal rate again. Long time heating without agitation must be avoided since very little underexposed SU-8 2035 can be cross linked by long time heating and can be stacked on the aluminum CPW which is hard to remove later. The easiest way to get rid of this problem and having a clean liftoff process is to use  $OmniCoat^{TM}$  (an organic polymer) beneath SU-8 2035 surface [10]. OmniCoat<sup>TM</sup> acts as a barrier between SU-8 2035 and the wafer which protects the wafer from cross linked SU-8 contamination. In addition, it promotes adhesion and ensures better liftoff [11]. Piranha etches  $[H_2SO_4:H_2O_2 \text{ mixture}]$  can be used to get rid of cross linked SU-8 but piranha reacts with aluminum and dissolves it very quickly. Burning the wafer at 650°C temperature inside a hot furnace can also remove cross linked SU-8 from the surface [12] but it won't work for aluminum since at this temperature our aluminum CPW will reach its melting point and will be melted.

After liftoff in 1165 remover the sample must be immersed in IPA very quickly instead of rinsing or washing it by distilled water. As water has high surface tension the water beneath the air-bridge may pull the aluminum layer downward while it starts drying and causes the air-bridge to collapse. On the other hand, IPA has low surface tension which cannot produce sufficient force to pull the aluminum layer downward. It is not required to dry the air-bridge using nitrogen blow if IPA is used instead of water, as it dries automatically at the environment within  $5 \sim 10$  minutes.

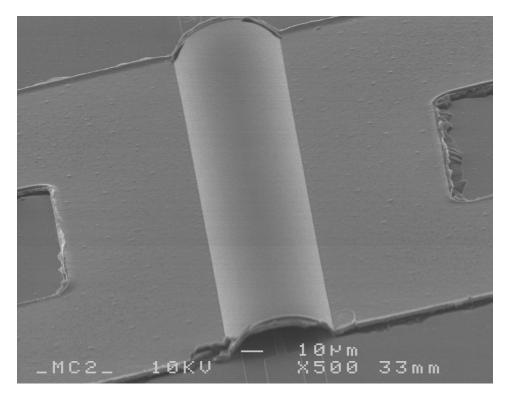

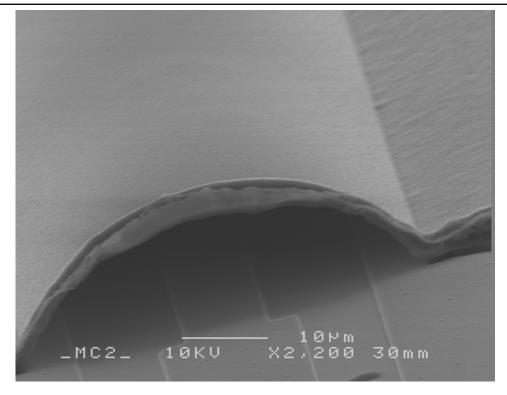

## 5.9 Characterization of fabricated air-bridges

Observing SEM images of fabricated air-bridges in Fig 5.6 (a-e) it is clear that support resists was cleared entirely beneath these air-bridges after the final liftoff process. The height of these air-bridges is about  $8.5\mu$ m and the thickness of aluminum layer  $2\mu$ m. The effect of the reflow for making air-bridge support span round shaped is clearly visible from SEM images (see Fig.5.6 (e)). Further characterizing the fabricated air-bridges we used Keithley 4200 SCS Parameter analyzer to perform two port measurements between CPW centre conductor and air-bridge which ensured that the air-bridge did not touch the CPW centre conductor. Beside this we used another two port measurement setup between air-bridge and ground plane which ensured perfect electrical contact of these air-bridges with the ground planes.

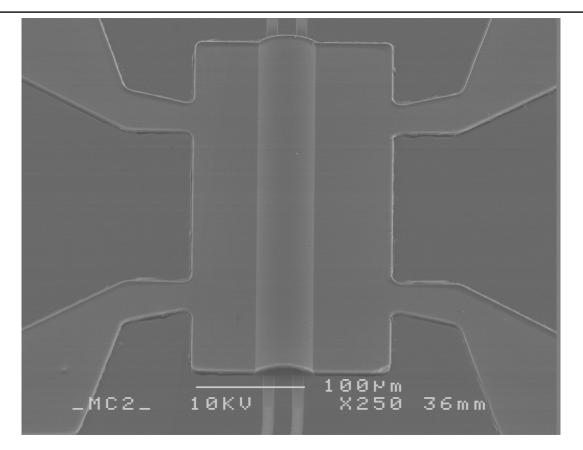

Fig.5.6 (a): Top view of 500µm long, 60µm wide air-bridge on top of CPW connecting two ground plane. The height of the air-bridge is 8.5 µm.

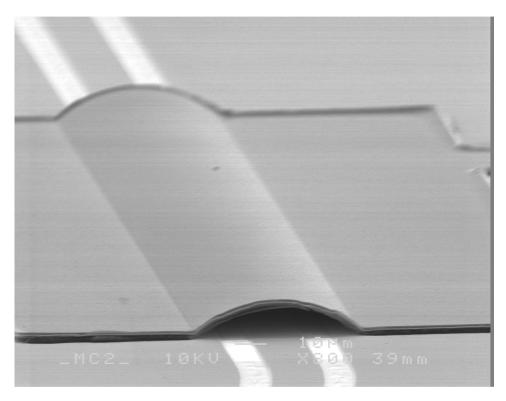

Fig.5.6 (b): A 300µm long, 60µm wide air-bridge on top of CPW connecting two ground planes. The height of the air-bridge is ~8.5 µm.

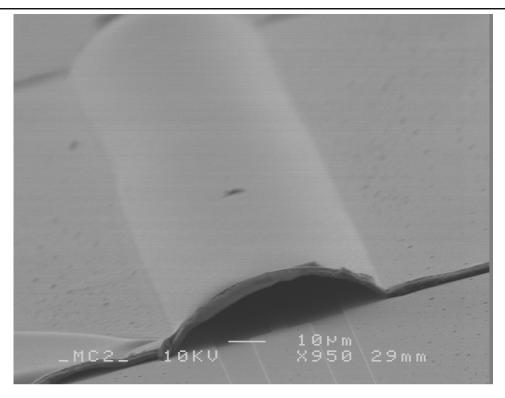

Fig.5.6 (c): A 300µm long, 60µm wide air-bridge on top of CPW. The height of the bridge is ~15 µm.

Fig.5.6 (d): A 500µm long, 60µm wide air-bridge on top of CPW. The height of the air-bridge is ~15 µm.

Fig.5.6 (e): No support resist beneath  $\sim 15 \mu n$  high air-bridge after the final liftoff process.

# **Chapter 6**

### Measurement

### 6.1 Microwave setup for cryogenic measurement

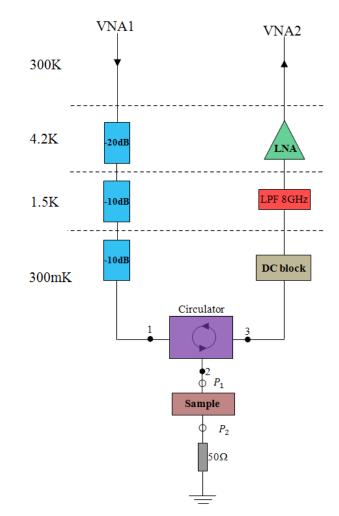

Fig.6.1: A Schematic of the microwave setup in the He-3 cryostat. The blue squares are microwave attenuators with the attenuation indicated in dB. The low noise amplifier (LNA) has a gain of 38dB. The low pass filter (red) is indicated with its cutoff frequency.

In order to measure the input reflection coefficient  $(S_{11})$  of the CPW with air-bridges at cryogenic temperature, we used a microwave setup as shown in Fig.6.1. Fig.6.1 is a reflection measurement setup since the input signal comes from the Vector Network Analyzer's port-1 (VNA1) incident at port  $(P_1)$  of the sample and the signal reflected from port  $(P_1)$  of the sample is after amplification measured by the port-2 of the Vector Network Analyzer (VNA2). Hence,  $S_{21}$  measured by the VNA is actually the  $S_{11}$  measurement for the sample. The detailed circuit operation will be discussed in the next section. There are three temperature stages in the cryostat, 4.2K, 1.5K and 300mK. The Vector Network Analyzer where the signal comes from was at room temperature (300K). A -20dB attenuator and Low Noise Amplifier (LNA) with gain 38dB was mounted at 4.2K temperature stage. A -10dB attenuator and Low Pass Filter (LPF) with cut-off frequency 8 GHz was placed at the 1.5K temperature stage. The sample, the circulator, -10dB attenuator, dc block and 50 $\Omega$  termination were placed at the 300mK temperature stage. 300mK is the base temperature of this cryostat.

#### 6.2 Working principle of the measurement setup

The noise which comes from the thermal radiation at room temperature and also comes from the MW components, cables and connectors at different temperature stages must be attenuated so that they cannot reach in the base temperature stage where the sample is connected. All these thermal noises at different temperature stages must be reduced in order to increase the Signal to Noise Ratio (SNR). The thermal noise only depends on the temperature of the stage and independent of the signal power coming from the VNA. Although it seems that it is possible to increase the SNR by simply increasing the signal power when noise is fixed but in practical measurement it is not possible to increase the signal power above a certain limit since high power signal can damage the MW components and it is not allowed for the safety of the electronics. In fact, high power signal can be dissipated as heat in the co-axial cables since they have certain amount of attenuation which may heat up the lower temperature stages having lower cooling power there. Hence, we must attenuate the thermal noise instead of increasing the signal power to improve the SNR. For this purpose, we must use attenuators which are basically dissipative filters at different temperature stages [19] [20] [21].

The thermal noise power (P) is defined by the equation (6.1)

$$P = K_B T B R \tag{6.1}$$

Where T=temperature of the stage, R=resistance of the MW component or co-axial transmission line, B=bandwidth of the thermal noise,  $K_B$ =Boltzman constant.

The noises which are generated at 300K, 4.2K, 1.5K and 300mK stages can be calculated using equation (6.1) and can be written in equation (6.2), (6.3), (6.4) and (6.5) respectively assuming the bandwidth B of the noise is same at different temperature stages.

$$P_{300K} = 300K_B B Z_o \tag{6.2}$$

$$P_{4.2K} = 4.2K_B B Z_o (6.3)$$

6.2 Working principle of the measurement setup

$$P_{1.5K} = 1.5K_B B Z_o \tag{6.4}$$

$$P_{300mK} = 0.3K_B B Z_o \tag{6.5}$$

The ratio of the noise power at 4.2K to 300K stage  $\left(\frac{P_{4.2K}}{P_{300K}}\right)$  is (1/71). Hence, we need to use an attenuator at 4.2K stage which can attenuate the noise power coming from 300K stage by 1/71 or less. For this purpose, we used -20dB attenuator which can attenuate noise power by 1/100 using equation (6.6).

$$dB = 10 \log_{10}(\frac{P_0}{P_i}) \tag{6.6}$$

Where,  $P_o$ =thermal noise power of a certain cold temperature stage,  $P_i$ =thermal noise power of the previous cold temperature stage.

Thus, at 4.2K stage there are two noise powers, one is generated at 4.2K stage and the other is the attenuated noise power  $(\frac{P_{300K}}{100} < P_{4.2})$  which is coming from the 300K stage. Since thermal noise directly proportional to the temperature of the stage, the total noise power in 4.2K stage is now less than the noise power coming from 300K stage. Similarly, the ratio of the thermal noise in 1.5K to 4.2K stage  $(\frac{P_{1.5K}}{P_{4.2K}})$  is (1/2.8). So, according to equation (6.6) a -4.47dB attenuator should be used but we used a -10dB attenuator which is available in lab. Thus a -10dB attenuator is used in 1.5K stage to keep the noise power coming from 4.2K stage less than the noise power of 1.5K stage. For similar reason, we used a -10dB attenuator in 300mK stage to keep the noise power coming from 1.5K stage lower than the noise power in 300mK stage. Since thermal noise directly proportional to the temperature of the stage, the noise power at 300mK stage is the lowest compare to the previous higher temperature stages. Hence, by attenuating the noise power at different temperature stages, we can get high SNR without increasing the signal power.

However, it would be best if we could use a -30dB attenuator  $\left(\frac{P_{300K}}{P_{300K}}\right) = \frac{1}{1000} = -30dB$  in the 300mK stage to reduce the noise coming from the higher temperature stages because by this way we could also reduce the noise generated from the attenuators themselves which is the minimum at the lowest temperature. But, if we do that then all thermal noises coming from previous higher temperature stages will be dissipated as heat in 300mK stage. Since the cooling power of 300mK stage is the lowest, this large dissipated noise power may generate heat which will raise the temperature of this stage. On the other hand, if we use all the attenuator in the 4.2K stage then there will be no attenuator to attenuate the thermal noises which are generated in the subsequent lower temperature stages. Hence, the noise power of 4.2K stage is much lower than the 300K stage, additional attenuation of noise power at 4.2K stage may raise the temperature of this stage.

If we choose a -10dB attenuator instead of a -20dB attenuator at 4.2K stage then the attenuated noise power coming from 300K stage would be higher than the noise power at 4.2K stage,  $\left(\frac{P_{300K}}{10} > P_{4.2K}\right)$ . Hence, to attenuate this large noise power  $\left(\frac{P_{300K}}{10}\right)$  at 1.5K stage, additional attenuator must be added in the 1.5K stage. Thus, more power will be attenuated

and dissipated as heat in 1.5K stage. As the cooling power of 1.5K stage is very small, it might heat up the 1.5K stage.

After -10dB attenuation in 300mK stage, the signal was passed through a microwave circulator. The signal power circulates from port 1 to port 2 and arrive at the sample's input port ( $P_1$ ). The reflected signal power from port ( $P_1$ ) circulates from port 2 to port 3 but no reflected power will be circulated from port 2 to port 1. The port 2 of the sample ( $P_2$ ) was grounded by a 50 $\Omega$  resistor to ensure zero power incident at this port.

The signal at port 3 of the circulator was passed through a dc block and a LPF. Since the signal was attenuated three times, it must be amplified using a LNA with large gain prior to send it to VNA2 for measuring. Since microwave circulator does not work at dc (f=0), the dc block capacitor is required to block dc currents coming from the biasing circuit of the LNA. Hence, biasing current cannot circulate from port 3 to port 1 of the circulator and prevents mixing with the incident signal. Having a LPF with cutoff frequency 8GHz before LNA, any high frequency signal or noise comes from LNA will be filtered. However, the LNA was placed at 4.2K instead of 1.5K or 300mK stage to avoid heating of the lower temperature stages.

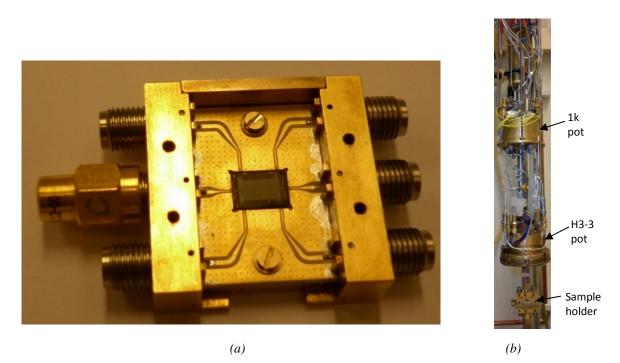

*Fig.6.2: Sample bonded in the sample holder (a), sample holder connected with the sample mount close to the He-3 pot (b).*

#### 6.3 Measurement result

Before performing the measurement the sample was bonded with gold bonding wires to the sample holder to connect it with the microwave circuits (see Fig.6.2 (a)). A Helium-3 cryostat was used during measurement which operates with a base temperature of 300mK. The sample was mounted in the Inner Vacuum Chamber (IVC) which was kept inside a liquid Helium-4

bath to cool it at 4.2K (see Fig.6.2 (b)). The detailed construction and cooling mechanism of Helium-3 cryostat can be found in [17] [18]. However, we only reached at 4.2K temperatures.

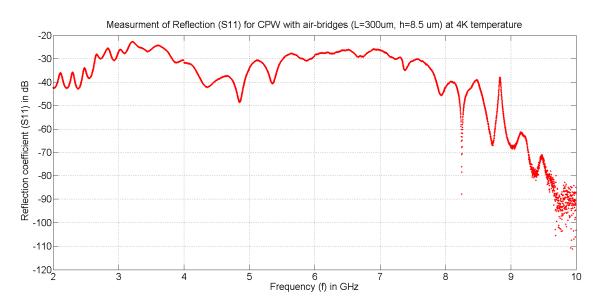

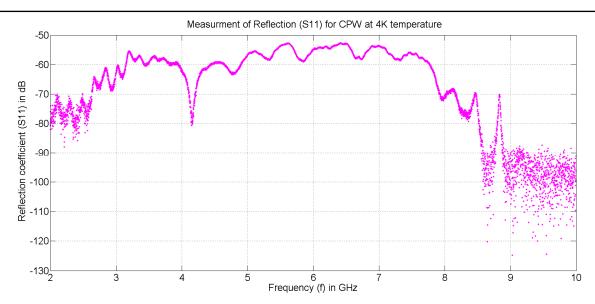

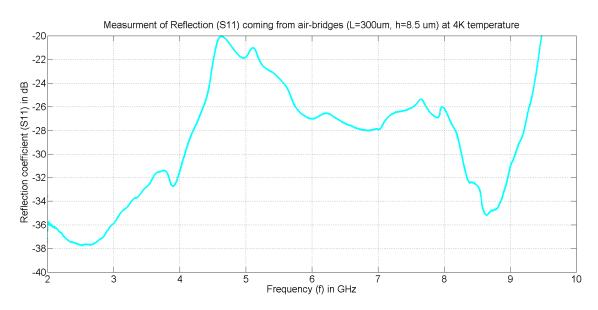

During the measurements, it was hard to measure the actual reflection coming from the air-bridges since there were lots of reflections coming from the microwave co-axial cables, connectors and even from the other microwave components like attenuators, circulator etc. In addition, there is a significant amount of reflection coming from the gold bonding wires of the contact pad having an impedance mismatch at the contact. In order to measure the accurate reflection coming from the air-bridges, we first measured the reflection of a sample CPW with air-bridges (L=300 $\mu$ m, h=8.5 $\mu$ m) (see Fig.6.3). Three different reflections were included in that measurement. First, the reflection from the air-bridges, second, the reflection from the gold bonding wires and third, the reflections from the whole microwave setup. To exclude these reflections coming from bonding wires and microwave setup, we measured another sample with identical CPW structure but without any air-bridges (see Fig.6.4). The second measurement gives the reflection coming from bonding wires and same microwave setup. Subtracting the two measurement data gives net reflection coming from air-bridges (see Fig.6.5).

Fig.6.3: Measurement of the reflection for CPW with air-bridges (L=300µm, h=8.5µm) at 4K temperature.

Fig.6.4: Measurement of the reflection for CPW at 4K temperature.

Fig.6.5: Reflection from the air-bridges (L=300µm, h=8.5µm) at 4K temperature.

The bandwidth of the circulator and LNA we used for this measurement was 4GHz-8GHz. Hence, the measured reflection coefficient  $(S_{11})$  within 4GHz-8GHz is the actual reflection which comes from the air-bridges at 4K. From Fig.6.5, we can see, within 4GHz-8GHz, the input reflection  $(S_{11})$  comes from the air-bridges (L=300µm, h=8.5µm) at 4K is below -20dB which confirms negligible reflection coming from these air-bridges.

## **Chapter 7**

### **Conclusion and future work**

In this thesis work, we simulated, fabricated and measured superconducting air-bridges which is expected to be a part of future quantum electrical circuit for improving their performance. The air-bridge was modeled by lumped circuit element shunt capacitance and included with the equivalent transmission line circuit for seeing their influence. Its length, width and height were identified as designing parameters for getting minimum shunt capacitance. For the purpose of equalizing the ground potentials throughout the structure, the length of this airbridge must be chosen free by which makes its height the only variable to get optimum performance. High precision 3D EM simulation indicates that the air-bridge height should be chosen as high as possible in order to keep reflection at a minimum level.

Final device fabrication was guided by the result of EM simulation. From fabrication point of view, it was tough and challenging to fabricate these long and high aluminum airbridges. Finally a fabrication method was successfully developed to make long and high airbridges (L~500 $\mu$ m, h~15 $\mu$ m). SEM images of these air-bridges confirm their mechanical stability and electrical property was verified by two port measurement. At the end, cryogenic temperature MW measurements show minimum reflection coming from these air-bridges which is a good sign for using these high aluminum air-bridges in future quantum electrical circuits.

In the future the same superconducting air-bridges would be fabricated in complex quantum electrical circuit with qubits to see the performance of the whole circuit at cryogenic temperature. The developed fabrication method can be used to make air-bridges higher than  $15\mu$ m, by increasing the height of the liftoff layer, controlling the dose and increasing the thickness of the deposited aluminum. These aluminum air-bridges can be used in any superconducting quantum electrical circuit for other purposes and for other device fabrication. For example, these high aluminum air-bridges can be used as superconducting inductor which might be used in future quantum processor.

# Appendix

### A. Detail recipe for fabrication

#### **Cleaning the Wafer:**

- i) 1165 remover, 75 °C, 10 min

- ii) Ultrasonic bath, P=100%, 1 min

- iii) IPA bath , 2 min circulation

- iv) QDR bath

- v) Blow dry with  $N_2$  gas

#### Photolithography of gold contact pad:

- i) Stripping plasma etching in Batchtop, 1 min, 250W, 40 sccm  $O_2$

- ii) Spin coat HMDS Primer @ 3000 rpm, 1 min, *t<sub>acc</sub>*=1500 ms

- iii) Soft bake 1 min @ 110 °C

- iv) Spin coat LOR3B @ 3000 rpm, 1 min,  $t_{acc}$ =1500 ms (~350*nm*)

- v) Soft bake 5 min @ 200 °C

- vi) Spin coat S1813 @ 3000 rpm, 1 min, t<sub>acc</sub> =1500 ms (~150*nm*)

- vii) Soft bake 2 min @ 110 °C

- viii) Expose 8.5s (250nm-450nm), at LoVac mode, alignment gap 20 µm

- ix) Develop 30s in MF319 with shaking

- vi) QDR bath 2 min

- vii) Blow dry with  $N_2$  gas

#### **Deposition of gold contacts:**

- i) Ashing in  $O_2$  plasma, for 10s, 50 W

- ii) Electron beam evaporation, (Baltzer BAK 600), P<sub>ch</sub>≤10<sup>-7</sup> mbar Sticking layer: 30 Å of Ti, 2 Å/s Contact layer: 800 Å of Au, 5 Å/s Stopping layer: 100 Å of Pd, 2 Å/s

- iii) Lift-off excess metals in 1165 Remover @ 75 °C, for 1 hour

- iv) Clean in IPA for 2 min

- v) Blow dry with  $N_2$  gas

#### **CPW Layer Photolithography:**

i) Ashing in  $O_2$  plasma, for 10 s, 50 W

- ii) Spin coat HMDS @ 3000 rpm for 1 min,  $t_{acc}$ =1500 ms

- iii) Soft bake @110 °C for 1 min

- iv) Spin coat LOR3B @ 2000 rpm for 30s,  $t_{acc}$ =1500 ms

- v) Soft bake 5 min @ 200 °C

- vi) Cool 1 min at environment

- vii) Spin coat LOR3B @2000 rpm for 30s,  $t_{acc}$ =1500 ms

- viii) Soft bake 5 min @ 200 °C

- ix) Cool 1 min at environment

- x) Spin coat S1813 @ 3000 rpm for 1 min, *t<sub>acc</sub>*=1500 ms

- xi) Soft bake @ 110 °C for 2 min

- xii) Expose 8.5s (250nm-450nm), at LoVac mode, alignment gap 20µm

- xiii) Develop 40s in MF319 with shaking

- xiv) QDR bath for 2 min

- xv) Blow dry with  $N_2$  gas

#### Deposition of aluminum thin film for CPW:

- i) Ashing in  $O_2$  plasma, for 10s, 50 W

- ii) Deposit 400nm aluminum using Plassys

- iii) Lift-off excess aluminum in 1165 remover @ 75 °C, for 2 hours

- iv) Rinse in IPA, 2 min

- v) Blow dry with  $N_2$  gas

#### PMGI SF15 Support for 8.5 μm high air-bridges:

- i) Ashing in  $O_2$  plasma, for 10 s, 50W

- ii) Spin coat SF15 @ 2000 rpm, for 5s,  $t_{acc}$ = 300 ms

- iii) Keep it on the spinner for 10 minutes for evaporating the air bubbles

- iv) Prebake @ 160 °C for 5 min

- v) Spin coat S1813 @ 3000 rpm for 30s, *t<sub>acc</sub>*=1500 ms

- vi) Prebake 2 min @ 110 °C

- vii) Expose 11s (250*nm*-450*nm*) at soft contact mode

- viii) Develop 3 minutes 55s in MF319 with shaking

- ix) QDR bath for 2 min

- x) Dry with  $N_2$  gas

- xi) Flood exposure for 8s (250nm-450nm)

- xii) Develop 10s in MF319 with shaking

- xiii) QDR bath for 2 min

- xiv) Blow dry with  $N_2$  gas

- xv) Ashing in  $O_2$  plasma, for 10s, 50 W

- xvi) Hard bake @ 250 °C for 5 min on hotplate.

#### PMGI SF15 Support for 15µm high air-bridges:

- i) Ashing in  $O_2$  plasma, for 10s, 50 W

- ii) Spin coat SF15 @ 2000 rpm, for 5s,  $t_{acc}$ = 300 ms

- iii) Keep it on the spinner for 10 minutes for evaporating the air bubbles

- iv) Prebake @ 160 °C for 5 min

- v) Spin coat SF15 @ 2000 rpm, for 5s,  $t_{acc}$ = 300 ms

- vi) Keep it on the spinner for 10 minutes for evaporating the air bubbles

- vii) Prebake @ 160 °C for 5 min

- viii) Spin coat S1813 @ 3000 rpm for 30s,  $t_{acc}$ =1500 ms

- ix) Prebake 2 min @ 110 °C

- x) Expose 11s (250*nm*-450*nm*) at soft contact mode

- xi) Develop 4 minutes 30s in MF319 with shaking

- xii) QDR bath for 2 min

- xiii) Dry with  $N_2$  gas

- xiv) Flood exposure for 8s (250nm-450nm)

- xv) Develop 10s in MF319 with shaking

- xvi) QDR bath for 2 min

- xvii) Blow dry with  $N_2$  gas

- xviii) Ashing in  $O_2$  plasma, for 10s, 50 W

- xix) Hard bake @ 250 °C for 5 min on hotplate

#### SU-8 2035 air-bridge layer:

- i) Spin coat SU-8 2035 @ 3000 rpm, for 30s, *t<sub>acc</sub>* = 3000 ms

- ii) Bake first 2 min (soft bake) @ 65 °C and next 5min @ 95 °C

- iii) Cool it environment for 10 min

- iv) Expose for 11s @ soft contact mode

- v) Post Exposure bake (PEB1) @ 65 °C for first 1 min and PEB2 @ 95 °C for next 3 min

- vi) Develop 10 min in Dev-600 with shaking

- vii) QDR bath for 2 min

- viii) Dry with  $N_2$  gas

- ix) Remove residual resist by ashing in  $O_2$  plasma, for 10s, 50 W

- x) Deposit Al using Plassys electron gun evaporator, 2µm thick, deposition rate 1 nm/s

- xi) Remove excess Al using 1165 remover for 90 minutes (Shake the wafer firmly, rinse the wafer by 1165 spray from a bottle to clear unexposed SU-8 2035 resist on the surface and replace the old 1165 remover by fresh one several times)

- xii) Clean in IPA for 5 min

- xiii) Dry in environment for 10 min

- xiv) Remove residual resist using dry etching SU8-STRP

## **Bibliography**

- [1] John Clarke, & Frank K. Wilhelm, "Superconducting quantum bits", NATURE, Vol. 453, No.19, June 2008.

- [2] S. Alexandrou, R. Sobolewski, T. Y. Hsiang, "Bend-induced even and odd modes in picosecond electrical transients propagated on a coplanar waveguide", Appl. Phys. Lett., Vol. 60, No. 15, April 1992.

- [3] George E. Ponchak, John Papapolymerou, Manos M. Tentzeris, "Excitation of Coupled Slotline Mode in Finite-Ground CPW with Unequal Ground-Plane Widths" IEEE Transactions on microwave theory and techniques, Vol. 53, No. 2, February 2005.

- [4] Jongjoo Lee, Heeseok Lee, Woopoung Kim, Jaehoon Lee, Joungho Kim, "Suppression of coupled-slotline mode on CPW using air-bridges measured by picoseconds photoconductive sampling", IEEE microwave and guided wave letters, Vol. 9, No. 7, July 1999.

- [5] Chung-Yi Lee, Yaozhong Liu, Tatsuo Itoh, "The effects of the coupled slotline mode and air-bridges on CPW and NLC waveguide discontinuities", IEEE Transactions on microwave theory and techniques, Vol. 43, No. 12, December1995.

- [6] Nihad I. Dib, Minoo Gupta, George E. Ponchak, Linda P.B. Katehi, "Characterization of asymmetric coplanar waveguide discontinuities", IEEE Transactions on microwave theory and techniques, Vol. 41, No. 9, September 1993.

- [7] "Superconducting coplanar delay lines", by Wi Wang, Doctoral thesis, University of Birmingham, February 2005.

- [8] C. P. Wen, "Coplanar waveguide: A surface strip transmission line suitable for nonreciprocal gyromagnetic device applications", IEEE Transaction on microwave theory and techniques", Vol. 17, No. 12, Dec. 1969.

- [9] M Gaudet, J C Camart, L Buchaillot, and S Arscott, "Variation of absorption coefficient and determination of critical dose of SU-8 at 365 nm", Appl. Phys. Lett. 88, 024107 (2006).

- [10] Datasheet SU-8 2000 Series, MicroChem.

- [11] Datasheet MicroChem Omnicoat<sup>TM</sup>.

- [12] Paul M. Dentinger, W. Miles Clift, Steven H. Goods, "Removal of SU-8 photoresist for thick film applications", Elsevier science, microelectronic engineering 61-62 (2002) 993-1000.

- [13] Rainee N. Simons, "Coplanar waveguide circuits, components, and systems"; ISBN 0-471-22475-8.

- [14] D. Vion, A. Aassime, A. Cottet, P. Joyez, H. Pothier, M.H. Devoret, C. Urbina, D. Esteve, "Towards quantum electrical circuits", Physica E 18 (2003).

- [15] Christian Schuster, Wolfgang Fichtner, "Parasitic modes on printed circuit bodes and their effects on EMC and signal integrity", IEEE Transaction on electromagnetic compatibility, Vol. 43, No. 4, November 2001.

- [16] H. Liaw and H. Merkelo, "Crossing the planes at high speed", IEEE Circuits & Devices Mag., Vol. 13, No. 6, November 1997.

- [17] <u>http://www.oxford-instruments.com/products/low-temperature/3he-</u> <u>refrigerators/Pages/3he-refrigerators.aspx.</u>

- [18] N.H. Balshaw, Practical cryogenics. Oxford instruments superconductivity, 2001.

- [19] D. Vion, P. F. Orfila, P. Joyez, D. Esteve, and M. H. Devoret, "Miniature electrical filters for single electron devices", J. Appl. Phys., Vol. 77, No. 6, March 1995.

- [20] K. Bladh, D. Gunnarsson, E. Hurfeld, S. Devi, C. Kristoffersson, B. Smalander, S. Pehrson, T. Claeson, and P. Delsing, "Comparison of cryogenic filters for use in single electronics experiments", Review of Scientific Instruments, Vol. 74, No. 3, March 2003.

- [21] Akio Fukushima, Akira Sato, Akio Iwasa, YasuhiroNakamura, Takeshi Komatsuzaki, and Yasuhiko Sakamoto, "Attenuation of microwave filters for single –electron tunneling experiments", IEEE Transactions on instrumentation and measurement, Vol. 46, No. 2, April 1997.