MASTER'S THESIS 2010

# IMPLEMENTATION OF A SOFTWARE TOOL FOR DEVELOPMENT, SPECIFICATION AND VERIFICATION OF LOGIC CONTROL PROGRAMS

Massoud Alahdini

Division of Control, Automation and Mechatronics Department of Signal and Systems Chalmers University of Technology Göteborg, Sweden 2010

# IMPLEMENTATION OF A SOFTWARE TOOL FOR DEVELOPMENT, SPECIFICATION AND VERIFICATION OF LOGIC CONTROL PROGRAMS

© Massoud Alahdini, 2010.

Master's Thesis 2010 Department of Signal and Systems Division *of* Control, Automation and Mechatronics Automation Research Group Chalmers University of Technology SE-41296 Göteborg, Sweden Telephone: +46-(0)31 772 1000 www.chalmer.se

Department of Signal and Systems

Göteborg, Sweden 2010

#### Abstract

This master thesis presents a practical work for implementing a software tool that is used for automating formal verification tasks for PLC-programs.

PLC-programs being used in manufacturing industries are on the demand of new requirements such as correct usage and behavior of the components. However, it is required to facilitate quick and correct modification of the programs as much as possible. One possible solution is to reuse the programs code.

The code that is structured into reusable components may speed up the development process. Furthermore it may cause the control program to have fewer bugs. For this aim, the previous research suggested to apply Reusable Automation Components (RACs). The RACs contain the implementation and formal specification.

To enhance reusability, it is necessary to identify and specify the requirements for the RACs. Additionally, the complete RAC including the specification must be translated into input to a tool for formal verification, to determine whether the implementation of the components fulfils the specification or not.

Performing all of these tasks manually is time consuming for developers, and even it is impossible to test all different cases in which the components can be used. Therefore, building a software tool to assist developers was a part of this project. The tool automatically generates inputs to Cadence SMV tool for formal verification, and finally the result of formal verification is presented as a feedback to developer.

To build the above mentioned tool, PLCOpenEditor that is an open source PLC programming environment has been extended to support RAC and formal verification using Cadence SMV.

The tool has successfully been used for non-trivial case study; an industrial example of translating the specification for a scan cycle based component is presented.

# Acknowledgements

This work would not have been completed without help and support of many individuals. I would like to thank everyone who has helped me along the way. Particularly: Dr. Knut Åkesson for providing me an opportunity to conduct my master's thesis with new research area and for his guidance and support over the course of my thesis, Oscar Ljungkrantz for his supervision and for helping me with various technical details, helpful comments on the text and his conversations during the development of the ideas in this thesis, special thanks goes to my brother Ali and my family without whose support none of this would have been possible.

# Contents

| CHAPTE | R 1 - Theory                                               | 1 |

|--------|------------------------------------------------------------|---|

| 1.1    | Introduction                                               | 1 |

| 1.2.0  | Overview                                                   | 3 |

| 1.2    | .1 Problem Description                                     | 3 |

| 1.2    | .2 Information Flow of Program                             | 3 |

| 1.3. B | ackground Theory                                           | 5 |

| 1.3    | .1 RAC/RAC Framework                                       | 5 |

| 1.3    | .2 Function Block                                          | 6 |

| 1.3    | .3 Scan Cycle                                              | 7 |

| 1.3    | .4 Formal Specification                                    | 7 |

| 1.3    | .5 Specification Text                                      | 8 |

| 1.3    | .6 Formal Verification                                     | 9 |

| 1.3    | .7 Symbolic Model Verification (SMV Model Checking)        | 9 |

| 1.4. C | Case Study                                                 | 9 |

| 1.4    | .1 Introduction                                            | 9 |

| 1.4    | .2 Previous Work at University1                            | 0 |

| 1.4    | .3 Aims and Objectives of utilizing the tool1              | 0 |

| 1.4    | .4 The Prepared Inputs of Example1                         | 0 |

| 1.4    | .5 The Output Result of Example1                           | 4 |

| 1.4    | .6 Benefits 1                                              | 8 |

| CHAPTE | R 2 – Specification Tool 1                                 | 9 |

| 2.1 Bu | uilding Graphical User Interface1                          | 9 |

| 2.1    | .1 Implementation and Integration of Specification Panel 2 | 0 |

| 2.1    | .2 Dividing Specification Panel                            | 1 |

| 2.1    | 3 Resizing Specification Window                            | 1 |

| 2.1    | .4 Switching Between Tabs 2                                | 2 |

| 2.2 Sa | aving and Loading Specification Data 2                     | 3 |

| 2.2    | .1 Saving Specification to a XML file                      | 3 |

| 2.2    | .2 Loading Information from XML-File to Editor 2           | 4 |

| 2.3 Creating "Tools" Menu                                                  | 25 |

|----------------------------------------------------------------------------|----|

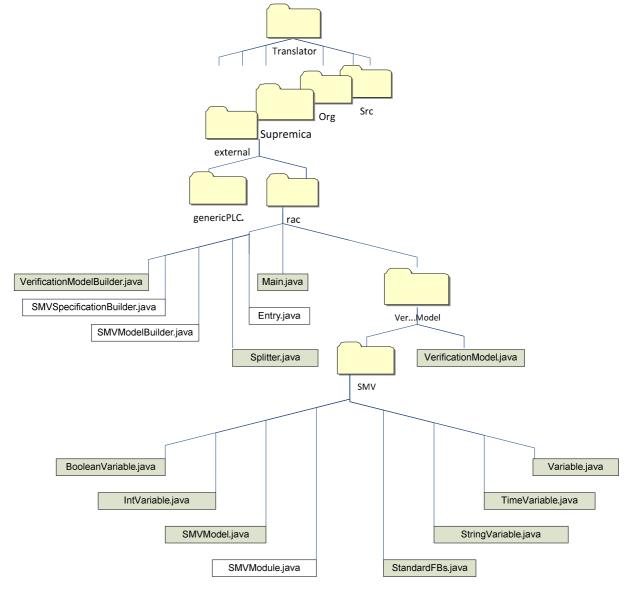

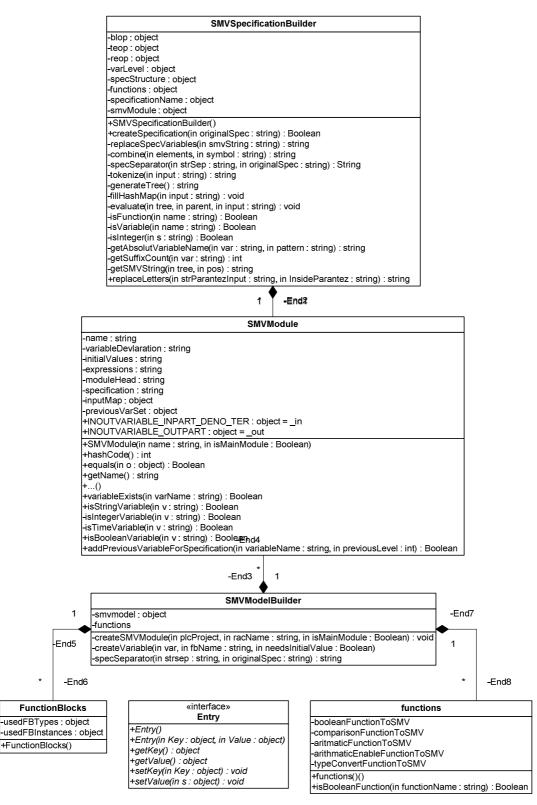

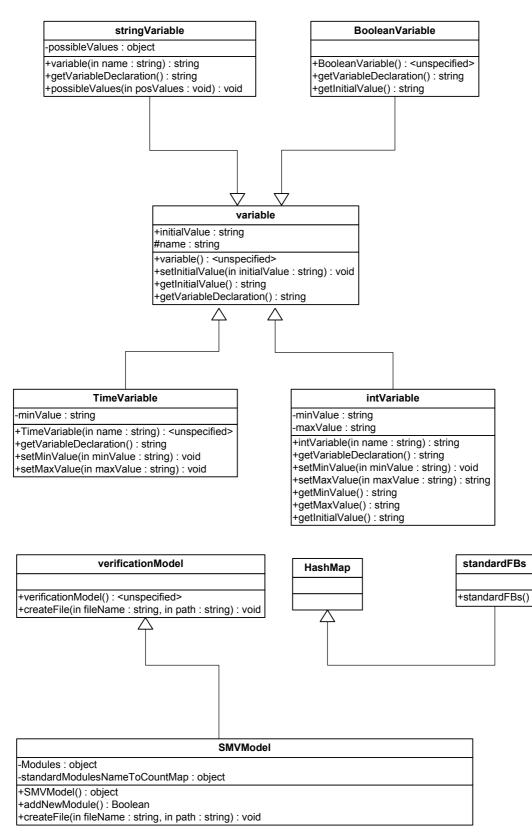

| CHAPTER 3- Java Implementation                                             | 26 |

| 3.1 Former Work at Department- (Translation of Control Logic into SMV)     | 26 |

| 3.2 Implement Translator (Translation of Specification Text into SMV Form) | 27 |

| 3.2.1 Loading Original Specification for Converting into SMV               | 27 |

| 3.2.2 Parsing Original Specification String and Identifying Type of Words  | 27 |

| 3.2.3 Build a Parse Tree Structure for Keeping Specification Texts.        | 27 |

| 3.2.4 Build "_previous" for Each Variable                                  | 28 |

| 3.2.5 Converting Tree to SMV Expression                                    | 31 |

| 3.2.6 Call Methods                                                         | 32 |

| 3.3 The Structure of Specification                                         | 32 |

| 3.3.1 Merging Strings Together                                             | 32 |

| CHAPTER 4 – Integrating all programs in one tool                           | 34 |

| 4.1 Calling Translator                                                     | 34 |

| 4.2 Starting SMV                                                           | 34 |

| 4.3 Applying Tool Feedback                                                 | 34 |

| 4.4 Automating Tool                                                        | 35 |

| CHAPTER 5 – Conclusion                                                     | 36 |

| 5.1 Conclusion                                                             | 36 |

| 5.2 Future Work                                                            | 37 |

| References                                                                 | 38 |

| Appendixes                                                                 | 39 |

| Appendix A: (Concepts, Terms and Definitions)                              | 39 |

| Appendix B: (TABLES)                                                       | 41 |

#### List of abbreviations

- FB: Function Block

- FBD: Function Block Diagram

- LD: Ladder Diagram.

- PLC: Programmable Logic Controller.

- RAC: Reusable Automation Components.

- SMV: Symbol Model Verification.

- XML: Extensible Markup Language

- CTL: Computation Tree Logic

- ST: Structured Text

- LTL: Linear Temporal Logic

- ST-LTL: Structured Text-LTL

# **CHAPTER 1 - Theory**

This chapter gives a brief introduction, an overview and background theory to my master thesis project. Furthermore, it describes a case study through an industrial example, which has been applied to the implemented tool in this thesis work.

# **1.1 Introduction**

This master thesis presents a practical work for implementing a software tool which is useful in computer software development, in particular for automating the formal verification task for PLC-programs. The software tool will be used for testing and formal verification, which are important issues for developing and building Reusable Automation Components (RACs).

PLC (Programmable Logic controller) is a typical embedded system to instrument and control systems. The PLC-programs that are generally referred to as logic control programs are used to control and coordinate machines and robots in automated manufacturing system.

Traditional PLC-programs have been used successfully in industry so far, but they would be very difficult to be modified, and to be extended to meet the new requirements. Moreover, PLC-programs tend to be time consuming to change when the manufacturing systems have to be changed (see [1]). Since, they often are tested to work first on the real equipments. Moreover, the same equipments cannot be used for production if error should be solved. Furthermore, it will be costly, since sometimes the traditional PLC-programs must first be tested to check if they work on real equipment or not. Hence, fixing the errors before production line would be expensive.

Developing PLC program with reusable components is a possible solution to enable fast and correct modification of the control logic. The code can be encapsulated and reused as Function Blocks (FBs). However, just encapsulating the control code into FBs is not enough [1]. The FBs should also be specified and be verified in order to work properly. For instance, it is required to determine how the efficient FBs (The FBs that are reused) shall be used and what the components guarantee.

The RACs mainly consist of two parts: implementation and specification. The implementation is designed in Ladder Diagram (LD) which is the most common language in Programmable Logic Controller (PLC) programs. The specification is written in Structured Text- Linear Temporal Logic (STL-LTL) which is a text based specification language for PLC program components, see [1]. Both the implementation and the specification are translated into inputs to a tool (SMV, Symbolic Model Verification, see [1, 2]) for performing formal verification, in order to determine whether the implementation fulfils the specification or not.

The SMV tool allows the developer to verify the behavior of the PLC program over all possible operating conditions, and if the verification is not successful a *counter example* will be shown to the user.

In order to enhance the development process, it is required to utilize an appropriate software tool that can automate the mentioned tasks (translation and formal verification).

The tool is applied by the developers who require implementing, specifying and verifying the reusable software components of PLC programming. So a RAC can be implemented, specified and verified in the developed software tool.

A former java based prototype at Chalmers University of Technology (CTH) has been implemented based on PLCOpenEditor. PLCOpenEditor is a free and open source IEC 61131-3 automation IDE. In this project, the PLCOpenEditor graphical user interface was extended for building the software tool. The editor can be used for writing the specification data and saving the specification data in XML file.

The java based prototype was extended for translating of the specification data into SMV format. This part of software tool creates the automatic generation of inputs, which they will be input to Cadence SMV tool. Some parts of the developed code launch the SMV tool properties for the formal verification; in consequence, the results of the verification process are stored to different output files. The output files can be observed by the user to see the faults, warnings and errors which may exist.

This report starts by introducing the main issues and a general overview of thesis work, and a background theory is described in the first Chapter, and then by presenting a case study shows an application perspective of such a software tool, below is a short guide to the rest of the report.

In Chapter 2 developing the python code for building specification editor is explained. In Chapter 3, developing the java program for building translator is described. In Chapter 4, integration of programs with SMV tool is described. Chapter 5 includes the conclusion, and the future work that is suggested for the improvement of tool.

# 1.2. Overview

This chapter will state the problem which is going to be solved, and describes the problem and requirements on developing the program.

#### **1.2.1 Problem Description**

A main part of this master thesis work was dedicated to develop and implement a software package. The aim has been to provide a tool for the developers in the automation group of signal and system department who want to implement, specify and verify the RAC components.

To make such software tool, the following main tasks has been carried out:

- Developing a graphical tool for specifying the FBs

- Developing the automatic generating of inputs to Cadence SMV tool for formal verification.

- Integrating the Editor, Translators, and SMV tool along with directing the information to the paths, running and starting the program from command lines.

#### **1.2.2 Information Flow of Program**

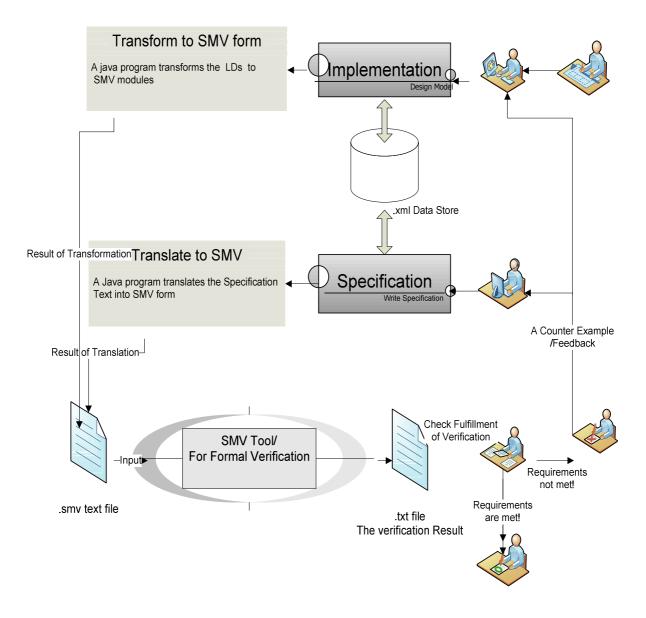

A general view of the whole process or the information flow of program has been depicted in Fig.1, a developer builds the FB diagrams and writes the corresponding specification text into the editor, the developer also is able to edit the previous information and FBs within this editor, and after completion can store the information to a file with ".xml" extension.

Whenever developer clicks on verify button in the editor, the translation will be started first, the translation of FBs or LDs into the SMV module along with Translation of ST-LTL specification into the SMV form. The results of these two translation processes are stored in a file with ".smv" extension. Other commands in the program launch the SMV and set this ".smv" file, this text file is as an input to the SMV tool. After that, SMV is started to perform the verification process. In consequence, the verification result is stored in a text file. A part of the program checks the fulfilments of the verification, mainly it checks if the verification is true or false, if it is false means that the requirements have not been met and it gives a message or show up the *counter example* to the developer.

Fig.1 - An overview of the complete processes in this project.

The later chapters describe the development of Translator program which has been used for building the software tool, the overview of the processes with software tool is shown in Fig.1.

#### **1.3. Background Theory**

This section attempts to give a background to the thesis work and argue why there is a need for such a tool for specification and verification of PLC components.

In industrial application, there are number of manufacturing systems for mass production which use machines and robots to automate tasks. Moreover, specific hardware and software components are required for the automation of machines and robots.

PLC-programs are kind of programs, which coordinates the machines and the robots in industry. However, the PLCs that have been used so far in industry shown to be successful, in order to meet the new requirements in developing of the PLC-programs.

As in previous years, the challenge of shorter life-cycles of many mass-produced products has been increased. This competition places new requirements on the PLC programs too. For instance, it is required that the PLC programs to be easily modifiable or extendable. The modification or extension is a difficult task, in which it needs to be tested on the real equipments, and it might be difficult to be changed. Moreover, the cost of the production will be increased if any error is detected. Since the error must be resolved in the previous equipment that caused an error, finding a new solution becomes expensive when the equipment cannot be reused. Moreover, changing the PLC-programs is time consuming task [1, 3, 4, and 5].

In some manufacturing companies, it is common to run the control logic against simulated manufacturing systems. Moreover it has been possible to test and troubleshoot the control logic in the earlier stages of development process. On the other hand, the control logic codes also can be encapsulated and be reused as Function Blocks (FBs). Since, reusing components is known as a beneficial design methodology in the development of embedded software products. One reason is due to the fact that it alleviates the cost of designing new solutions. Other reason, the development is faster if the designer can take the benefit of previous works and reduce the repetitive testing or verification task, hence, creating the PLC-programs from reusable components is also a way to expedite the correct modifications of the control logic [3, 4].

In order to create more effective software, a designer must be able to implement a new solution and adapt that to fit the requirements of the design of PLC components. In the following sections a RAC and its related issues are described, RACs are proposed for the components which are used for developing the control programs. It is followed by an overview of formal specifications and formal verification, the formal verification is to verify the reusability of software components.

#### 1.3.1 RAC/RAC Framework

A Reusable Automation Component (RAC) is a component and specification structure that is useful for building PLC-programs, the term "component" that often has been used in this project refers to RAC too[1]. A RAC prototype development tool has been implemented in Chalmers University

of Technology within Automation group in the Department of Signals and Systems. In Fig.2, a simple schema of a RAC is displayed.

|        | Reusable Automation Component                                                                                    |         |

|--------|------------------------------------------------------------------------------------------------------------------|---------|

|        | Interface                                                                                                        |         |

|        | Operation Specification                                                                                          |         |

| Inputs | Operation Preconditions prei,,prei     Operation Behaviours opBi,,oPBi     Exception Specification               | Outputs |

|        | <ul> <li>Exception Conditions exi,,exo</li> <li>Exception Behaviours exB<sub>1</sub>,,exB<sub>p</sub></li> </ul> |         |

|        | Invariants inv <sub>1</sub> ,,inv <sub>q</sub>                                                                   |         |

|        | Body                                                                                                             |         |

|        | Internal Variables                                                                                               |         |

|        | Implementation                                                                                                   |         |

|        |                                                                                                                  |         |

Fig.2. The main part of the Reusable Automation Component, RAC.[1]

The RAC (shown in Fig.2) consists of an *interface* and a *body*. The *interface* is the part which is visible to the end users. However, the *body* of the RAC is only accessible to the developers of the component [1].

The *interface* consists of three parts: Inputs, Outputs and Specification. The *body* includes the implementation part of the components function along with the declaration of any internal variables.

#### **1.3.2 Function Block**

The Function Block (FB) is the basic functional software unit that is the smallest element of a distributed control system, which has its own data structure and a set of algorithms. These abilities make it possible to access and modify the data. The models and the concepts introduced by the PLC standards (such as: IEC 61131-3, see [7] and Appendix A) provide the possibility to define such a distributed application to be hardware independent, the applications can be implemented by modular components, and the components can be reused too [12]. The most PLC-programs are implemented according to the IEC 61131-3 standard [7]. Hence in this project, only the IEC 61131-3 standard is applied.

The RAC can be implemented as a FB; the FB concept is a kind of typical offered solution by automation companies which was previously introduced in the PLC language IEC 61131-3 standard. FBs can be considered as small reusable pieces of software that prepare a software solution in advance to a small problem. The RACs can be developed as IEC 61131-3 function blocks

which is extended with specification [2]. However, the FB might not be formally specified before, it should be specified formally, even formal verification requires a formal specification. Hence, the RAC is complemented with a formal specification [1, 3]. Moreover, the end-user will be able to integrate the pre-made software block without further knowledge about the complex contents such as internal components and functions etc. One advantage of using the IEC 61131-3 in contrast to traditional PLC programming is the easy reusability of its software and easy integration into the user program [8].

#### 1.3.3 Scan Cycle

There is a scheduling function that is provided to ensure the correct execution sequence and priority. Moreover, a PLC does not handle many tasks in the same time, but there is a parallel computing that is simulated by an operation cycle. This operation cycle which will be run several times per second is referred as the scan cycle of a PLC [12]. The scan cycle is composed of four basic stages:

- 1) Self-checking for finding the hardware and software faults

- 2) Input scan is the stage when all inputs are copied into the memory.

- 3) Logic scan is the stage which is using only the memory copy of the inputs while the program is executed.

- 4) Output scan is the stages which are using the temporary values in memory while all the outputs are updated. The output value can be changed only in the temporary memory.

Each FB may have a set of Input variables, outputs variables and enclosed algorithms in its structure. This structure will be reviewed by an example that will be described in the later parts of the case study.

#### **1.3.4 Formal Specification**

In this part, an overview and the description of the formal specification in the current project is presented.

By convenient, "Formal specification in computer systems is defined as a mathematical description of software or hardware". The specification and implementation (or designs) are two mixed processes. The specification describes what the system should do and how the system should perform an action.

Informal descriptions of a RAC are not suitable for formal verification, since they might be ambiguous and could be misinterpreted [3]. Nevertheless, formal specification is necessary and suitable for formal verification. Formal specification handles with more effort in the early stages of software development. With this way, the user will be able to specify the requirements of the implementation.

Formal specification along with formal verification, reduce the requirements, errors and faults. In consequence, any inconsistency or any unstable situation can be discovered and resolved in the earliest phases of implementation. It is also expected to reduce any ambiguity or errors in the requirements, which will result in saving the costs (time, expenses) of implementation and validation in the developing of the system.

In this project, the formal specification must be expressed in a temporal logic notation with precisely defined the grammar and syntax and semantics. Moreover, temporal logics are used to describe Boolean logic and its relation over time. Two most common temporal logics are *Computation Tree Logic* (CTL) and *Linear Temporal Logic* (LTL). They differ in how they handle branching in the underlying computation tree. In CTL temporal operators it is possible to quantify over the paths departing from a given state. In LTL operators are intended to describe properties of all possible computation paths. [2, 15]

#### **1.3.5 Specification Text**

There is no former support of formal specification in developing and reusing FB's, the ongoing research in department[1,2] has proposed solution to use a text based specification language instead of other existing language for PLC programming.

A text based specification language, is similar to the structured text (ST). Furthermore, it contains some extensions. The aim of adding these extensions is to handle temporal/ time relations, since it is mixed with simplified and clarified temporal logic[1,2], such that the specification apply the temporal operators and functions.

The suggested specification language in [2] for PLC program components is based on the IEC 61131-3 language and LTL (Linear Temporal Logic). For instance, if "a rising edge of a *Boolean* input *I* will always guarantee that at least one of the two outputs O1 and O2 will eventually be *true*" be an example that should be specified (when the input transits from *false* to *true*), this in LTL can be expressed as:

$$G\left(\sim I\bigwedge (XI)\Rightarrow FX\left(01\bigvee 02\right)\right)$$

This property can be specified using a text-based variant such as what written bellow.

Spec1: = ALWAYS (NOT I\_previous & I -> EVETUALLY (O1 OR O2)); or

Spec1: = ALWAYS (I\_risingEdge -> EVENTUALLY (O1 or O2));

The IEC 61131-3 standard contains Boolean and comparison functions such as AND (), NOT (), OR(), GT() and EQ()[2]. These functions might be applied in both graphical languages (LD and FBD) and text-based languages (Structured Text and Instruction List) of IEC 61131-3. Moreover, the logic functions to be applied in text based languages have corresponding *operators* [2]. For example, AND in IEC 61131-3 is both an operator and a function.

In structured Text the Boolean "and" relation between two variables p and q can be written such as:  $p \ AND \ q, p \ \& q, or \ AND \ (p,q)$ . AND (p,q) is the function type of the other two forms. However, there is a possibility for writing specifications graphically in Ladder Diagram (LD) or Function Block Diagrams (FBD) as well. In this project, the specifications are written in the text based language.

#### **1.3.6 Formal Verification**

The implementation of PLC program has been designed in LD. The developer can write the specification for this implementation. Then after writing the formal specification, it is possible to apply formal verification techniques in order to demonstrate whether a system design is correct or not. A developer is interested in testing if the implementation is correct with respect to the given specification. Otherwise the result might be shown to the user and check what has been wrong within implementation process.

#### 1.3.7 Symbolic Model Verification (SMV Model Checking)

By definition, model checking (on a given model of system) refers to automatically testing whether the model meets a given specification [9]. SMV (Symbolic Model Verifier) is a tool for checking the finite-state systems to meet the requirements (or specifications), the specifications has given in LTL. The model is required to be translated into the input language of a model checking tool. The tool that has been used in this project is "Cadence SMV" tool [2, 11, and 14].

In the process of model checking, it checks if whether a given model satisfies the specification. The most valuable feature of SMV tool is its *counter example* feedback. If a given model does not fulfil the requirements of its specifications, then SMV presents a trace identifying why the specification is false.

#### 1.4. Case Study

This section provides a case study which briefly studies the usage of a software tool that has been implemented in this project.

#### **1.4.1 Introduction**

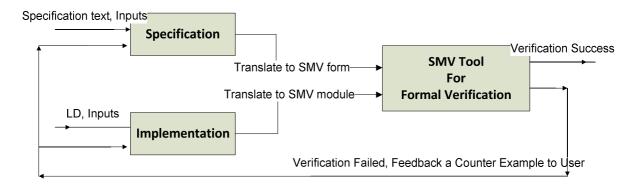

The software tool has been applied for the purpose of the implementation, specification and verification of Logic Control Programs. In this section, the case study represents an example showing how this integrated program can be an appropriate tool for the developers who require implementing, specifying and verifying the re-usable software components of PLC programming. Fig.3 depicts a whole process of implementation, specification and translation of both into a SMV tool for the purpose of verification.

Fig.3. depicts the whole schema of Implementation, specification, translation and verification stages.

As it is shown in Fig.3, the implementation (i.e. Implemented in a LD) is transformed into a set of SMV modules; moreover the transformation retains the structure of block diagram model which has been designed. The specification text also will be translated into the SMV language form. The transformation and translation will be an input to SMV tool for the formal verification process.

In this case study, the design of PLC Ladder Diagram, the specification text and SMV approach to PLC program verification is illustrated with an example. The design and implementation of this software tool will be described in details in later chapters.

#### **1.4.2 Previous Work at University**

A RAC prototype development tool has been developed [3]. The Implementation part of designing a model of PLC software components has been developed previously by Oscar Ljungkrantz in automation group of the department of Signals and Systems in CTH, using Java programming language to translate the control logic components into SMV. For the specification part, it was suggested to be translated into the text format of Cadence SMV. PLC Open has defined an open interface for PLC-programs, with an XML schema. Furthermore, The RACs should be saved to a XML file according to that XML format [3].

#### 1.4.3 Aims and Objectives of utilizing the tool

- To view the implementation of PLC software component, and to transform it into SMV modules.

- To write a specification for the component, and translate it into SMV format

- To verify the result of SMV files, and convey a feedback to the developer

#### 1.4.4 The Prepared Inputs of Example

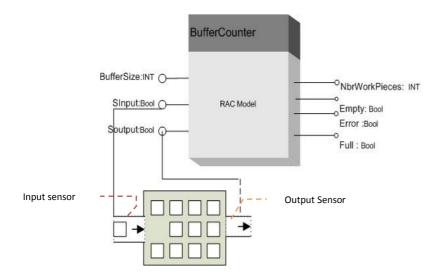

This example, "*BufferCounter*" is presented to show how a RAC can be implemented, specified and verified in the developed software tool. The "BufferCounter" is a RAC for collecting some information from a buffer, the information that can be used while controlling the buffer. The inputs and their types in this case study are depicted in Fig.4.

Fig. 4- The variable declaration and code icon for a Buffer Counter

The RAC model has been proposed and provided by my supervisors (Oscar Ljungkrantz, Knut Åkesson) at Chalmers University of Technology. This is an example of a FB that counts the number of work pieces in a buffer (NbrWorkpieces). "Buffer Size" and "NbrWorkpieces" are defined as integer, the other Inputs and Outputs are Boolean.

By conducting an inquiry on input and output sensors of the buffer, it will be possible to count the NbrWorkpieces. Passing the respective sensor into the high or passing it out of the buffer is considered for changing of the NbrWorkpieces. If the NbrWorkpieces is over the capacity of the buffer size, it will give an error. Moreover, such information will be useful for controlling the buffer on next steps.

The input file is a RAC example which should be opened in the editor. The user will be able to build the LDs, FBs, and all the corresponding elements along with writing the specification, based on the example stated in this study. The implementation will be transformed into the SMV module. The files related to this case study along with software tool can be viewed in the attached CD to this report, thus it is possible to build the RAC of this case study.

#### 1.4.4.1 Implementation

The example demonstrates the development of a RAC BufferCounter, which has been implemented as a FB in LD. LD is the most common language for developing PLC-programs (for instance in car industries).

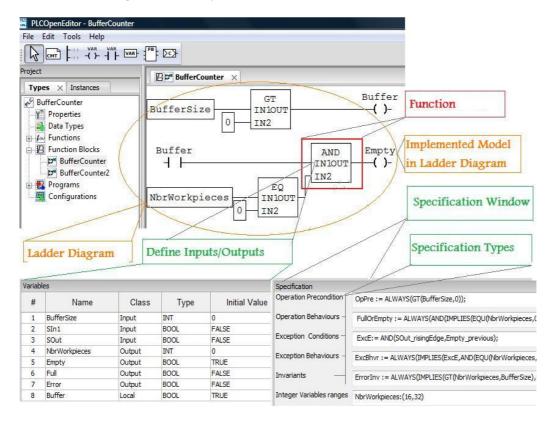

In the Fig.5, there are different panels in a PLCOpenEditor. Some of these panels are *implementation* panel, *specification* panel and *variables* panel which have been highlighted in

Fig.5. The developer can implement the FB example within the implementation panel (window) in LD. For each FB might have an implementation window.

Fig. 5 - The input/output variables, implementation, and specification window are shown in this figure.

The developer can choose a XML file from the menu "File/Open" on menu bar of the editor. It is also possible to choose the FBs on the left side of the editor (in Project panel). The developer can design and implement the LD and the elements which are the basis for reusing software. The implementation later will be translated into inputs to the SMV tool for performing the formal verification task.

#### 1.4.4.2 Specification

The specification is written in specification windows within the separated text fields. The inputs and outputs variables should be defined on the *variables* panel in advance whenever the user implements the FBs.

As mentioned previously in the report, the specification "*BufferCounter*" example can be specified in the specification language (ST-LTL), which is based on LTL and ST. Moreover, it is assumed that the input sequences strings of specification be expressed in "prefix" form, which is one way of writing expressions, these strings should not be in the form of "postfix" or "infix", because the program does not support the possibility of translating "postfix" and "infix". This specification text includes all five specification types which are stated in Table.

| Spec                       | ification type             | Specification texts( specified in ST-LTL)                                                                                        |

|----------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                            | Operation<br>preconditions | OpPre := ALWAYS(GT(BufferSize,0));                                                                                               |

| Specification              | S                          | CountUp :=<br>ALWAYS(IMPLIES(AND(SIn1_risingEdge,NOT(SOut_risingEdge)),(EQ(NbrWorkpieces,ADD(NbrWorkpiece<br>s_previous,1)))));  |

|                            | behaviou                   | CountDown :=<br>ALWAYS(IMPLIES(AND(SOut_risingEdge,NOT(SIn1_risingEdge)),(EQ(NbrWorkpieces,SUB(NbrWorkpiece<br>s_previous,1)))); |

| Operation                  | Operation behaviours       | UpNDown :=<br>ALWAYS(IMPLIES(AND(SIn1_risingEdge,SOut_risingEdge),(EQ(NbrWorkpieces,NbrWorkpieces_previous<br>))));              |

|                            | 0                          | FullOrEmpty :=<br>ALWAYS(AND(IMPLIES(EQU(NbrWorkpieces,0),Empty),IMPLIES(GT(NbrWorkpieces,BufferSize),Full)));                   |

| on<br>ation                | Exception<br>conditions    | ExcE:= AND(SOut_risingEdge,Empty_previous);                                                                                      |

| Exception<br>Specification | Exception<br>behaviours    | ExcBhvr := ALWAYS(IMPLIES(ExcE,AND(EQ(NbrWorkpieces,0),Empty)));                                                                 |

| Invariants                 |                            | ErrorInv := ALWAYS(IMPLIES(GT(NbrWorkpieces,BufferSize),Error));                                                                 |

Table1. Specification contents that are written within separated fields

Besides the writing of these eight specifications that were described in Table1, the developer can specify the *minimum* and *maximum* values of the integer variables within the editor, which is required later for verification stage, these amounts should be written in the last text field of specification window(within the editor). For instance, "BufferSize:(40, 50)" shows the initial value of size that is dedicated to Buffer, these values are used in formal verification. In this example, the *minimum* value of *BufferSize* is considered to be "40" and the maximum is given by "50". "NbrWorkpieces:(-1, 70)" shows the initial value for the number of work pieces, so the minimum given value of the number of workpieces(i.e. NbrWorkpieces) is "-1" and the maximum given value of this value is "70" in the first attempt of running the program.

After implementing FBs, designing in LDs language and writing the specification in the form of ST language, the user can save both implementation and specification in an XML file by clicking on "File/Save".

#### 1.4.5 The Output Result of Example

All the specification and information should be edited in the PLCOpenEditor and be saved into the BufferCounter.xml file. There is a program which has been developed in Java, and it acts as a translator which automatically does the translation procedure. So the next step is the translation from ST language to SMV code. The whole process of translation will be triggered when user Click on *"verify"* on the sub-menu under the *Tools* menu of main editor in the software tool. (See in Fig.6).

| PLCOpenEditor - BufferCounter                                                                                                                                                                                                                                                     | To la                                                                  | unch                                                                       |                                                                                                   |                                                                                              |                        |               |         |                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| Project SMV                                                                                                                                                                                                                                                                       |                                                                        | ication                                                                    | Implemen<br>panel                                                                                 | ntation                                                                                      | )                      |               |         | Library                                                                                                                           |

| Types       X       Instances         Properties       Data Types         Data Types       Functions         Function Blocks       BufferCounter         BufferCounter       BufferCounter2         Programs       Configurations         Specification panel       Specification | But<br>But<br>Specifi<br>Opera<br>Opera<br>Except<br>Except<br>Invaria | tion Precondition<br>tion Behaviours<br>tion Conditions<br>tion Behaviours | GT<br>IN10U<br>IN2<br>OpPre := ALWAYS<br>(NbrWorkpieces,0)<br>ExcE:= AND(SOut<br>ExcBhvr := ALWA) | (GT(BufferSize,I<br>,Empty),IMPLIE<br>:_risingEdge,Emp<br>/S(IMPLIES(Exct<br>/S(IMPLIES(GT() | S(AND(NbrWorkpieces,Bu | s,0),Empty))) |         | Block Types<br>Standard f<br>Type conv<br>Numerical<br>Arithmetic<br>Bit-shift<br>Bitvise<br>Comparise<br>Character<br>User-defin |

|                                                                                                                                                                                                                                                                                   | Variab                                                                 | es                                                                         |                                                                                                   |                                                                                              |                        |               | -       |                                                                                                                                   |

|                                                                                                                                                                                                                                                                                   | #                                                                      | Name                                                                       | Class                                                                                             | Туре                                                                                         | Initial Value          | Retain        | Constar | nt                                                                                                                                |

| Variable                                                                                                                                                                                                                                                                          | 1                                                                      | BufferSize                                                                 | Input                                                                                             | INT                                                                                          | 0                      | No            | No      |                                                                                                                                   |

| panel                                                                                                                                                                                                                                                                             | 2                                                                      | SIn1<br>SOut                                                               | Input                                                                                             | BOOL                                                                                         | FALSE                  | No            | No      |                                                                                                                                   |

|                                                                                                                                                                                                                                                                                   | 4                                                                      | NbrWorkpieces                                                              | Output                                                                                            | INT                                                                                          | 0                      | No            | No      |                                                                                                                                   |

Fig. 6- Launching the verification in the editor

#### 1.4.5.1 Translate to SMV Code

In translation process the implementation will be translated into SMV modules. The specification will be translated to SMV language. Thus the translator first parses the specification text, and then converts it to an SMV code. In consequence of the translation process, the result of translation as input is fed to SMV tool for formal verification, the code will be verified in the SMV tool and the output of the verification will be saved within different files. For instance, the SMV trace will be placed in BufferCounter.smv.

The "BufferCounter.smv" file contains one record for each specification that has been checked. If it is true, states that specifying the truth value of the specification. And if it is false, it presents a

*counter example* showing why the specification is false. The result of this checking is also stored in the file "BufferCounter.out", another output file is "BufferCounter.warn", which contains the errors and warning that has been made by verification process (i.e. running "verify all" within tool bar menu of SMV). In the following sections the verification on the BufferCounter example will be described.

#### 1.4.5.2 Verification

This section takes a closer look at the process of formal verification of specification text that was described in the previous sections, by going through an example.

As it has been explained in previous sections, the result of translation to SMV format and the result of translating the implementation will be the inputs into SMV tool for performing formal verification, to determine whether the implementation fulfills the specification or not. If the Implementation does not fulfill the specification, then the result might be shown to user, moreover the user can check what has been wrong within Implementation process. After completing the verification process, a verification message will be pop up to developer as shown in the Fig.7.

Fig. 7- Informing message when requirements

If "yes" option is chosen, a graphical user interface for "SMV" will be shown. Then the SMV result can be viewed by the developer. However, the SMV graphical interface itself provides the ability of source browsing, *counter example* browsing, abstraction editing, etc [2].

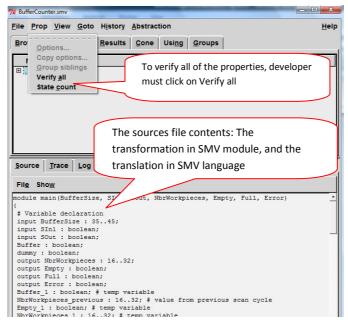

The SMV graphical interface is formed from a main menu bar, and a collection of "panes", each one can be visible by clicking on its tab. These pans are depicted in Fig.8. The first pane that is viewed is called "Source pane", showing the currently loaded source-file (BufferCounter.smv)

| 7 BufferCounter.smv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| File Prop View Goto History Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>H</u> elp |

| Browser Properties Results Cone Using Croups                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| Name Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| E : (top.level):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Source Irace Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Fil <u>e</u> Sho <u>w</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| <pre>module main(BufferSize, SIn1, SOut, NbrWorkpieces, Empty, Full, Error<br/>{<br/># Variable declaration<br/>input BufferSize : 3545;<br/>input SIn1 : boolean;<br/>input SUut : boolean;<br/>Buffer : boolean;<br/>dummy : boolean;<br/>dummy : boolean;<br/>output Full : boolean;<br/>output Full : boolean;<br/>output Furor : boolean;<br/>Buffer_1 : boolean; # temp variable<br/>NbrWorkpieces_previous : 1632; # value from previous scan cycle<br/>Empty 1 : boolean; # temp variable<br/></pre> | ;)           |

Fig. 8- The SMV graphical interface shows source file.

All of the properties in the file can be verified by selecting the "Verify all" option from the "Prop" menu in the program (shown in Fig.9). One particular property (i.e. property name) can be verified by choosing "Verify property" option from the "Prop" menu. This action is supposed to run the SMV model checker in background, and to give a notification to the user whenever the verification is completed.

Fig. 9 – The SMV graphical interface for verifying the Source file

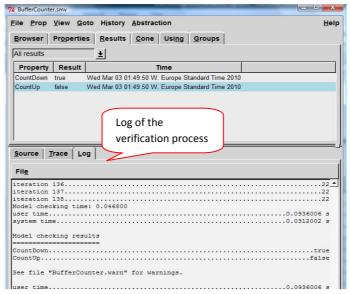

The results of the most recent verification run will be displayed in "Results" pane. The properties that have been checked are listed in this pane. The results, either True or False, will also be shown. It has been highlighted in Fig.10.

| ile <u>P</u> rop        | View Go                                                                    | to H <u>i</u> s                       | tory <u>A</u> bst                | raction                               |                                  |                                       |                                       |                                       | He                    |

|-------------------------|----------------------------------------------------------------------------|---------------------------------------|----------------------------------|---------------------------------------|----------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------|

| Browser                 | Pr <u>o</u> pertie                                                         | s <u>R</u> es                         | ults <u>C</u> o                  | ne Usi <u>n</u>                       | g <u>G</u> roup                  | ps                                    |                                       |                                       |                       |

| All results             |                                                                            | ±                                     | _                                |                                       |                                  |                                       |                                       |                                       |                       |

| Property                | Result                                                                     |                                       |                                  | Time                                  |                                  |                                       |                                       |                                       |                       |

| CountDown               | true                                                                       | Wed Ma                                | r 03 01:49:5                     | 0 W. Europ                            | e Standard 1                     | Time 2010                             |                                       |                                       |                       |

| CountUp                 | false                                                                      | Wed Ma                                | r 03 01:49:50                    | 0 W. Europ                            | e Standard 1                     | Time 2010                             |                                       |                                       |                       |

|                         | [race Lo                                                                   |                                       | Count                            | er exam                               | nple resu                        | ults in Tr                            | ace pan                               | e                                     |                       |

|                         | - 1 -                                                                      |                                       | $\geq$                           |                                       |                                  |                                       |                                       |                                       |                       |

|                         | R <u>u</u> n Vie                                                           | w -                                   | 2                                | 3                                     | 4                                | 5                                     | 6                                     | 7                                     |                       |

|                         | R <u>u</u> n Vie<br>BufferSize                                             | 1<br>35                               | $\geq$                           |                                       |                                  |                                       |                                       |                                       |                       |

|                         | R <u>u</u> n Vie                                                           | 1<br>35                               | 2                                | 3                                     | 4                                | 5                                     | 6                                     | 7                                     |                       |

|                         | R <u>u</u> n Vie<br>BufferSize                                             | 1<br>35<br>1                          | 2<br>35                          | 3<br>35                               | 4 35                             | 5<br>35                               | 6<br>35                               | 7 35                                  |                       |

|                         | R <u>u</u> n Vie<br>BufferSize<br>Buffer_1                                 | 1<br>35<br>1<br>1                     | 2<br>35<br>1                     | 3<br>35<br>1                          | 4<br>35<br>1                     | 5<br>35<br>1                          | 6<br>35<br>1                          | 7<br>35<br>1                          | 5<br>5<br>1<br>1<br>( |

| Fil <u>e</u> Edit       | Run Vie<br>BufferSize<br>Buffer_1<br>Empty                                 | 1<br>35<br>1<br>1<br>0                | 2<br>35<br>1<br>1                | 3<br>35<br>1<br>1                     | 4<br>35<br>1<br>1                | 5<br>35<br>1<br>1                     | 6<br>35<br>1<br>1                     | 7<br>35<br>1<br>1                     | 1<br>1<br>1<br>1      |

| Fil <u>e Ed</u> it      | Run Vie<br>BufferSize<br>Buffer_1<br>Empty<br>Empty_1                      | 1<br>35<br>1<br>1<br>0<br>1           | 2<br>35<br>1<br>1<br>0           | 3<br>35<br>1<br>1<br>0                | 4<br>35<br>1<br>1<br>0           | 5<br>35<br>1<br>1<br>0                | 6<br>35<br>1<br>1<br>0                | 7<br>35<br>1<br>1<br>0                |                       |

| Fil <u>e Ed</u> it      | Run Vie<br>BufferSize<br>Buffer_1<br>Empty<br>Empty_1<br>pty_previous      | 1<br>35<br>1<br>1<br>0<br>1<br>0      | 2<br>35<br>1<br>1<br>0<br>1      | 3<br>35<br>1<br>1<br>0<br>1           | 4<br>35<br>1<br>1<br>0<br>1      | 5<br>35<br>1<br>1<br>0<br>1           | 6<br>35<br>1<br>1<br>0<br>1           | 7<br>35<br>1<br>1<br>0<br>1           |                       |

| Fil <u>e</u> Edit<br>Em | Run Vie<br>BufferSize<br>Buffer_1<br>Empty_1<br>pty_previous<br>Sensor CLK | 1<br>35<br>1<br>1<br>0<br>1<br>0<br>0 | 2<br>35<br>1<br>1<br>0<br>1<br>0 | 3<br>35<br>1<br>1<br>0<br>1<br>1<br>1 | 4<br>35<br>1<br>1<br>0<br>1<br>0 | 5<br>35<br>1<br>1<br>0<br>1<br>1<br>1 | 6<br>35<br>1<br>1<br>0<br>1<br>0<br>0 | 7<br>35<br>1<br>1<br>0<br>1<br>1<br>1 |                       |

Fig. 10 – The SMV graphical interface for viewing the result in Trace pane

#### **1.4.5.3 TRACE PANE**

The *counter examples* and simulation traces can be displayed in the trace pane view. It is similar to a spreadsheet (i.e. shown in Fig.10), where the rows represent the variables and the columns represent time [2].

#### 1.4.5.4 Viewing Log File

A log of the verification process will appear in another pane which is called log pane. This file is created as SMV is progressing to complete the process of model checking.

Fig. 11 – The SMV graphical interface for observing the log file

The verification process is launched by internal commands which save the results in different files. For instance *"log file"* is one of those files that a user can observe the result of verification. There are some other output files that will be created such as *"BufferCounter.warn"* showing the warnings, and "BufferCounter.out" that shows the errors if any exists.

However, if verification failed after launching the verification process, the user is informed before showing the contents of the output files. If any of specifications is false, the SMV model checker tool will produce a *counter example*, the *counter example* contents can prove that the specification is false [11].

#### **1.4.6 Benefits**

This case study presented an industrial example that contains a formal verification of a PLC system, which shows how the specification can be automatically translated into Cadence SMV input language, and how it is formally verified. It shows how the formal verification process can be useful in real applications. The Software tool automatically verifies that the implementation fulfils the specification. Otherwise, if the implementation does not fulfil the specification, it produces a *counter example* to state the reason that the specification is not fulfilled. In consequence, the RAC can be corrected and verified again until the complete specification is fulfilled [3]. In next chapters will describe how the program has been implemented.

# **CHAPTER 2 – Specification Tool**

In this chapter, the implementation of the specification editor is described. This editor window is integrated to PLCOpenEditor that was implemented by LOLITech group in Beremiz PLCOpen project. The PLCOpen Editor is the one of Beremiz's sub-projects; Beremiz is an open source for automation IDE that is based on IEC 61131-3, which is a multi-platform IDE for automation [6].

# 2.1 Building Graphical User Interface

A Graphical User Interface (GUI) is required to be used for creating the example components in it. In this project, we decided to develop the same PLCOpenEditor GUI that was implemented in python by LOLITech group; this PLCOpenEditor is shown in this Fig.11.

Fig.11- PLCOpenEditor before integrating specification window

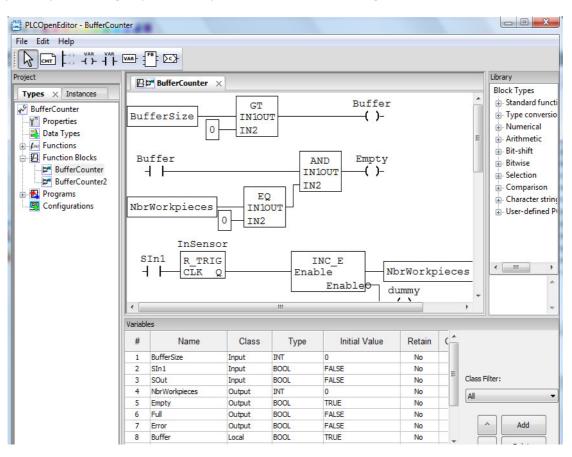

The PLCOpenEditor before integrating the specification window is similar to what is shown in Fig.11, in this editor the developer can make Functions and Function Blocks, and set the input and output variables, etc. After integrating another panel for specification, it looks like Fig.12 that is shown in next page.

| PLCOpenEditor - BufferCount | ter    |                                                            |                   |                 | www.iau.wo                 | 10.00      |         |                            |  |  |

|-----------------------------|--------|------------------------------------------------------------|-------------------|-----------------|----------------------------|------------|---------|----------------------------|--|--|

| File Edit Tools Help        | -      |                                                            |                   |                 |                            |            |         |                            |  |  |

|                             | VAR-   | 202                                                        |                   |                 |                            |            |         |                            |  |  |

| Project                     |        |                                                            |                   |                 |                            |            |         | Library                    |  |  |

| Turner of Turners           | - 8    | BufferCount                                                | er ×              |                 |                            |            | [       | Block Types                |  |  |

| Types × Instances           | _      |                                                            | GT                |                 | Buffer                     |            | -       | - Standard function blocks |  |  |

| BufferCounter     ■         | Bu     | fferSize                                                   | IN10              |                 |                            |            |         |                            |  |  |

| Properties                  |        | 11010120                                                   | 0 IN2             |                 |                            |            |         |                            |  |  |

| Data Types                  |        |                                                            | U INZ             | -               |                            |            |         | Arithmetic     Bit-shift   |  |  |

| + fin Functions             |        | 222                                                        |                   |                 |                            |            |         |                            |  |  |

| Function Blocks             | B      | uffer                                                      |                   | 2               | AND Empty                  |            | -       | Bitwise                    |  |  |

| BufferCounter               | 4      |                                                            |                   |                 | torm ()                    |            | •       | Selection                  |  |  |

| BufferCounter2     Programs | Canad  | fication                                                   |                   |                 |                            |            |         | Comparison                 |  |  |

| Configurations              |        |                                                            |                   | (CT/D. HarCing  | 0)).                       |            |         | - Character string         |  |  |

| Conigurations               |        | Operation Preconditions OpPre := ALWAYS(GT(BufferSize,0)); |                   |                 |                            |            |         | User-defined POUs          |  |  |

|                             | Opera  | ation Behaviours                                           | (NbrWorkpieces,0) | ); ‡            |                            |            |         |                            |  |  |

|                             | Excep  | tion Conditions                                            | ExcE: = AND(SOut  | t risinaEdae.Em | pty previous):             |            | ÷       |                            |  |  |

|                             | Euro   | tion Behaviours                                            |                   |                 |                            |            |         |                            |  |  |

|                             | Схсер  | ouori beriaviours                                          | ExcBhvr := ALWA   | YS(IMPLIES(Excl | E, AND (EQU (Nbr Workpiece | ; 🗘 -      |         |                            |  |  |

|                             | Invari | iants                                                      | ErrorInv := ALWA  | YS(IMPLIES(GT(  | NbrWorkpieces,BufferSize)  | ),Error)); | \$      |                            |  |  |

|                             | Variab | ole Ranges                                                 | NbrWorkpieces:(1) | 5,32)           |                            |            | :       | *                          |  |  |

|                             | Variab | oles                                                       |                   |                 |                            |            |         |                            |  |  |

|                             | #      | Name                                                       | Class             | Туре            | Initial Value              | Retain     | Constan | it 🕺                       |  |  |

|                             | 1      | BufferSize                                                 | Input             | INT             | 0                          | No         | No      |                            |  |  |

|                             | 2      | SIn1                                                       | Input             | BOOL            | FALSE                      | No         | No      |                            |  |  |

|                             | 3      | SOut                                                       | Input             | BOOL            | FALSE                      | No         | No      | Class Filter:              |  |  |

|                             | 4      | NbrWorkpieces                                              | Output            | INT             | 0                          | No         | No      |                            |  |  |

|                             | 5      | Empty                                                      | Output            | BOOL            | TRUE                       | No         | No      |                            |  |  |

|                             | 6      | Full                                                       | Output            | BOOL            | FALSE                      | No         | No      |                            |  |  |

|                             | 7      | Error                                                      | Output            | BOOL            | FALSE                      | No         | No      | ^ Add                      |  |  |

|                             | 8      | Buffer                                                     | Local             | BOOL            | TRUE                       | No         | No      |                            |  |  |

|                             | 9      | InSensor                                                   | Local             | R_TRIG          | EN OF                      | No         | No      | v Delete                   |  |  |

|                             | 10     | dummy                                                      | Local             | BOOL            | FALSE                      | No         | No      |                            |  |  |

Fig.12- PLCOpenEditor after integrating specification panel

The aim of the first part of this chapter is to show how the specification editor has been developed within framework of this project, the specification editor (shown in Fig.12) is one editor which has been integrated to the previous editor (shown in Fig.11) that basically was made by Beremiz group. In the following sections, this development has been described. It is not possible to describe all details of programming and codes in this report; however the attempt was to give a main view from what has been done.

#### 2.1.1 Implementation and Integration of Specification Panel

To Implement and integrate the specification window into the PLCOpenEditor, the following lines has been written in the PLCOpenEditor to build the specification panel.

| self.panel = SpecificationPanelIndexer(self, self, self.Controler)                                            |

|---------------------------------------------------------------------------------------------------------------|

| self.AUIManager.AddPane(self.panel,                                                                           |

| wx.aui.AuiPaneInfo().Caption("Specification").Center().Layer(0).BestSize(wx.Size(50,200)).CloseButton(False)) |

|                                                                                                               |

| Table 2. Part of PLCOpenEditor code which implements the specification panel                                  |

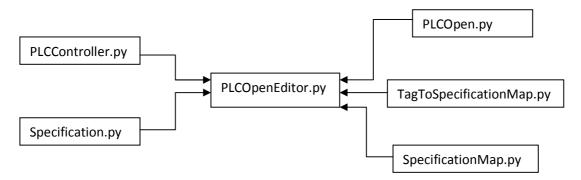

The following Fig.13 shows the main files of editor that have been extended in this project. Those classes that have been imported in "PLCOpenEditor.py" file have .py extension.

Fig.13- The files that have been changed or built in this project

The *"Specification.py"*, *"SpecificationMap"*, and *"TagToSpecificationMap"* have been built, and the other files just have been changed.

#### 2.1.2 Dividing Specification Panel

A specification panel has been divided to six parts. Each part has a label and a text field (shown in Fig.14), so it is more convenient for developer to enter the input texts into these text fields. The specification text should be saved in and be loaded from the file with .xml extension.

| Specification           |    |

|-------------------------|----|

| Operation Preconditions | ÷  |

| Operation Behaviours    | ÷  |

| Exception Conditions    | ÷. |

| Exception Behaviours    | 4  |

| Invariants              | *  |

| Variable Ranges         | ÷. |

Fig.14- specification panel view that has been integrated to PLCOpenEditor

#### 2.1.3 Resizing Specification Window

At this stage, a specification panel (i.e. Fig.14 )within PLCOpen Editor(i.e. main editor shown in Fig.12) has been created. However, PLCOPen Editor has many panels such as *variables* panel, library, project. Whenever the developer clicks on the *maximize* button(on the right corner of window), all of these panels will be resized to the maximum. The specification panel should also be maximized whenever the panels are maximized.

The code (i.e. shown in Table 3) was extended within "PLCOpenEditor.py" to provide a possibility for automatically resizing of the specification window. When a new file is opening to the main editor or clicking on maximize button that is available on the right corner of the main editor.

sizer = wx.FlexGridSizer(cols=2, hgap=6, vgap=6)

sizer.Hide(self)

sizer.AddMany([Ope\_PreLbl, (Ope\_PreTxt, 1, wx.EXPAND), Ope\_BehLbl, (Ope\_BehTxt, 1, wx.EXPAND), Exc\_ConLbl,

(Exc\_ConTxt, 1, wx.EXPAND),Exc\_BehLbl, (Exc\_BehTxt, 1, wx.EXPAND),InvariantsLbl, (InvariantsTxt, 1,

wx.EXPAND),VariablesLbl, (VariablesTxt, 1, wx.EXPAND)])

self.panel.SetSizer(sizer)

sizer.AddGrowableCol(1,0)

Table 3. Part of PLCOpenEditor code which extends the size of specification panel

The aim of the part of code that is shown in Table 3 is to solve the problem of resizing ability, to resize the specification panel whenever the size of main editor changes. The panel has put in a "sizer", the proportion is set to "1", and the wx.EXPAND style flag is used for each "widget" in order to resize each of the text fields within the panel. Here, a widget is an element of editor such as: text field, buttons, text area, etc [6]. The widget displays information arrangement changeable by user. All eight rows and the second column have been made growable. By this way, the text controls is allowed to be extended (i.e. growable), when the window is resized. The eight text controls will grow in horizontal direction. "wx.EXPAND" has been applied to make the widgets expandable.

#### 2.1.4 Switching Between Tabs

Inside the PLCOpenEditor (shown in Fig.12), the user can open different FBs. Whenever the user chooses a FB, one different tab is opened (for each FB). By clicking on tabs within editor different implementation and specification are shown. Since each tab in the PLCOpenEditor has its specific information, the user should visit different information regarding to different tabs when switches between various tabs. So it is expected that information change when the user switch to another tab. For instance, the information within each specification editor panel belongs to only one tab that is opened; hence the corresponding information should be updated by switching to another tab. hereafter this possibility of switching between different FB's is called Tab-Switching.

During the development of specification panel, there was a problem when user was switching to the next tab (Tab-Switching). The contents of specification within the text editor were the same as the information in the previous tab. while the contents should be changed over different tabs.

The quality of Tab-Switching for specification panel resembles from the previous implementation of Tab-Switching for Variable panel. In this example, each "Tab" has a "tag name", and each "Variable Panel" instance is associated to a tag name.

The class "TagToSpecificationMap ()" has been created in "TagToSpecificationMap.py" to be used for adding, updating the contents of specification panel to a hash map or removing those contents from the hash map. The classes within this file will be imported into PLCOpenEditor.py file.

The hash map data structure that keeps all specification information over different tabs was named: mySpecificationMap = {}, It is more efficient to find / search for items in a hash map than in a list.

For instance, if there are three tabs which are opened, myspecificationMap has all three part of information that loaded in the editor. Each one having the list of its own displayed specification. Whenever the user switches to a different tab, the list corresponding to that tab will be filled.