# Design and implementation of a central control unit in an automotive drive-by-wire system

Master of Science Thesis in Embedded Electronic System Design

Alexandra Angerd Andreas Johansson

Chalmers University of Technology University of Gothenburg Department of Computer Science and Engineering Gothenburg, Sweden, September 2013 The Author grants to Chalmers University of Technology and University of Gothenburg the non-exclusive right to publish the Work electronically and in a non-commercial purpose make it accessible on the Internet.

The Author warrants that he/she is the author to the Work, and warrants that the Work does not contain text, pictures or other material that violates copyright law.

The Author shall, when transferring the rights of the Work to a third party (for example a publisher or a company), acknowledge the third party about this agreement. If the Author has signed a copyright agreement with a third party regarding the Work, the Author warrants hereby that he/she has obtained any necessary permission from this third party to let Chalmers University of Technology and University of Gothenburg store the Work electronically and make it accessible on the Internet.

Design and implementation of a central control unit in an automotive drive-by-wire system

Alexandra Angerd Andreas Johansson

© ALEXANDRA ANGERD, September 2013. © ANDREAS JOHANSSON, September 2013.

Examiner: LARS SVENSSON

Chalmers University of Technology University of Gothenburg Department of Computer Science and Engineering SE-412 96 Göteborg Sweden Telephone + 46 (0)31-772 1000

Department of Computer Science and Engineering Göteborg, Sweden, September 2013

### Abstract

X-by-wire is a technique which is commonly used in aeronautics, but a challenge to face for the automotive industry. The objective of Sigma Kudos, which is a consultancy company in the automotive industry, is to implement a drive-by-wire system in a fullsize electric car. As part of the process of developing a prototype, the purpose of this project was to design a central control unit which would bring the prototype one step closer to vehicle implementation. In addition, the central control unit had to support an already existing system, containing throttle, brake, and steering functionality. To achieve this a platform was chosen, consisting of a TMS570 development board from Texas Instruments, and a GPL licensed FreeRTOS software platform from Real Time Engineers Ltd. The outcome of the project was an extensible platform with the potential of supporting full-size vehicles. However, questions arose regarding the use of an open source software platform in a safety-critical system, which is an issue that should be investigated further.

# Acknowledgements

We would like to offer our special thanks to David Rydén, our supervisor at Sigma Kudos Engineering Services, for his technical support and for sharing his insights into the automotive industry. We also would like to express our very great appreciation to our examiner Lars Svensson, for his academic support, constructive critique, and proof-reading of the report.

In addition, we wish to thank various people for their contribution to this project; Klas Persson, CEO at Sigma Kudos Engineering Services, who approved and initiated this project; Risat Pathan, for his help regarding response times in real-time systems; and Roger Johansson, for interesting discussions regarding real-time systems.

Alexandra Angerd and Andreas Johansson, Göteborg 4/9/13

# Contents

|          | $1.1 \\ 1.2$      |                                                                                          | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                   |

|----------|-------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|          | 1.2               | Purpo                                                                                    | se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                   |

|          |                   | Object                                                                                   | tive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                                   |

|          | 1.3               | Scope                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                   |

|          | 1.4               | Metho                                                                                    | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                   |

|          | 1.5               | Techn                                                                                    | cal background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                   |

|          |                   | 1.5.1                                                                                    | CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                   |

|          | 1.6               | Repor                                                                                    | t disposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                   |

| <b>2</b> | The               | e prior                                                                                  | prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                   |

|          | 2.1               | The st                                                                                   | eering subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                   |

|          | 2.2               | The th                                                                                   | rottle and brake subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                                                  |

|          | 2.3               | Evalua                                                                                   | ution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                  |

|          |                   | 2.3.1                                                                                    | Distribution of CAN bus and power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                  |

|          |                   | 2.3.2                                                                                    | Application code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                  |

| _        | Cha               | vice of                                                                                  | platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

| 3        | Und               |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                  |

| 3        | 3.1               |                                                                                          | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>16</b><br>16                                     |

| 3        |                   |                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |

| 3        |                   | The h                                                                                    | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16                                                  |

| 3        |                   | The ha<br>3.1.1<br>3.1.2                                                                 | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\begin{array}{c} 16 \\ 17 \end{array}$             |

| 3        | 3.1               | The ha<br>3.1.1<br>3.1.2                                                                 | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19                                      |

| 3        | 3.1               | The ha<br>3.1.1<br>3.1.2<br>The so                                                       | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19<br>19                                |

| 3        | 3.1<br>3.2        | The ha<br>3.1.1<br>3.1.2<br>The so<br>3.2.1                                              | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19<br>19<br>20                          |

|          | 3.1<br>3.2        | The ha<br>3.1.1<br>3.1.2<br>The so<br>3.2.1<br>3.2.2                                     | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19<br>19<br>20<br>22                    |

|          | 3.1<br>3.2<br>Imp | The ha<br>3.1.1<br>3.1.2<br>The so<br>3.2.1<br>3.2.2                                     | ardware platform       Candidates         Candidates       Discussion of choice         Discussion of choice       Candidates         oftware platform       Candidates         Candidates       Candidates         Discussion of choice       Candidates         Candidates       Candidates         Discussion of choice       Candidates         Candidates       Candidates | 16<br>17<br>19<br>19<br>20<br>22<br><b>23</b>       |

|          | 3.1<br>3.2<br>Imp | The ha<br>3.1.1<br>3.1.2<br>The so<br>3.2.1<br>3.2.2<br><b>blemen</b><br>Functi          | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19<br>20<br>22<br><b>23</b><br>23       |

|          | 3.1<br>3.2<br>Imp | The ha<br>3.1.1<br>3.1.2<br>The so<br>3.2.1<br>3.2.2<br><b>blemen</b><br>Functi<br>4.1.1 | ardware platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16<br>17<br>19<br>20<br>22<br><b>23</b><br>23<br>27 |

|              |      | 4.1.5 The LCD task                                                          | 32        |

|--------------|------|-----------------------------------------------------------------------------|-----------|

|              | 4.2  | Physical architecture                                                       | 34        |

|              |      |                                                                             | 34        |

|              |      |                                                                             | 36        |

|              |      |                                                                             | 37        |

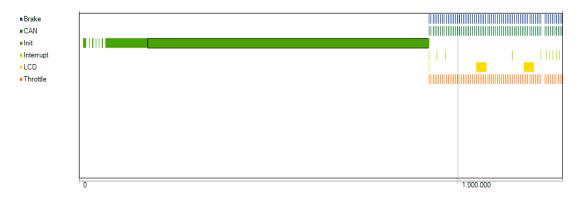

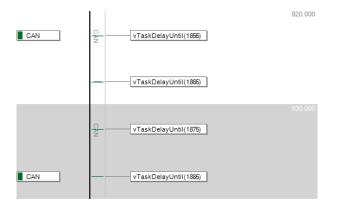

| <b>5</b>     | Res  | ource utilization and response time analysis                                | 39        |

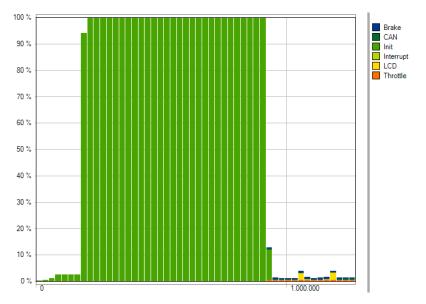

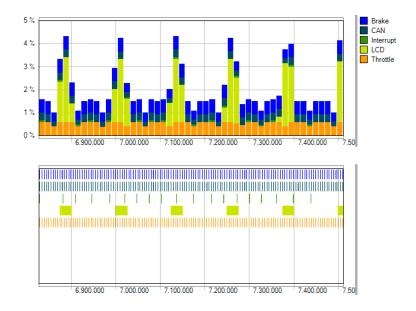

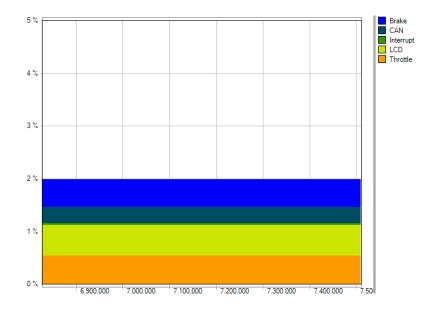

|              | 5.1  | Processor load                                                              | 39        |

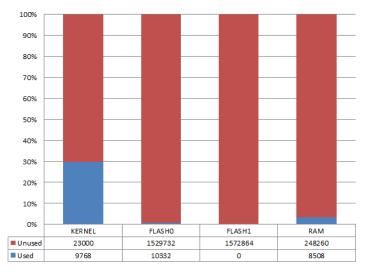

|              | 5.2  | Memory utilization                                                          | 43        |

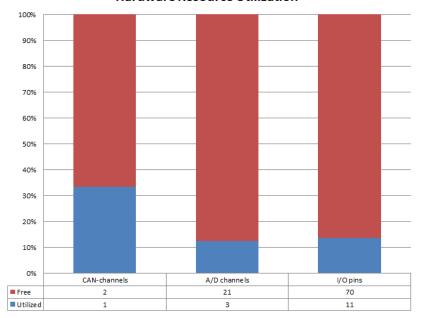

|              | 5.3  |                                                                             | 45        |

|              | 5.4  | Response time analysis                                                      | 47        |

| 6            | Disc | cussion                                                                     | <b>52</b> |

|              | 6.1  | The choice of platform                                                      | 52        |

|              | 6.2  | Future improvements                                                         | 54        |

|              |      | 6.2.1 Develop system guidelines                                             | 54        |

|              |      | 6.2.2 Replace the sensors, the receiver ECUs, and the display               | 54        |

|              |      | 6.2.3 Implement safety-critical properties                                  | 55        |

| 7            | Con  | aclusion                                                                    | 56        |

|              | Bib  | oliography                                                                  | 60        |

| $\mathbf{A}$ | Pin  | mappings                                                                    | 61        |

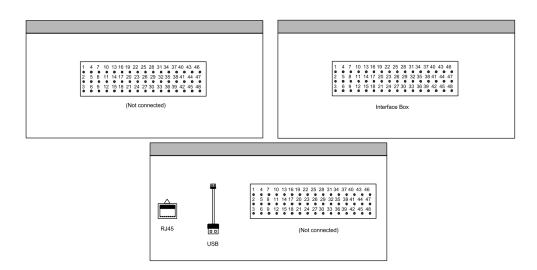

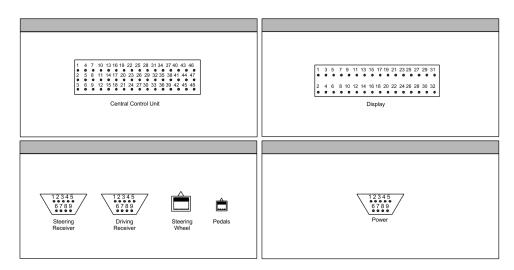

|              | A.1  | Pin setup and pin configurations of the D-SUB connectors                    | 61        |

|              | A.2  | Pin setup and pin configuration of the RJ10 connector                       | 63        |

|              | A.3  | Pin setup and pin configuration of the RJ45 connector                       | 64        |

|              | A.4  | Pin setup and pin configuration of the 48-pin industrial connector          | 65        |

|              | A.5  | Pin setup and pin configuration of the 32-pin industrial connector $\ldots$ | 67        |

| Acronym  | Description                                                                                                             |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| ABS      | Anti-lock Braking System                                                                                                |  |  |

| A/D      | Analogue-to-Digital                                                                                                     |  |  |

| ADC      | Analogue-to-Digital Converter                                                                                           |  |  |

| API      | Application Programming Interface                                                                                       |  |  |

| AUTOSAR  | Automotive Open System Architecture                                                                                     |  |  |

| AWG24    | American Wire Gauge 24, a standardized wire gauge size with a diameter of 0.511 mm                                      |  |  |

| BCD      | Binary-Coded Decimal                                                                                                    |  |  |

| BSW      | Basic Software                                                                                                          |  |  |

| CAN      | Controller Area Bus                                                                                                     |  |  |

| CAN-H    | CAN High                                                                                                                |  |  |

| CAN-L    | CAN Low                                                                                                                 |  |  |

| CCU      | Central Control Unit                                                                                                    |  |  |

| CRC      | Cyclic Redundancy Check                                                                                                 |  |  |

| DMIPS    | Dhrystone Million Instructions Per Second                                                                               |  |  |

| ECC      | Error-Correcting Code                                                                                                   |  |  |

| ECU      | Electrical Control Unit                                                                                                 |  |  |

| EMI      | Electromagnetic Interference                                                                                            |  |  |

| GIO      | General Input/Output                                                                                                    |  |  |

| GPL      | GNU General Public Licence                                                                                              |  |  |

| HalCoGen | HAL Code Generator Tool                                                                                                 |  |  |

| I/O      | Input/Output                                                                                                            |  |  |

| IDE      | Integrated Development Environment                                                                                      |  |  |

| IEC61508 | An international standard regarding functional safety in electri-<br>cal/electronic/programmable safety-related systems |  |  |

| ISR      | Interrupt Service Routine                                                                                               |  |  |

| LIN      | Local Interconnect Network                                                                                              |  |  |

| MIPS     | Million Instructions Per Second                                                                                         |  |  |

| PCB      | Printed Circuit Board                                                                                                   |  |  |

|          |                                                                                                                         |  |  |

# Abbreviations

| Acronym | Description                        |

|---------|------------------------------------|

| RC      | Radio Controlled                   |

| RISC    | Reduced Instruction Set Computing  |

| RJ10    | A connector with four pins         |

| RJ45    | A connector with eight pins        |

| RTE     | Runtime Environment                |

| RTI     | Real-Time Interrupt                |

| SIL     | Safety Integrity Level             |

| SPI     | Serial Peripheral Interface        |

| SWC     | Software Component                 |

| WHIS    | Wittenstein High Integrity Systems |

|         |                                    |

### Abbreviations, continued

# 1

# Introduction

RIVE-BY-WIRE IS A technique which aims to replace mechanical control systems in vehicles with an electronic equivalent, consisting of Electrical Control Units (ECUs), communication buses, sensors, and actuators. In a strict drive-bywire system, there is no mechanical connection between the driver's input interface and the actuators which control the speed and direction of the vehicle.

Already a well-used technique in aeronautics such as Airbus A320, X-by-wire is now a challenge to face for the automotive industry. Drive-by-wire in cars may offer a lot of benefits, such as making it easier to integrate driver assistance functions, reduce the repair time, and reduce the weight of the car. It also brings the technology one step closer to the driverless car, where one example is Google's autonomous car [1]. Google's autonomous car is a modified Toyota Prius, which uses a drive-by-wire system. Other car manufacturers, such as Volkswagen and Lexus, also use the drive-by-wire concept, although none of them are strictly drive-by-wire systems as they retain some mechanical links between the input interface and the actuators.

The objective of consulting company Sigma Kudos is to implement a strict drive-bywire system in a full-size electric car prototype, with the aim to attract new employees at job fairs and similar activities. The basic drive-by-wire prototype should include a solution which handles systems controlling the steering functionality, as well as the throttle and brake functionality. In addition, it has to be possible to add more functionality in the future. When this project began, some development had already been done, and the prototype consisted of two subsystems which operated in parallel.

# 1.1 Purpose

The two subsystems in the prior prototype contained two ECUs each, where one ECU in each subsystem was a sender ECU, and the other two were receiver ECUs. The system was undersized for use together with a full-size vehicle, as it was implemented in order to control wheels taken from a radio-controlled car. Thus, the purpose of this project was to prepare the drive-by-wire system for implementation in a full-size vehicle by designing a Central Control Unit (CCU), and thereby increasing the capacity of the prototype.

# 1.2 Objective

The main objective of the project was to restructure the prior solution by merging the two sender ECUs present in the prior prototype. This process included several milestones, such as choosing a suitable hardware and software platform, assemble the hardware, install the software platform, develop new application software, and make the new platform compatible with the prior prototype.

Furthermore, the solution had to be extensible, both with respect to hardware and software. This means that the capacity of the microcontroller in the CCU must be such that more functionality can be added without a significant performance loss. It also means that the system must be designed to support the possibility to include additional sensors and actuators in a future system.

A secondary objective of this project was to implement a temporary way to monitor the major activities inside the CCU. However, not much effort was spent on this part because in the future, the prototype will include a dashboard which holds this functionality.

## 1.3 Scope

Because the objective of this project was to reconfigure the existing system architecture, no new functionality was added to the wheel and engine control units. The reconfiguration did not involve replacement of the sensors and actuators used in the prior prototype.

In addition, the project was only supposed to bring the prototype one step closer to a complete product. Therefore, PCB design was avoided by using pre-assembled hardware as far as possible.

Even though fully implemented drive-by-wire systems require the properties of a fault-tolerant and safety-critical system [2], this was omitted from this project. However, the new CCU must have the capacity to implement at least some of these properties in the future.

## 1.4 Method

The project was carried out at Sigma Kudos Engineering Services. A supervisor at the company monitored the progress during weekly meetings throughout the project. At the meetings, the current status and problems were discussed, and the time plan was evaluated and modified if needed. All expenses of the project had to be approved by the supervisor, with the result that the company was responsible for all decisions regarding the budget.

In order to choose an appropriate platform for the CCU, a pre-study was carried out. The prior prototype was analyzed together with possible solutions found by a literature study, and requirements were determined. When the requirements of the new unit were set, a hardware platform was selected. In addition, based on this platform and the requirements of the software, a suitable software platform was chosen.

When the software and hardware platform had been selected, the implementation phase started. In this phase, the software and hardware were developed in parallel in an agile fashion. At last, an analysis of the CCU was made in order to determine how much resources the implementation consumes.

### 1.5 Technical background

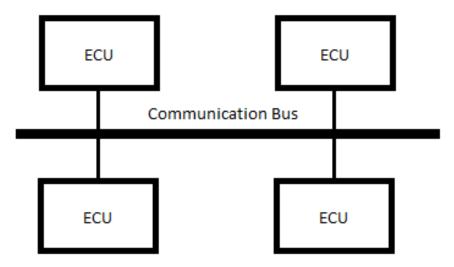

The modern vehicle of today is equipped with several ECUs. The ECUs are used in driver-to-vehicle interfaces, in actuator control, and in information gathering regarding the current vehicle state. For instance, one ECU may be responsible for displaying the current vehicle speed on the dashboard, while another ECU is responsible for controlling the Anti-lock Braking System (ABS). As seen in Figure 1.1, the ECUs are interconnected via a communication bus, which the ECUs use to send and receive data. Thus, data regarding the state of the ABS is presented on the dashboard, even though the dashboard is not directly connected to the brakes.

Figure 1.1: An illustration of how the ECUs are interconnected with a communication bus.

The communication bus is based on a communication protocol used by the ECUs. In the automotive industry, mainly two different communication protocols are available: FlexRay and Controller Area Network (CAN). The main differences between the two are that FlexRay offers higher reliability due to its redundancy features, and has a maximum transmission rate of 10 Mbps, while CAN has a maximum transmission rate of 1 Mbps. However, FlexRay is more expensive than CAN, which makes CAN a more suitable choice in low-budget projects [3]. Because of this, the prototype described in this report is using the CAN communication protocol.

### 1.5.1 CAN

CAN was designed by Bosch in 1983, and presented in 1984 at the Society of Automotive Engineers (SAE) [4]. The purpose of CAN was to increase the reliability and the fuelefficiency of the vehicle. Furthermore, it was intended to solve communication problems occurring when multiple ECUs are transmitting simultaneously [5].

A message sent over CAN is called a frame, and consists of several fields. The fields hold information regarding the frame, such as the number of data bytes, the data to be sent, and a frame identifier. The identifier is unique for each type of message, and in addition used for message prioritization. The total length of the frame depends on whether the frame is a base frame, with a length of 11 bytes, or an extended frame, with a length of 29 bytes. The additional 18 bytes in the extended frame are used to extend the number of available frame identifiers, making it possible to include more types of messages on the bus. Figure 1.2 illustrates the different fields in a CAN base frame.

Figure 1.2: Fields in a CAN base frame.

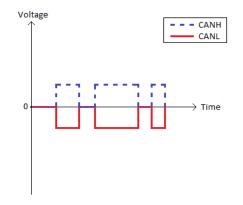

The transmission of a CAN frame is carried out using a differential bus consisting of two lines: CAN high and CAN low. Using a differential bus for communication reduces interference and allows for ground shifting. Furthermore, it allows the ECUs to have different supply voltages, as long as the differential voltage can be achieved in all nodes [6]. Figure 1.3 illustrates CAN high and CAN low during communication.

Figure 1.3: Figure of CAN high and CAN low during communication.

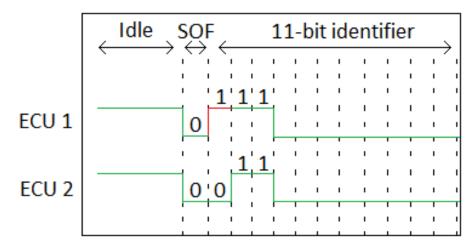

When the CAN bus is idle, the signal level of the bus is high. The Start-Of-Frame (SOF) bit signals that a transmission has started, by setting a low signal level on the bus. Following after the SOF bit is an 11-bit identifier, which sets the priority of the frame. A low identifier value on a CAN bus indicates a high priority. This behaviour is illustrated in Figure 1.4, where two ECUs are transmitting at the same time. In this example, the first ECU sends a frame with the identifier value seven, while the second ECU sends a frame with the identifier value six. When this happens, the message of the second ECU will be prioritized over the message of the first ECU. This is because a low signal value is dominant, while a high signal level is recessive [7].

Figure 1.4: A representation of how the signals are interpreted when two CAN messages are sent.

The identifier is followed by a Remote Frame Request (RFR) bit. This bit specifies if the frame requests data or if the frame intends to deliver data, which corresponds to a high or a low value on the bus, respectively [4] [5].

When the RTR is sent, a bit called Identifier Extension (IDE) is transmitted. The IDE informs the receiver about the type of frame being sent. If the IDE bit is set low, the frame is a base frame, and if it is set high, the frame is an extended frame. The IDE bit is followed by a reserved bit, which is set to the low dominant value.

The data is sent after a field called Data Length Code (DLC). This field specifies the number of data bytes, ranging between zero and eight bytes. In order to ensure that the frame is received correctly, a Cyclic Redundancy Check (CRC) is added to the frame. When all fields have been transmitted, End-Of-Frame (EOF) is signaled by setting the signal level high. At this point, the bus is available for a new frame transmission.

# **1.6** Report disposition

The report is structured as follows: the prior prototype, which was the foundation of this project, is described in chapter 2. In addition, the prior prototype is evaluated in order to find weak spots which can be reinforced by the new CCU prototype. In chapter 3, the selection process of a platform for the CCU is described. Possible hardware and software platforms are discussed, and the best suited candidates are chosen.

Chapter 4 explains the implementation of the new CCU, describing both the functional and the physical architecture. The resulting system is then analysed in chapter 5, where the CPU load, memory utilization, and pin and channel resources are presented. In addition, chapter 5 contains a response time analysis.

The resource analysis, the response time analysis and the problems encountered during the project are discussed in chapter 6. In addition, possible future projects are suggested.

The report ends with a conclusion in chapter 7, which also summarizes the project.

# 2

# The prior prototype

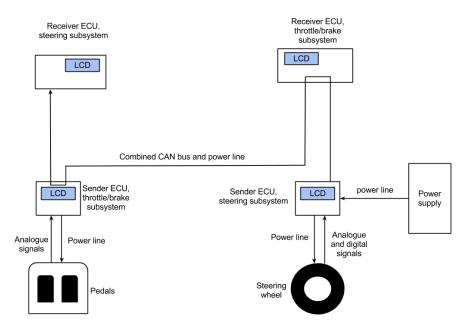

N ORDER TO understand the foundation on which this project stands, an evaluation of the prior prototype had to be done. The prototype consists of two separately developed subsystems, tied together with a CAN bus. The first subsystem implements steer-by-wire functionality, and consists of one sender ECU and one receiver ECU. The sender ECU converts an analogue value, corresponding to a steering wheel angle, into a digital value. The value is packed into a CAN message and transmitted on the CAN bus. The receiver ECU reads the CAN message, and sets a wheel position corresponding to the information given by the CAN message.

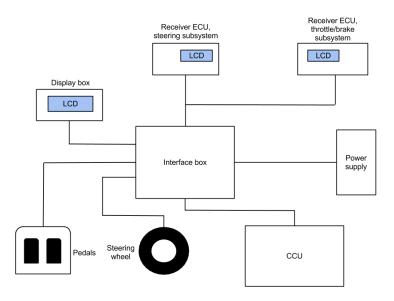

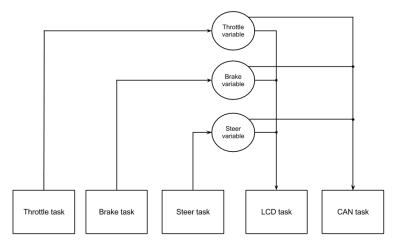

The other subsystem also consists of one sender and one receiver ECU, and works in a similar manner. However, this subsystem implements the brake- and throttle-bywire functionality. An overview of the prototype can be seen in Figure 2.1. As a result of the distributed system architecture, all ECUs execute independent of each other, disregarding the CAN bus. Because the CCU replaces the sender ECUs in the prior prototype, the emphasis on the evaluation are placed on the sender ECUs.

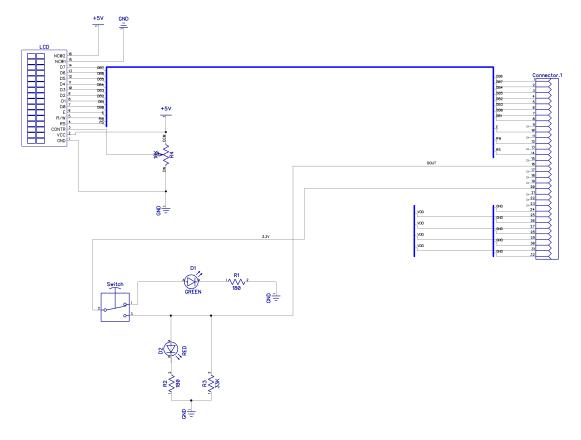

All ECUs are built on a microcontroller called ATmega128 [8]. The microcontroller includes an 8-bit AVR RISC-based processor, which is running at a frequency of 16 MHz. The throughput of the processor is about 1 MIPS per MHz. In addition to the microcontroller, a CAN transceiver [9] is available in each ECU. The CAN transceiver can be accessed by the microcontroller via the communication protocol Serial Peripheral Interface (SPI). Hence, the microcontroller is able to transmit and receive messages on the CAN bus by controlling the CAN transceiver via SPI. The CAN transceivers used in the existing system are designed to use CAN 2.0B, and configured to use the maximum transmission rate of 1 Mbit/s.

Moreover, the prototype is powered using a power box which offers two different voltage levels; 5 V with a maximum supply current of 2.1 A, and 12 V with a maximum supply current of 1.2 A. The power is distributed through the system via D-SUB cables. Since the power lines are traversing through all ECUs in the system, the CAN bus is

Figure 2.1: A simplified overview of the prior prototype.

distributed using the same D-SUB cables as the power lines.

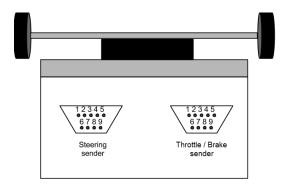

# 2.1 The steering subsystem

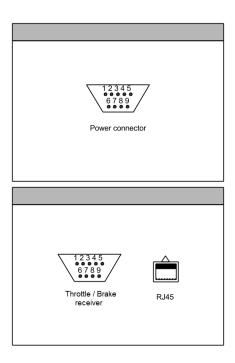

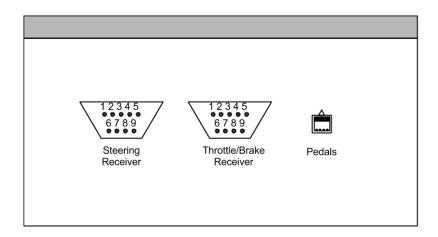

The physical architecture of the steering system consists of a steering wheel, a sender ECU, and a receiver ECU. The receiver ECU is directly connected to a pair of small wheels controlled by a servomotor. In order to communicate with the sender ECU, a D-SUB connector is mounted on the receiver ECU. In addition, it also controls a display. Figure 2.2 illustrates the receiver ECU.

The sender ECU, illustrated by Figure 2.3, includes two D-SUB connectors and one RJ45 connector. The first D-SUB connector is a power connector which receives a 12 V source and a 5 V source from the power box. Both of the power sources are redirected to the second D-SUB connector, the system connector, which in addition to the power sources also carries a CAN-H signal and a CAN-L signal. The system connector connects the sender ECU with the rest of the system, and thus distributes both the power sources and the CAN signals to the receiver ECU.

The RJ45 connector is used to connect the steering wheel to the sender ECU. In order to make it possible to read the angle of the steering wheel, an integrated circuit capable of measuring linear or rotary motion [10] is used. In this circuit, a magnet is used to generate signals to make it possible to read the direction of the motion. Hence, this circuit will be called the magnet sensor from this point forward. The relevant output signals from the magnet sensor which are used by the sender ECU are listed in Table 2.1. In addition to these signals, the RJ45 connector also carries the power supply for

Figure 2.2: Connector and wheels of the steering receiver ECU.

Figure 2.3: The connectors on the sender ECU of the steering subsystem.

| Pin name | • Type of signal |

|----------|------------------|

| А        | Digital          |

| В        | Digital          |

| Index    | Digital          |

| A0       | Analogue         |

Table 2.1: Output signals from the magnet sensor which are used by the sender ECU.

Table 2.2: Structure of the CAN message from the sender unit in the steering subsystem.

| CAN message configuration | Value              |

|---------------------------|--------------------|

| Data (field 0)            | Quadrature counter |

| Identifier                | 0x12C              |

| Length                    | 1 byte             |

the magnet sensor.

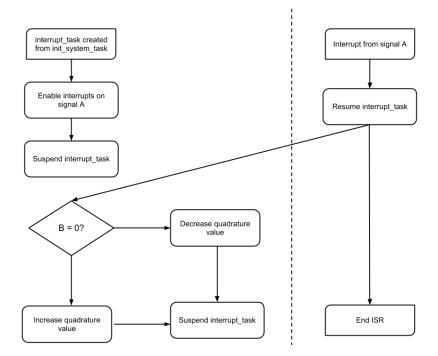

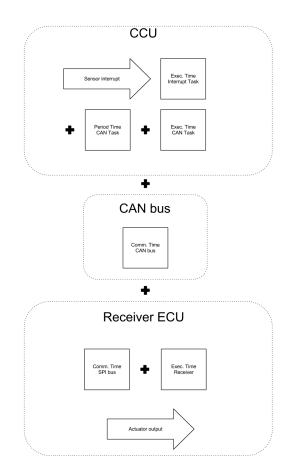

To decide the rotation of the steering wheel, the A and B signals are two pulse trains which are phase-shifted by  $90^{\circ}$ . If A leads B, the direction is clockwise. Similarly, if B leads A, the direction is counter-clockwise. Each pulse from the A and B signal are called a quadrature pulse, and a single index pulse is generated every 40 quadrature pulse. The index signal can be used to define a start position. The analogue signal A0 is used to calibrate the distance between the magnet and the sensor. If the value of analogue signal is out of bounds, the digital signals may be too weak to read.

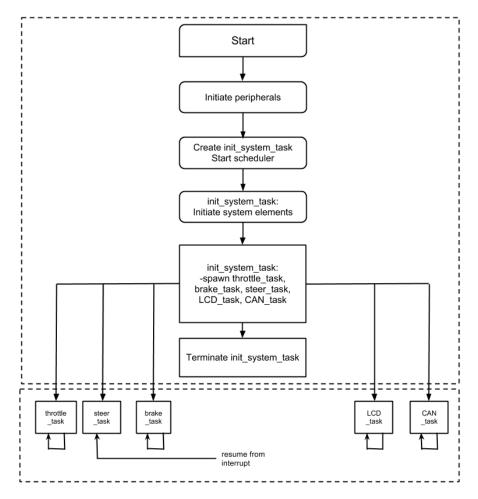

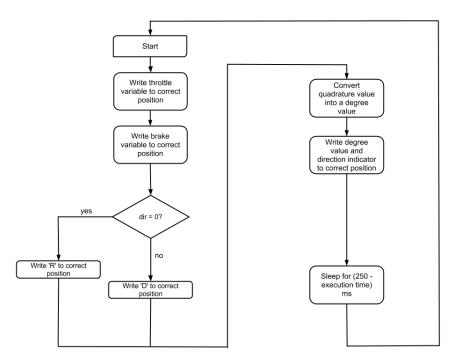

The responsibility of the sender ECU in this subsystem is to measure the steering wheel angle, show the angle at an LCD display, and transmit a CAN message to the receiver ECU. The software application of the sender ECU consists of an initiation phase and an infinite loop. In the initiation phase, all necessary initiations are made. An important part of this phase is to set a home position for the magnetic sensor. This makes it possible for the software to create a starting point for the magnetic sensor, and calculate the current position of the steering wheel.

After the initiation, the infinite loop is started. Within this loop, the software switches between three different functions, simulating a real-time behaviour where each task is given two milliseconds each. Although the software switches between three different tasks, only two of them are implemented, namely a CAN task and an LCD task. The LCD task converts a quadrature counter value, which is described below, to an ASCII value, and puts the steering rate and direction onto the display.

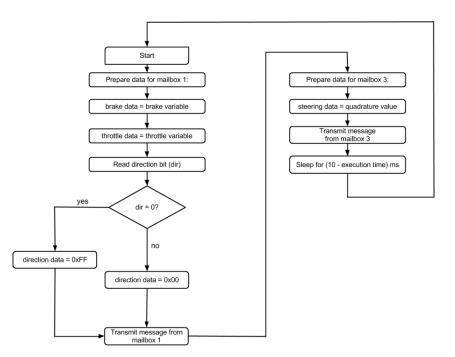

The CAN task creates a new CAN message, with the configurations shown in Table 2.2. After making sure that the CAN buffer is free, it puts the quadrature counter value into the data field of the CAN message and sends the message.

The value of the quadrature counter is initially set to 110. This value changes when

Figure 2.4: Connectors and wheels of the throttle and brake receiver ECU.

the A signal has a positive edge, as the A signal is used to generate interrupts. The interrupt handler reads the B signal from the magnet sensor. If the B value is equal to zero, the quadrature counter is increased. If the B value is greater than zero, the quadrature counter is decreased. In practise, this means that a quadrature counter value of 110 corresponds to a 0 degree steering wheel angle (straight forward), while a value greater than 110 corresponds to a clockwise rotation. A value less than 110 corresponds to a counter-clockwise rotation.

In parallel with the sender ECU, the receiver ECU waits for a CAN message to arrive. This is done in a busy-wait fashion. When it arrives, the value of the quadrature counter is converted into a BCD value which is written to the display attached to the receiver ECU. In addition, it scales the steering wheel angle  $(-180^{\circ} \text{ to } 180^{\circ})$  into an angle which makes sense for the wheels  $(-44^{\circ} \text{ to } 44^{\circ})$  and instructs the wheels to take the correct position.

### 2.2 The throttle and brake subsystem

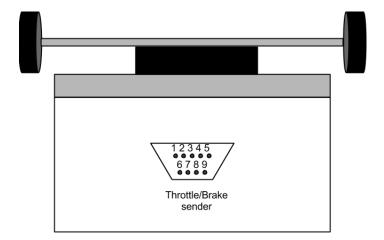

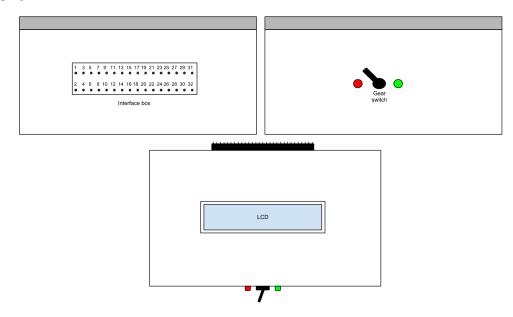

Like the steering subsystem, the brake and throttle subsystem also consists of a sender ECU and a receiver ECU. However, instead of a steering wheel, two pedals are used as input sensors, and a toggle switch is used as a gear shift. The receiver ECU communicates with the system via two D-SUB connectors. The reason why it needs two D-SUB connectors is to make it possible for the CAN and power signals to propagate in the system. Like the receiver ECU in the steering system, the brake and throttle receiver ECU also controls a display and two wheels. The receiver ECU is illustrated in Figure 2.4.

The sender ECU, illustrated by Figure 2.5, includes two D-SUB connectors and one RJ10 connector. The D-SUB connectors are shorted with each other inside the interface box, in such a way that the pins of the first connector is connected with the corresponding pins of the second connector. This setup makes it possible for the power lines and the CAN bus to traverse to the next node in the system. The pin configuration of the D-SUB cables is the same as in the steering sender ECU, and can be found in Appendix A.

Figure 2.5: Connectors mounted on the throttle and brake sender ECU.

Table 2.3: Output signals from the pedals that are used by the sender ECU.

| Pin name       | Type of signal |

|----------------|----------------|

| Throttle value | Analogue       |

| Brake value    | Analogue       |

The RJ10 connector is used in order for the ECU to read the position of the pedals. The pedals are connected to one potentiometer each, which makes it possible to change the voltage level that is carried by the RJ10 cables. Thus, a certain voltage level corresponds to a certain pedal position.

Two output signals from the RJ10 connector are relevant for the software application in the sender ECU, and those are shown in Table 2.3. In addition to the pedals, the software application uses the toggle switch to decide the gear position (drive or reverse). The toggle switch sends out a single digital signal, which is high if the direction is set to reverse, and low if the direction is set to drive.

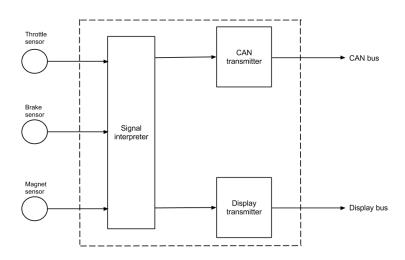

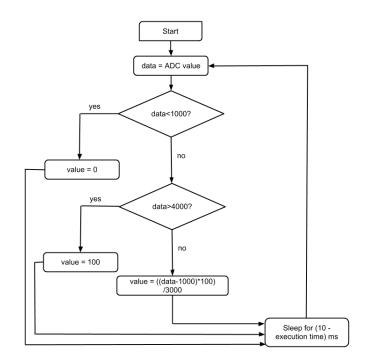

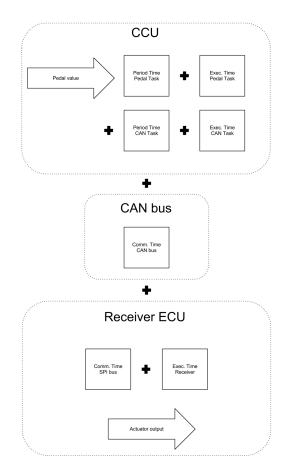

The software of the sender ECU consists of an initiation phase, where the LCD, the ADC, and the CAN peripherals are initiated. In addition, an A/D conversion is started. This is followed by a loop which works in a busy-wait fashion. At the beginning of the loop, a CAN-message is sent. After that, the LCD is updated if a counter has reached the value of 10 000 (every 10 000th loop revolution). This LCD routine only updates the default information on the display.

The next step is to check whether a new A/D value, coming from the throttle and brake signals, has arrived or not. A checkbit is used in order to know if a new value has arrived. When the A/D-conversion is finished, an interrupt is sent, and an interrupt handler sets the checkbit. When the checkbit is set and a new A/D value has arrived, the value is converted into a percentage. The software checks if the value came from the throttle or the brake by identifying the latest used A/D converter. The percentage, and

| CAN message configuration | Value                                           |

|---------------------------|-------------------------------------------------|

| Data (field 0)            | Brake percentage                                |

| Data (field 1)            | Throttle percentage                             |

| Data (field 2)            | Direction (drive $(0xFF)$ or reverse $(0x00)$ ) |

| Identifier                | 0x01                                            |

| Length                    | 3 bytes                                         |

Table 2.4:

Structure of the CAN message from the sender unit in the throttle and brake subsystem.

the direction (forward or reverse) if the value came from the throttle pedal, is written to the display and also put into a CAN message. The percentage value in the display is only updated every 150th loop revolution, while the CAN message, with the configuration shown in Table 2.4, is updated and transmitted every loop revolution. When the CAN message is transmitted, the A/D converter is restarted and the checkbit is unset. During one second the busy-wait loop laps about 150 times [11], which gives a loop period of approximately 6.7 milliseconds.

As for the steering subsystem, the receiver ECU of the throttle and brake subsystem executes in parallel with the sender ECU. After some initiations are made, a busy-wait loops waits for a CAN message to arrive. When a message arrives, throttle signals are sent to the wheels, and the brake value is sent to a servomotor. Also, the software reads the direction bit and sets an H-bridge to the correct configuration to make the wheels spin in the desired direction.

# 2.3 Evaluation

The system is functional, but several components could be modified to optimize the functionality, and to prepare the system for industrial implementation.

### 2.3.1 Distribution of CAN bus and power

The physical architecture solution is sufficient for the prior prototype, but if future modifications are to be done, several parts of the hardware need to be altered. One reason for this is that the distribution of the CAN network and the power sources is built as a chain, where each ECU has to be connected in a particular order. If they are not connected in the correct order, or if an ECU is disconnected, the consequence may be voltage drops, or that the CAN and power sources do not reach all ECUs. It may also result in interference on the CAN bus, as the bus terminations may be positioned at inappropriate places.

The unit that acts as a power supply includes two different power sources; a 5 V source with a maximum current of 2.1 A, and a 12 V source with a maximum current of 1.2 A. Both of them are distributed via a D-SUB cable along with ground. In addition, the 5 V supply is distributed via two plug cables, as the amount of current drawn by the components in the system is too high for the D-SUB cable to carry.

The power sources given by the central power supply are sufficient to support the prior prototype. However, if nodes with higher power consumption are added, neither the power supply nor the distribution are suitable as is. As the power supply limits the amount of voltage levels and current available, the D-SUB cables have a small crosssectional area which limits the amount of current that can be distributed. Thus, in the future, both the power supply and the distribution method have to be upgraded.

The CAN bus is distributed using the same D-SUB cables as the power sources. This is not the ideal case since cables used for communication are commonly divided in twisted pairs, as illustrated by Figure 2.6, to cancel out electromagnetic interference (EMI). Since the prior prototype is small, this does not cause immediate problems. However, when the prototype is installed in an actual vehicle, the electromagnetic interference will be at a much higher level, which demands the cables to be arranged as twisted pairs.

Figure 2.6: Twisted pair.

In addition, EMI that interferes with the CAN bus may occur when the power supply

is upgraded to a more powerful alternative, as the amount of current in the cables will be higher. Thus, it is suitable to separate the CAN bus and the cables that carry the power.

### 2.3.2 Application code

The software of the ECUs have been developed ad-hoc with busy-wait loops. This results in a software architecture which is hard to overview, and it is also complex to add new functionality to the ECUs without disturbing the existing functionality. Even though the busy-wait loops provide a sufficient response time for the prior prototype, this might not be the case if additional functionality is added.

In the new prototype, the sender units will be merged into a centralized unit, and new functionality will be added in the future. This results in a more complex application code which is hard to maintain, alter, and analyze if built ad-hoc, and the need of a structured software platform is clear. Furthermore, in order to provide a way to speed up the execution, parallelization of the functionality is needed.

Also, the CAN identifiers are set arbitrarily. A systematic way of assigning identifiers would make the system easier to understand, especially when it grows larger. Furthermore, CAN identifiers are used to assign priority to the messages. This means that if the identifiers are set arbitrarily, the inherent priorities may cause problems for critical systems, as non-critical systems may have a higher priority. However, it is not possible to assign new identifiers during this project. This is because the functionality of the CCU in this project must be compatible with the old system, and hence, the CAN messages sent out by the CCU must look like the ones transmitted from the sender units. The task of assigning more suitable identifiers is therefore omitted until the receiver units are replaced.

In addition to the arbitrary identifiers, the speed of the CAN communication is set to 1 Mbit/s. That speed is not necessary in the prior prototype, and could be optimized in a later stage. However, as the future prototype might be altered in a way that puts a high load on the bus, this optimization is omitted until the system is complete.

# 3

# Choice of platform

HERE ARE THREE main requirements on the new central unit. First, the system needs to include the old functionality of the two senders from the previous subsystems. Second, it should be extensible, both with respect to hardware and software. This means that the hardware platform needs to include a lot of resources to make it possible to add more sensors, actuators, and buses. This also means that the software must be structured in such a way that it is easy to add new functionality without the need of rewriting large parts of the existing code. Third, the new unit needs to be easy to understand in order to make it easy to use and alter it in the future.

In order to fulfill these requirements, both a hardware platform and a software platform had to be chosen. This was carried out by setting more detailed requirements for each platform, finding candidates, and choosing the ones that best fit the set requirements.

## 3.1 The hardware platform

The scope of this project states that PCB design shall be avoided. Therefore, the best solution is a development board already containing as much needed resources as possible. The resources required by the sensors and means of communication for the prior prototype are four digital I/O-pins, three ADC channels, and one CAN channel. Thus, more than four I/O-pins and three ADC channels are required in order to connect additional sensors to the system. Because it is impossible to guess how many I/O pins that might be needed for future sensors, as many I/O pins and ADC-channels as possible is preferred.

The prior prototype requires one CAN channel, which is sufficient to communicate with a lot of ECUs. However, one additional CAN channel is preferred to make it possible to physically separate future critical and non-critical CAN messages, as well as to offer a way to implement redundancy of the CAN-bus. Also, a Local Interconnect Network (LIN) channel might be useful to relieve the CAN bus from communication that is less time-critical than the communication between the ECUs.

In addition to the these requirements, the microcontroller of the chosen development board has to be powerful enough to support both the functionality of the sender ECUs in the prior prototype, but also have the capacity to support a lot of new functionality. This includes both the speed of the CPU as well as the size of the internal memory.

#### 3.1.1 Candidates

When the requirements were set, possible hardware platforms were considered. Several development boards were discovered, but only a few were investigated in more detail. The ones that best fitted the requirements are presented below.

### The AVR UC3 Evaluation Kit

The AVR UC3C Evaluation Kit [12] is a development board designed to be able to act as a prototype for motor control. It is built with the microcontroller AT32UC3C0512C [13], which has a 32-bit AVR processor with a performance of 1.49 DMIPS <sup>1</sup> per MHz, running at a maximum frequency of 66 MHz. It has several digital I/O pins and 16 analogue input channels with a resolution of 12 bits. In addition, the microcontroller is equipped with two CAN channels and five LIN channels, 512 KB of internal flash and 256 KB of internal RAM. With these specifications, the microcontroller itself fulfills all the requirements listed for the hardware platform.

The kit is designed in a way which makes is possible for the user to test all the functionality in the microcontroller, using only the evaluation board. It is equipped with a lot of additional hardware, such as an audio jack, a microphone, LEDs, push buttons, a capacitive touch screen, and several other interfaces. The available CAN channels in the microcontroller are connected to CAN controllers and external connectors. In addition, two of the five LIN channels are available for use on the evaluation board.

### The TMS570 Hercules Development Kit

Texas Instruments offers a microcontroller called TMS570LS3137 [14]. It is built around a 32-bit ARM Cortex-R4F microprocessor, which is running at a maximum frequency of 180 MHz, performing 1.6 DMIPS per MHz. It is designed to be used in safety-critical systems, such as braking systems and electric power steering, and uses two lock-stepped CPUs with error detection logic. The microcontroller is provided with three CAN channels, two FlexRay channels, two analogue-to-digital converters, one ethernet channel, and one LIN channel. In addition, it has several digital I/O-pins, and two 12bit ADC modules, where the first module supports 24 channels, and the second module supports 16 channels, all of which are shared with the first module.

<sup>&</sup>lt;sup>1</sup>Dhrystone MIPS, a benchmark for measuring general processor performance.