# **Voltage Oriented Control of Three-Phase Boost PWM Converters**

Design, simulation and implementation of a 3-phase boost battery charger

Master of Science Thesis in Electric Power Engineering

## Sylvain LECHAT SANJUAN

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden, 2010

## Voltage Oriented Control of Three-Phase Boost PWM Converters

Design, simulation and implementation of a 3-phase boost battery charger

Ву

Sylvain LECHAT SANJUAN

**Supervisor**

Saeid Haghbin, PhD Student

Examiner

Ola Carlson, Associate Professor

Department of Energy and Environment

Division of Electric Power Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden, 2010

## **VOLTAGE ORIENTED CONTROL OF THREE-PHASE BOOST PWM CONVERTERS**

DESIGN, SIMULATION AND IMPLEMENTATION OF A 3-PHASE BOOST BATTERY CHARGER SYLVAIN LECHAT SANJUAN

© SYLVAIN LECHAT SANJUAN, 2010

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY SE-412 96 Göteborg Sweden

Telephone: +46 (0)31-772 1000

## **ABSTRACT**

#### **Voltage Oriented Control of Three-Phase Boost PWM Converters**

Design, simulation and implementation of a 3-phase boost battery charger

Sylvain LECHAT SANJUAN

Department of Energy and Environment

Division of Electric Power Engineering

Chalmers University of Technology

In a plug-in hybrid electric vehicle, the utility grid will charge the vehicle battery through the battery charger. For a three-phase grid supply voltage, three-phase boost rectifiers are a commonly used scheme for chargers. Bi-directional power transfer capability and unit power factor operation are interesting features that can be achieved by the method proposed in this thesis. Different control strategies have been proposed to control the converter. The Voltage Oriented Control is one of these methods based on high performance dq-coordinate controllers.

The Voltage Oriented Control method for a three-phase boost rectifier have been designed and simulated. Moreover, an implementation of the system has been started. The system simulation has been done using Matlab/Simulink software. Feedforward decoupled current controller has been designed along with Pulse Width Modulation scheme to control the battery charging. The controller, that is, a current controller and a DC-link voltage controller, have been designed using a method called Internal Model Control. The simulation results have been presented and the control system performance evaluated in response to the load and dc-bus voltage step changes.

dSpace system have been used for practical implementation. The system is directly running a Simulink model as a controller. The Simulink files have been developed for this purpose. A brief explanation of the system configuration has been provided for the experimental system.

Key words: battery charger, decoupled controller, dSpace, Internal Model Control (IMC), Pulse Width Modulation (PWM), three-phase boost PWM rectifier, Voltage Oriented Control (VOC).

## **ACKNOWLEDGEMENTS**

First of all, I would like to express my sincere gratitude to Saeid Haghbin, my supervisor, for his total availability during the thesis, for his understanding, technical guidance and friendliness.

My gratitude also goes to Ola Carlson, for giving me the opportunity to do this Master's Thesis work in the Electric Power division of Chalmers University of Technology.

A very special thanks to Stefan Lundberg and Massimo Bongiorno, for all help, their availability, technical guidance and nice discussions.

Thanks to all the employees and staff in the division who made my thesis work such a pleasant stay. Furthermore, I would like to thank Magnus Ellsen for his availability and help for laboratory set-up.

Finally, many thanks to my fellow Master's Thesis students with Saman Babaei, Thinley Gyeltshen, Francisco Montes Venero, Peng Hou, Sergio Garcia Collino and Johan Andersson. Thanks for their support, guidance and nice discussions. They also made my stay in Sweden an unforgettable experience.

Sylvain Lechat Sanjuan Göteborg, Sweden Wednesday, June 16, 2010

## LIST OF SYMBOLS, SUPERSCRIPTS, SUBSCRIPTS AND ABBREVIATIONS

#### **ABBREVIATIONS**

DPC Direct Power Control IC Initial Condition

IGBT Insulated Gate Bipolar Transistor

IMInduction MachineIMCInternal Model ControlPWMPulse Width ModulationPLLPhase Locked Loop

**PMSM** Permanent Magnet Synchronous Machine

**SVM** Space Vector Modulation

VF-DPCVFOCVocVirtual Flux Oriented ControlVoltage Oriented Control

#### **SYMBOL**

U Line voltageE Line voltage

$E_q$  Grid phase-to-ground voltage amplitude

$E_d$  and  $E_q$  dq-coordinates of line or grid voltage (amplitude invariant transformation)

**Vpcc** Voltage at the point of common connection

Us Converter voltageV Converter voltage

V\* Converter voltage reference from current controller

$egin{array}{ll} oldsymbol{V_{LL}} & {

m Line-to-Line\ voltage} \ oldsymbol{V_{LN}} & {

m Line-to-Neutral\ voltage} \ \end{array}$

$v_{dc}$ ,  $V_{DC}$  DC-link voltage

$oldsymbol{v_c}$  Voltage across AC-side capacitor

i<sub>L</sub> Line currenti Line current

*i*<sub>CONV</sub> Line current, current flowing into the converter

$egin{array}{lll} egin{array}{lll} egin{array}{lll} egin{array}{lll} egin{array}{lll} egin{array}{lll} DC-link current \\ L & Line resistance \\ L & Line inductance \\ C & DC-link capacitor \\ R_g & Grid resistance \\ L_g & Grid inductance \\ \end{array}$

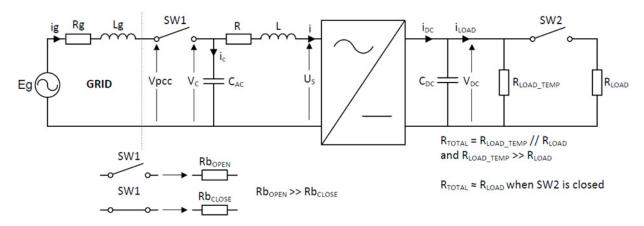

**R**<sub>b</sub> Breaker SW1 resistance

$egin{array}{ll} m{\mathcal{C}}_{ac} & & \mathsf{AC} \ \mathsf{capacitor} \ m{\mathcal{C}}_{dc} & & \mathsf{DC} \ \mathsf{capacitor} \ m{\mathcal{R}}_{LOAD} & & \mathsf{Load} \ \mathsf{resistance} \end{array}$

$R_{LOAD\_TEMP}$  Temporary load resistance

\theta Voltage angle

\textit{F}\_S Sampling frequency}

\textit{Ts} Sampling time

**F**<sub>SW</sub> Switching frequency

$egin{array}{ll} F_C & {

m Triangular \ wave \ frequency \ (PWM)} \ F_{Triangle} & {

m Triangular \ wave \ frequency \ (PWM)} \ lpha_i & {

m Current \ controller \ bandwidth \ (rad/s)} \ lpha_v & {

m Voltage \ controller \ bandwidth \ (rad/s)} \ \end{array}$

**Ga** Active damping conductance

$egin{array}{ll} \emph{K}\emph{i}_{\emph{v}} & \mbox{Voltage controller integrator coefficient} \\ \emph{K}\emph{p}_{\emph{v}} & \mbox{Voltage controller proportional coefficient} \\ \emph{K}\emph{i}_{\emph{i}} & \mbox{Current controller integrator coefficient} \\ \emph{K}\emph{p}_{\emph{i}} & \mbox{Current controller proportional coefficient} \\ \end{array}$

$egin{array}{lll} egin{array}{lll} egin{arra$

$oldsymbol{

ho}$  PLL bandwidth

F(s) Controller transfer function (PI) G(s) Process transfer function L(s) Open-loop transfer function S(s) Closed-loop transfer function

W  $v_{dc}^2$

$egin{array}{ll} {P_g} & & { ext{Grid power}} \ {P_{load}} & & { ext{Load power}} \end{array}$

## **SUPERSCRIPT, ACCENTS**

$\widehat{E}_g$ ,  $\widehat{C}$ ,  $\widehat{L}$ ,  $\widehat{R}$  Estimated values  $x^s$  Space vector

$x^{dq}$  dq-coordinate system  $x^*$  Reference value of x

## SUBSCRIPT, UNDERLINE

$x_{dq}$  dq-coordinate system

$\underline{x}$  dq-coordinate system, complex value

## **TABLE OF CONTENTS**

| AE         | <u>SSTRACT</u> |                                                       |                                                            | IV       |  |

|------------|----------------|-------------------------------------------------------|------------------------------------------------------------|----------|--|

| <u>A(</u>  | CKNOWLE        | DGEMENTS                                              |                                                            | v        |  |

| <u>LIS</u> | ST OF SYN      | MBOLS, SUP                                            | ERSCRIPTS, SUBSCRIPTS AND ABBREVIATIONS                    | VI       |  |

| <u>1</u>   | INTROD         | UCTION AN                                             | D SCOPE                                                    | 1        |  |

| <u>2</u>   | THREE P        | HASE CONT                                             | ROLLED RECTIFIERS                                          | 3        |  |

|            | 2.1            | Introduction                                          | on.                                                        | 3        |  |

|            |                |                                                       | pridge topology                                            | 5        |  |

|            |                | 2.2.1                                                 | Steady state operation                                     | 5        |  |

|            |                | 2.2.2                                                 | Mathematical model                                         | 5        |  |

|            |                | 2.2.3                                                 | Limitations                                                | 9        |  |

|            | 2.3            | Control str                                           | ategies                                                    | 11       |  |

|            |                | 2.3.1                                                 | Introduction                                               | 11       |  |

|            |                | 2.3.2                                                 | Direct Power Control and Virtual Flux Direct Power Control | 12       |  |

|            |                | 2.3.3                                                 | Voltage and Virtual Flux Oriented Control                  | 13       |  |

|            |                | 2.3.4                                                 | Comparison and discussion                                  | 14       |  |

|            | 2.4            | Pulse Widt                                            | th Modulation                                              | 15       |  |

|            |                | 2.4.1                                                 | Sinusoidal PWM                                             | 15       |  |

|            |                | 2.4.2                                                 | Digital implementation                                     | 16       |  |

|            |                | 2.4.3                                                 | Dead time effect                                           | 16       |  |

| <u>3</u>   | VOLTAG         | E ORIENTED                                            | CONTROL – SIMULATION                                       | 18       |  |

|            | 2 1            | Introduction                                          | on - References chasen                                     | 18       |  |

|            |                | Introduction – References chosen System block diagram |                                                            | 19       |  |

|            |                | PWM Simu                                              | _                                                          | 20       |  |

|            | 3.3            | 3.3.1                                                 | Simulink implementation of PWM                             | 20       |  |

|            | 3.4            | Current co                                            | ·                                                          | 22       |  |

|            |                | 3.4.1 Internal Model Control                          |                                                            |          |  |

|            |                | 3.4.2                                                 | Synchronous PI control                                     | 22<br>22 |  |

|            |                | 3.4.3                                                 | Design of the synchronous PI controller                    | 23       |  |

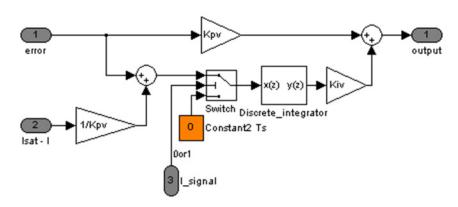

|            |                | 3.4.4                                                 | Active damping, voltage saturation, anti-windup            | 25       |  |

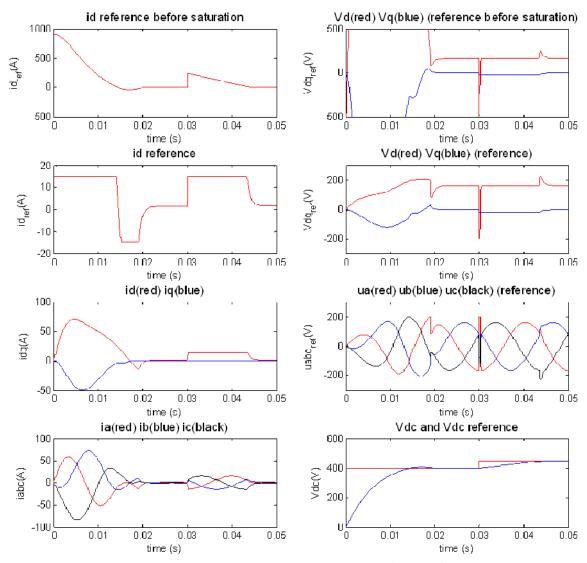

|            |                | 3.4.5                                                 | Current controller simulation                              | 27       |  |

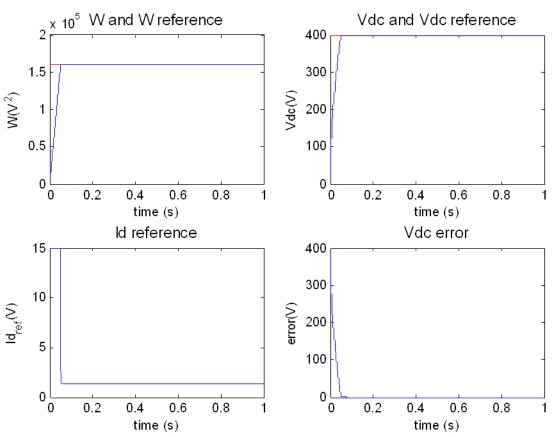

|            | 3.5            | DC-link vo                                            | tage controller                                            | 30       |  |

|            |                | 3.5.1                                                 | DC-link model and linearization                            | 30       |  |

|            |                | 3.5.2                                                 | Design of voltage controller                               | 30       |  |

|            |                | 3.5.3                                                 | Voltage saturation, anti-windup, active damping            | 31       |  |

|            |                | 3.5.4                                                 | Voltage controller simulation                              | 33       |  |

|            |                | 3.5.5                                                 | Simulation with current controller                         | 36       |  |

|            |                | 3.5.6                                                 | Controller improvements                                    | 39       |  |

|            | 3.6            | Stability ar                                          | nalysis                                                    | 41       |  |

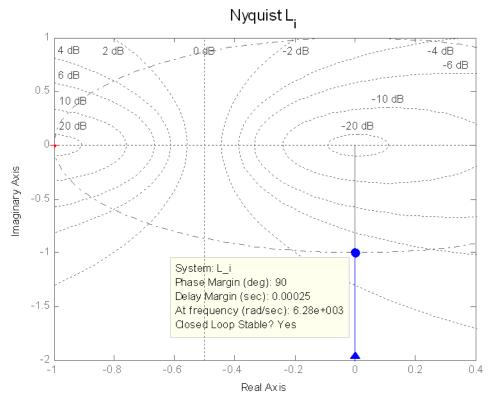

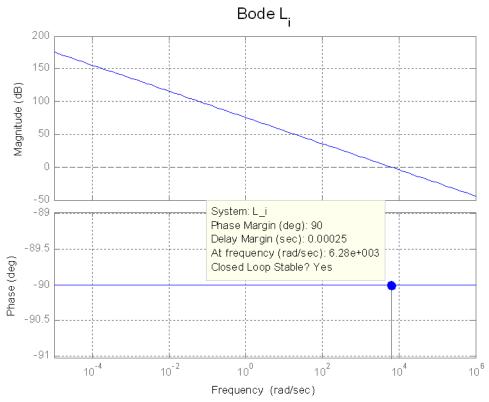

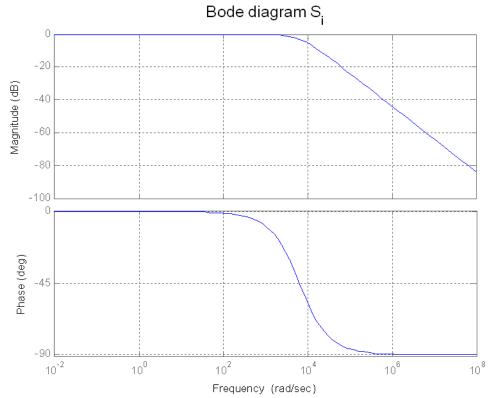

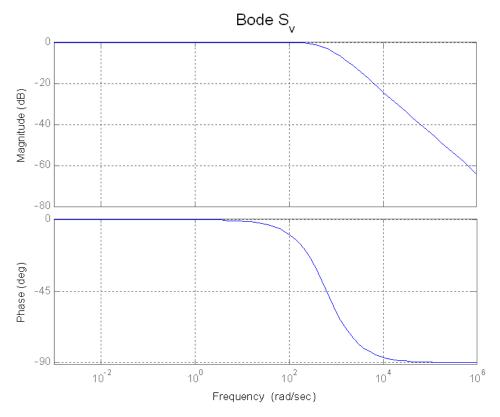

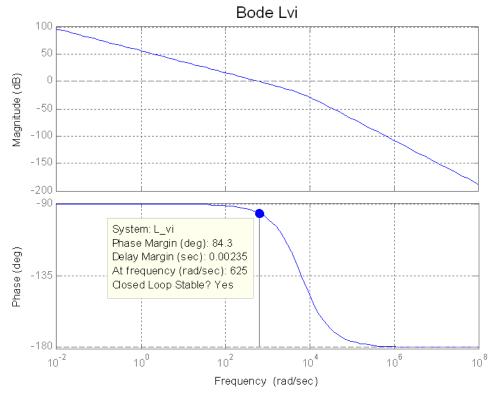

|                              | 3.6.1                                                                                                                                         | Current controller                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                          |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

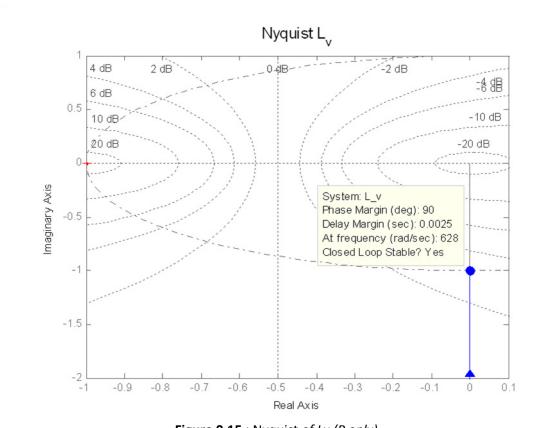

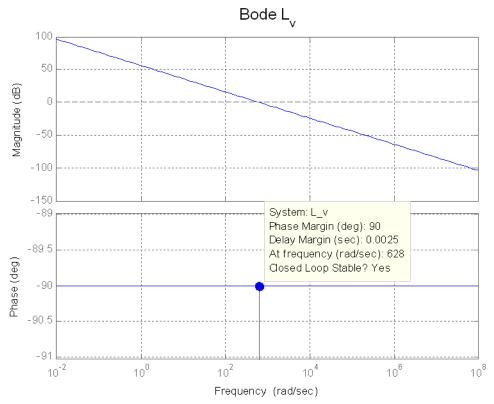

|                              | 3.6.2                                                                                                                                         | Voltage controller                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                          |

|                              | 3.6.3                                                                                                                                         | Complete controller                                                                                                                                                                                                                                                                                                                                     | 42                                                                                                          |

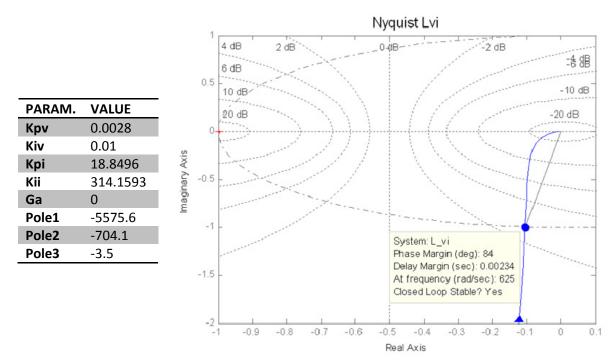

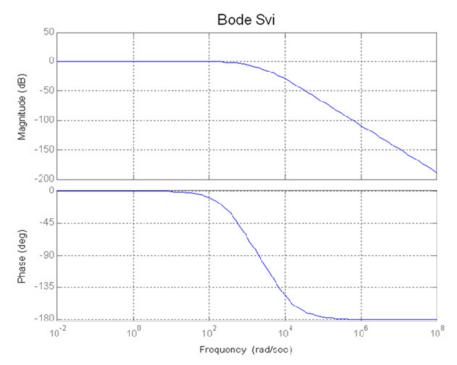

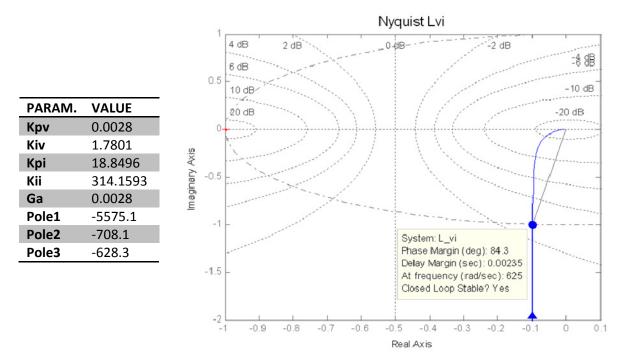

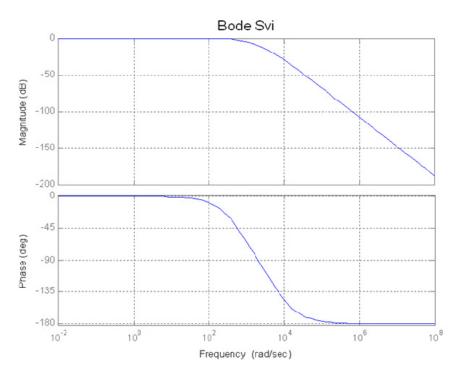

|                              | 3.6.4                                                                                                                                         | Nyquist and Bode diagram                                                                                                                                                                                                                                                                                                                                | 43                                                                                                          |

|                              | 3.6.5                                                                                                                                         | Conclusion                                                                                                                                                                                                                                                                                                                                              | 46                                                                                                          |

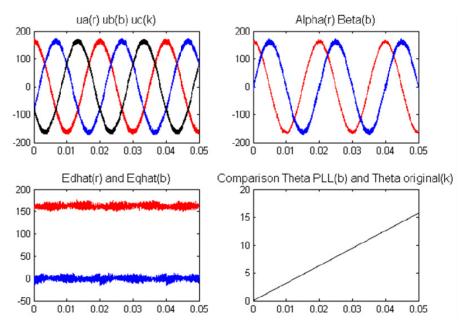

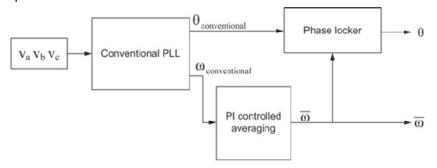

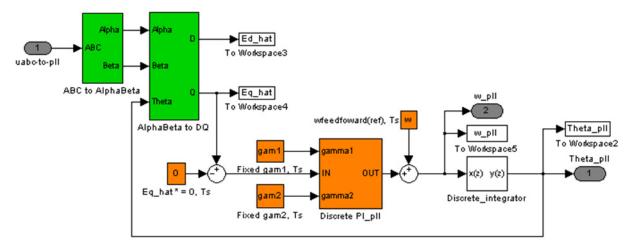

| 3.7                          | Phase Lock                                                                                                                                    | ked Loop (PLL)                                                                                                                                                                                                                                                                                                                                          | 48                                                                                                          |

|                              | 3.7.1                                                                                                                                         | Design                                                                                                                                                                                                                                                                                                                                                  | 48                                                                                                          |

|                              | 3.7.2                                                                                                                                         | Simulations                                                                                                                                                                                                                                                                                                                                             | 48                                                                                                          |

|                              | 3.7.3                                                                                                                                         | Improvements and conclusion                                                                                                                                                                                                                                                                                                                             | 52                                                                                                          |

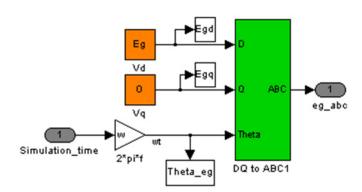

|                              | Grid mode                                                                                                                                     | <u> </u>                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                          |

| 3.9                          |                                                                                                                                               | ected converter simulation                                                                                                                                                                                                                                                                                                                              | 55                                                                                                          |

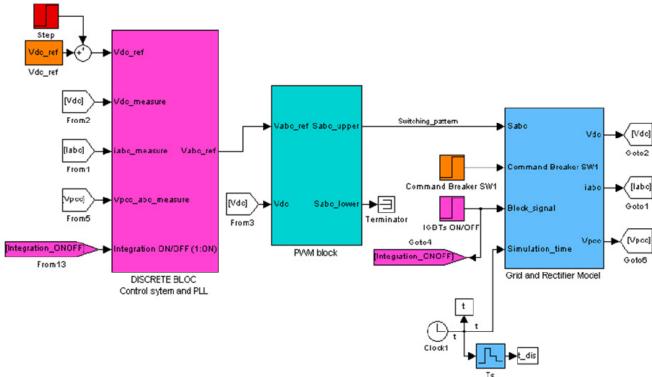

|                              | 3.9.1                                                                                                                                         | Simulation steps, Simulink block diagram                                                                                                                                                                                                                                                                                                                | 55                                                                                                          |

|                              | 3.9.2                                                                                                                                         | Verification                                                                                                                                                                                                                                                                                                                                            | 56                                                                                                          |

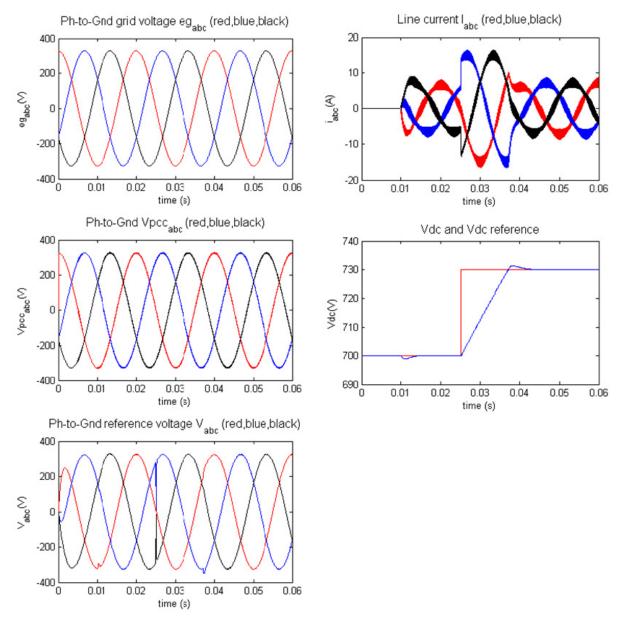

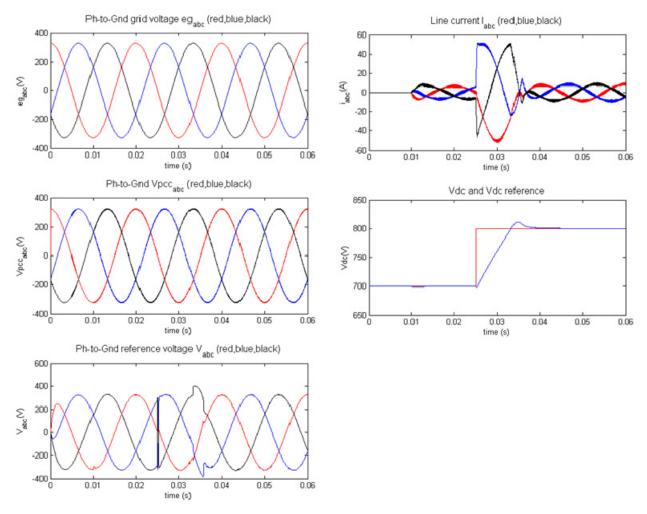

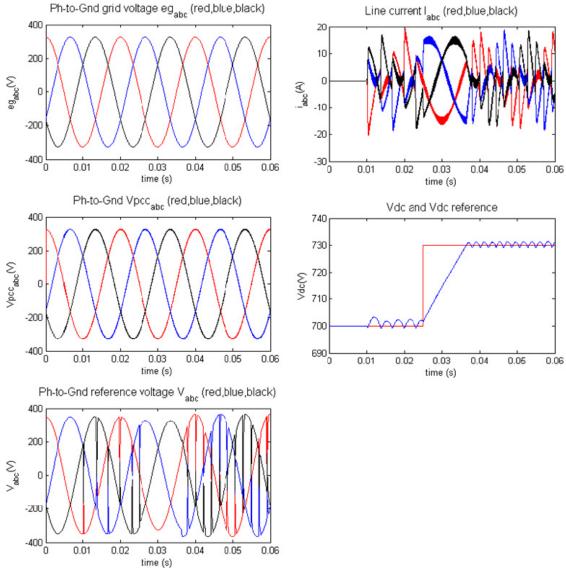

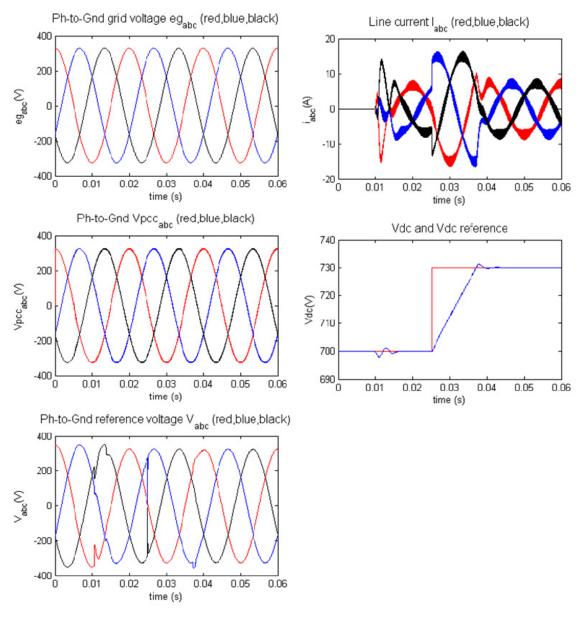

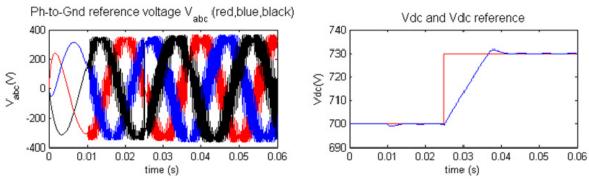

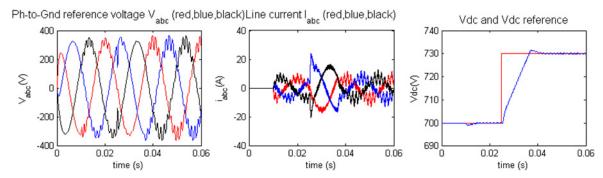

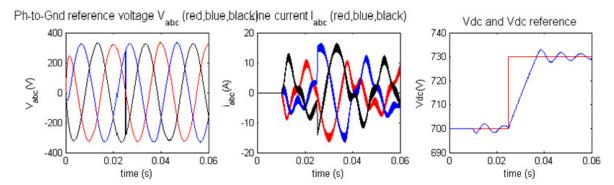

|                              | 3.9.3                                                                                                                                         | Simulation results                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                          |

| VOLTAG                       | E ORIENTED                                                                                                                                    | CONTROL – IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                | 63                                                                                                          |

| <i>1</i> 1                   | Block diagr                                                                                                                                   | ram                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                          |

|                              | Principle                                                                                                                                     | ıaııı                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                          |

|                              | •                                                                                                                                             | nodel modification                                                                                                                                                                                                                                                                                                                                      | 64                                                                                                          |

| _                            |                                                                                                                                               | n experiment                                                                                                                                                                                                                                                                                                                                            | 67                                                                                                          |

|                              | · ·                                                                                                                                           | ·                                                                                                                                                                                                                                                                                                                                                       |                                                                                                             |

| CONCLU                       | ISIONS AND                                                                                                                                    | FUTURE WORK                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                          |

| EFERENCE                     | :S                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                         | <b>7</b> 1                                                                                                  |

|                              |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                             |

| <u>PPENDICE</u>              | <u>:S</u>                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                         | 74                                                                                                          |

| <b>A.</b> 1                  | Three-phase                                                                                                                                   | system – Coordinate transformations                                                                                                                                                                                                                                                                                                                     | 74                                                                                                          |

|                              | A.1 Vo                                                                                                                                        | oltage and current definition                                                                                                                                                                                                                                                                                                                           | 74                                                                                                          |

|                              | A.2 Eq                                                                                                                                        | quivalent two-phase system, $lphaeta$ -transformation (Clarke)                                                                                                                                                                                                                                                                                          | 74                                                                                                          |

|                              | A.3 Sv                                                                                                                                        | nchronous coordinate, dq-transformation (Park)                                                                                                                                                                                                                                                                                                          |                                                                                                             |

|                              | ,                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                                          |

|                              | A.4 Sir                                                                                                                                       | mulation                                                                                                                                                                                                                                                                                                                                                |                                                                                                             |

|                              | A.4 Sir<br>A.5 Im                                                                                                                             | npedance in synchronous coordinates                                                                                                                                                                                                                                                                                                                     | 76<br>77                                                                                                    |

| В. \                         | A.4 Sir<br>A.5 Im<br>oltage and                                                                                                               | npedance in synchronous coordinates current control, continuous simulation                                                                                                                                                                                                                                                                              | 75<br>76<br>77<br><b>7</b> 9                                                                                |

| В. \                         | A.4 Sir<br>A.5 Im<br><b>/oltage and</b><br>B.1 Sir                                                                                            | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram                                                                                                                                                                                                                               | 76<br>77<br><b>79</b><br>79                                                                                 |

| В. \                         | A.4 Sir<br>A.5 Im<br><b>/oltage and</b><br>B.1 Sir<br>B.2 Co                                                                                  | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wi                                                                                                                                                            | 76<br>77<br><b>79</b><br>79<br>ndup, active                                                                 |

|                              | A.4 Sir<br>A.5 Im<br><b>/oltage and</b><br>B.1 Sir<br>B.2 Co<br>dampi                                                                         | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wi                                                                                                                                                            | 76<br><b>79</b><br>79<br>79<br>ndup, active<br>80                                                           |

| С. [                         | A.4 Sir<br>A.5 Im<br><b>/oltage and</b><br>B.1 Sir<br>B.2 Co<br>dampi<br><b>Digital simul</b> a                                               | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wing  ation                                                                                                                                                   | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b>                                              |

| C. E<br>D. \                 | A.4 Sir<br>A.5 Im<br>/oltage and d<br>B.1 Sir<br>B.2 Co<br>dampi<br>Digital simula<br>/oltage and                                             | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wing  ation  current control, discrete time simulation                                                                                                        | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b>                                              |

| C. E<br>D. \                 | A.4 Sir<br>A.5 Im<br>/oltage and<br>B.1 Sir<br>B.2 Co<br>dampi<br>Digital simula<br>/oltage and<br>stability anal                             | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-win  ing  ation  current control, discrete time simulation  lysis cont.                                                                                       | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b><br><b>82</b>                                 |

| C. E<br>D. \<br>E. S         | A.4 Sir<br>A.5 Im<br>/oltage and of<br>B.1 Sir<br>B.2 Co<br>dampi<br>digital simula<br>/oltage and<br>Stability anal<br>E.1 Sir               | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wing  ation  current control, discrete time simulation  lysis cont.  mulations                                                                                | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b><br><b>82</b><br><b>83</b>                    |

| C. E<br>D. \<br>E. S         | A.4 Sir<br>A.5 Im<br>/oltage and<br>B.1 Sir<br>B.2 Co<br>dampi<br>Digital simula<br>/oltage and<br>Stability anal<br>E.1 Sir<br>Grid connect  | npedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-win  ing  ation  current control, discrete time simulation  lysis cont.  mulations  ted converter simulation cont.                                            | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b><br><b>82</b><br><b>83</b><br>91              |

| C. E<br>D. \<br>E. S         | A.4 Sir<br>A.5 Im<br>/oltage and december 1 Sir<br>B.2 Condampi<br>Digital simular<br>/oltage and Stability anal<br>E.1 Sir<br>Grid connected | repedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  continuous voltage controller, simulation with saturation, anti-wing  ation  current control, discrete time simulation  lysis cont.  mulations  ted converter simulation cont.  ata and simulations                         | 76<br>77<br><b>79</b><br>79<br>ndup, active<br>80<br><b>81</b><br><b>82</b><br><b>83</b><br><b>91</b><br>91 |

| C. E<br>D. V<br>E. S<br>F. G | A.4 Sir<br>A.5 Im<br>/oltage and december 1 Sir<br>B.2 Condampi<br>Digital simular<br>/oltage and Stability anal<br>E.1 Sir<br>Grid connected | repedance in synchronous coordinates  current control, continuous simulation  mulink current control tests – Block diagram  ontinuous voltage controller, simulation with saturation, anti-wing  ation  current control, discrete time simulation  lysis cont.  mulations  ded converter simulation cont.  ata and simulations  atlab Script (Vdc Step) | 70<br>71<br>79<br>79<br>ndup, active<br>80<br>83<br>83<br>83<br>83                                          |

## 1 Introduction and scope

#### **PHD PROJECT**

The master thesis is part of a PHD project titled "Integrated charger for plug-in Hybrid Electric Vehicles".

The PHD project is funded by the Swedish Hybrid Vehicle Centre (SHC<sup>1</sup>) and is doing by the PHD student Saeid Haghbin under supervision of Associate Professor Ola Carlson. Moreover, Assistant Professor Sonja Lundmark is the project co-supervisor.

## The scope of the PhD project is:

- Investigating and evaluating existing plug-in HEV's in general and especially the charging systems. This collection of available information also includes listing all as well as the most interesting parameters of the charger, i.e. speed of charging, power rating, cost, volume and weight, number of phases, voltage levels, ease of charging and availability of charging places, limitations on power electronic components, power factor, harmonic distortion, monitoring equipment, standards, and persons safety. The study should involve battery knowledge, so that the charger could be fully adapted to the battery, giving a long battery life length.

- Suggest and evaluate possible integrated chargers, meaning integration of the charger and the available drive system used for propulsion of the vehicle.

- Prototype building in cooperation with the whole group (including industry). One prototype coordinator from industry administrates the task. The task also incorporates preparations for lab testing.

#### **MASTER THESIS SCOPE**

The thesis is part on the sub project "On Board Integrated Charging". The main goal is to design, simulate and implement a 3-phase boost battery charger with power factor correction.

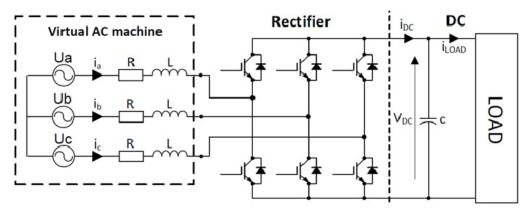

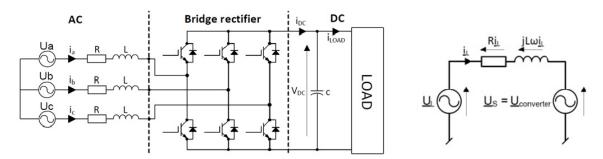

Figure 1.1: Rectifier schematic with AC machine

The Figure 1.1 represent our system. The first idea was to use an AC motor on the AC-side. Some data are given is Table 1.1.

<sup>&</sup>lt;sup>1</sup> SHC is composed with three different partners: three universities with Lund Institute of Technology (LTH), Royal Institute of Technology (KTH) and Chalmers University of Technology (CTH), The Swedish Energy Agency (Energimyndigheten) and automotive industry with AB Volvo, Volvo Car Corporation, Saab Automobile AB, GM Powertrain Sweden AB, Scania CV AB, BAE Systems Hägglunds AB.

|                                                     | - 3-phase                                                      |

|-----------------------------------------------------|----------------------------------------------------------------|

| Power source                                        | - 50Hz                                                         |

|                                                     | - PMSM 115V±20% phase voltage                                  |

| Power Level                                         | - 15kW                                                         |

| BATTERY VOLTAGE - 320-400VDC (nominal value 350VDC) |                                                                |

|                                                     | - Motor (KTH development)                                      |

|                                                     | - IGBT Rectifier                                               |

|                                                     | - Battery                                                      |

| MATERIAL                                            | - dSpace system                                                |

|                                                     | - Hardware (in development)                                    |

|                                                     | - Piece of software to develop for implementation (probably C) |

|                                                     | - Sensors (full access I/V/Speed)                              |

**Table 1.1** : Scope data

## At the beginning of thesis, a first plan had been established.

- 1) Literature review (how the system work/find literature resources)

- 2) Topology selection (VFOC is preferred method regarding to this specific application)

- 3) System design (inductance value, switching frequency, control design)

- 4) Simulation with Matlab/Simulink

- 5) Addition of PMSM to the model and using the leakage inductance of the machine as energy storage device (Re-design/Re-simulation)

- 6) Implementation

- a. dSpace system

- b. Software development

- c. Hardware test (in development)

- 7) Testing and debugging / Report

Nevertheless, after a couple of weeks we decided to simplify the system to keep a grid connected rectifier and try to implement it in the laboratory to test the controller.

The main goal of the thesis is to develop and test the control algorithm of the converter.

\* \*

We will start this thesis with an overview of three-phase controlled rectifiers (chapter 2), with steady state operation, modeling, limitations. Then, the overview will focus on control strategies, and finally, a Pulse Width Modulation (PWM) will be describe.

Chapter 3 will be the main part of the report with Voltage Oriented Control design and simulation. We will see the current and voltage controller, stability analysis, Phase Locked Loop (PLL), and finally a simulation of grid connected converter.

The last part chapter 4 will give the main guidelines for implementation of the controller using dSpace system.

## 2 THREE PHASE CONTROLLED RECTIFIERS

## 2.1 Introduction

In the following part, we will see some topologies for 3-phase rectifiers. But we can start to explain why those topologies appeared. The high harmonic content and a low power factor cause some problems in power distribution system. New standards have been introduced by governments or organizations to limit the harmonic content of the current drawn from the power line by rectifiers. Consequently, new topologies have been deployed for rectification applications [9].

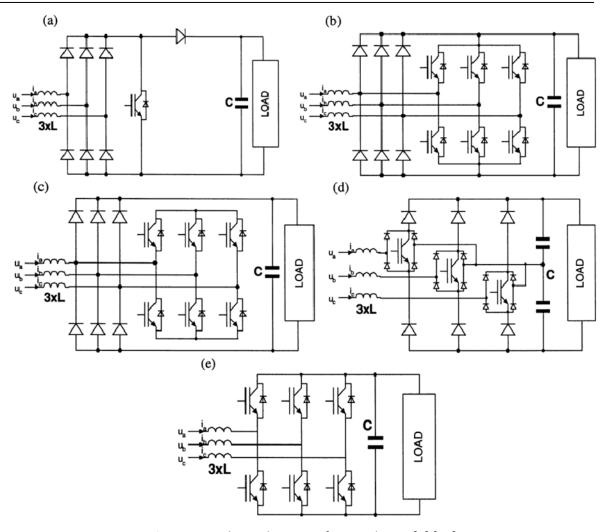

We can introduced five topologies (Figure 2.1).

**The figure a)** present a simple solution of Boost converter. The main drawback of this solution is stress on the components and low frequency distortion of the input current.

**The topologies b) and c)** use PWM rectifier modules with a very low current rating (20-25% level of RMS current comparable with e) topology). Hence they have a low cost potential and provide only the possibility of regenerative braking mode b) or active filtering c).

**Figure d)** presents a converter called a Vienna rectifier. The main advantage is low switch voltage, but non-typical switches are required.

**Figure e)** presents the most popular topology. This universal topology has the advantage of using a low-cost three-phase module with a bidirectional energy flow capability, and it can also provide a unity power factor (UPF). However, its disadvantages are a high per-unit current rating, poor immunity to shoot-through faults, and high switching losses [9].

Topologies are compared in a table (see Table 2.1). A diode rectifier is also included to the table for comparison.

**Figure 2.1**: Three-phase rectifier topologies [9] [13]

| FEATURE<br>TOPOLOGY | REGULATION OF DC OUTPUT VOLTAGE | LOW HARMONIC DISTORSION OF LINE CURRENT | NEAR SINUSOIDAL<br>CURRENT<br>WAVEFORMS | POWER FACTOR<br>CORRECTION | BIDIRECTIONAL<br>POWER FLOW | REMARKS |

|---------------------|---------------------------------|-----------------------------------------|-----------------------------------------|----------------------------|-----------------------------|---------|

| Diode rec.          | _                               | _                                       | _                                       | _                          | _                           |         |

| Rec. (a)            | +                               | _                                       | _                                       | +                          | _                           |         |

| Rec. (b)            | _                               | _                                       | _                                       | _                          | +                           |         |

| Rec. (c)            | _                               | +                                       | +                                       | +                          | _                           | UPF     |

| Rec. (d)            | +                               | +                                       | +                                       | +                          | _                           | UPF     |

| Rec. (e)            | +                               | +                                       | +                                       | +                          | +                           | UPF     |

Table 2.1 : Three-phase rectifier topologies, performance comparison [9] [13]

## 2.2 Universal bridge topology

## 2.2.1 Steady state operation

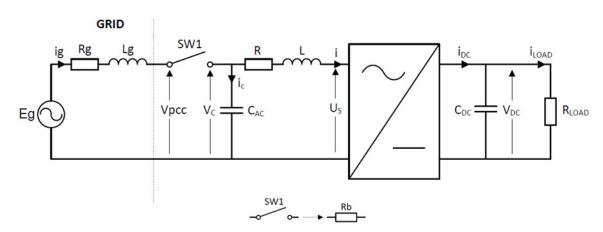

Figure 2.2: Rectifier schematics [9]

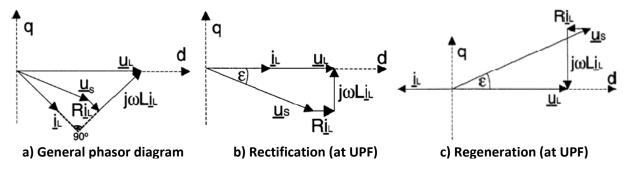

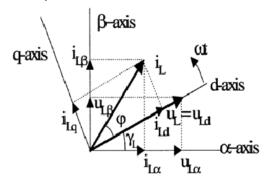

Figure 2.2 shows basic diagram of the three-phase boost converter.  $u_L$  is the line voltage and  $u_S$  is the bridge converter voltage controllable from de the dc-side. We can draw a general phasor diagram and diagrams for both rectification and regeneration operation at unity power factor (UPF).

Figure 2.3: Phasor diagrams [9]

The line current  $i_L$  is controlled by the voltage drop across the inductance L interconnecting the two voltage sources (line and converter).

When we control the phase angle  $\varepsilon$  and the amplitude of converter voltage  $u_s$ , we control indirectly the phase and amplitude of the line current. In this way, the average value and sign of the dc current is subject to control that is proportional to the active power conducted through the converter. The reactive power can be controlled independently with a shift of the fundamental harmonic current  $I_L$  with respect to voltage  $U_L$  [9].

<u>Remark</u>: Inductors connected between the line and the rectifier input bring a current source character of the input circuit and provide the boost feature of the converter [9].

## 2.2.2 Mathematical model

## **DESCRIPTION OF INPUT VOLTAGE AND CURRENT**

The three-phase line voltage and current are

$$u_{a} = E_{m} \cos(\omega t)$$

$$u_{b} = E_{m} \cos\left(\omega t - \frac{2\pi}{3}\right)$$

$$u_{c} = E_{m} \cos\left(\omega t - \frac{4\pi}{3}\right)$$

(2.1)

$$i_{a} = I_{m} \cos(\omega t + \varphi)$$

$$i_{b} = I_{m} \cos\left(\omega t + \varphi - \frac{2\pi}{3}\right)$$

$$i_{c} = I_{m} \cos\left(\omega t + \varphi - \frac{4\pi}{3}\right)$$

(2.2)

and since there is no neutral connection, we obtain

$$i_a + i_b + i_c = 0. (2.3)$$

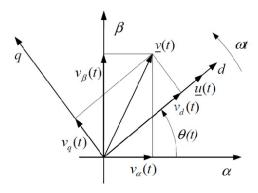

A three-phase system can be described with only two components  $\alpha$  and  $\beta$  (real and imaginary respectively). Furthermore, we call a **space vector** the quantity ([4] [12])

$$v^{s}(t) = v_{\alpha}(t) + jv_{\beta}(t) = \frac{2}{3}K\left(v_{a}(t) + v_{b}(t)e^{j\frac{2\pi}{3}} + v_{c}(t)e^{j\frac{4\pi}{3}}\right). \tag{2.4}$$

where K is a scaling constant (amplitude invariant K = 1, RMS-invariant  $K = 1/\sqrt{2}$ , power invariant  $K = \sqrt{3/2}$ ) – Refer to APPENDIX A for details).

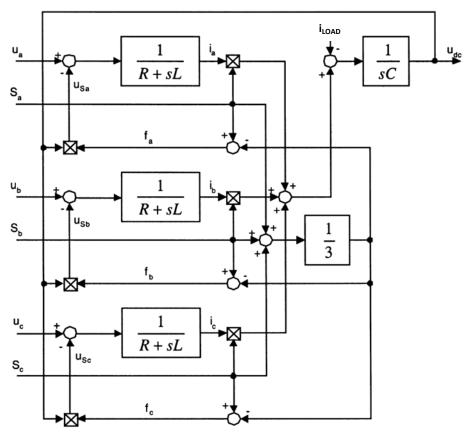

## RECTIFIER ABC-MODEL [9]

$$u_{Sab} = (Sa - Sb) u_{dc}$$

$$u_{Sbc} = (Sb - Sc) u_{dc}$$

$$u_{Sca} = (Sc - Sa) u_{dc}$$

(2.5)

with Si the switching function defined by :  $Si = \begin{cases} 1 & \text{upper switch ON} \\ 0 & \text{bottom switch ON} \end{cases}$  with phase i = a , b , c.

$$u_{Sa} = f_a \cdot u_{dc}$$

$$u_{Sb} = f_b \cdot u_{dc}$$

$$u_{Sc} = f_c \cdot u_{dc}$$

(2.6)

$$f_{a} = S_{a} - S^{*} = S_{a} - \frac{1}{3}(S_{a} + S_{b} + S_{c}) = \frac{2S_{a} - (S_{b} + S_{c})}{3}$$

$$f_{b} = \frac{2S_{b} - (S_{a} + S_{c})}{3}$$

$$f_{c} = \frac{2S_{c} - (S_{a} + S_{b})}{3}$$

$$(f_{abc} \text{ are } 0, \pm 1/3 \text{ or } \pm 2/3).$$

$$(2.7)$$

The rectifier in defined by four equations, one for each phase (voltage) and one for the currents (dc-link).

$$\begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} = R \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} u_{Sa} \\ u_{Sb} \\ u_{Sc} \end{bmatrix}$$

(2.8)

$$C\frac{du_{dc}}{dt} = S_a i_a + S_b i_b + S_c i_c - i_{load}$$

(2.9)

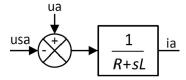

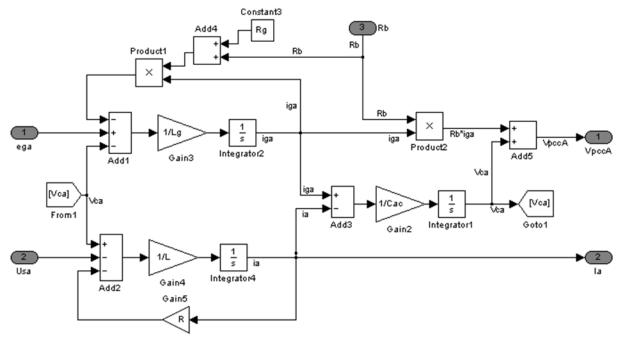

The combination of the previous equations can be represented as a block diagram.

Figure 2.4: Rectifier model [9]

## RECTIFIER $\alpha \beta$ -EQUATIONS

We define the amplitude invariant Clarke transformation (see APPENDIX A) with ([4] [12] )

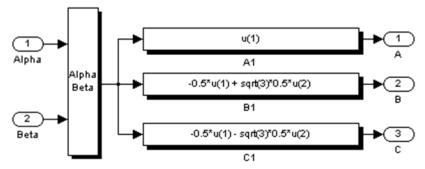

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & -\frac{1}{3} & -\frac{1}{3} \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & -\frac{1}{3} & -\frac{1}{3} \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}

\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}$$

(2.10)

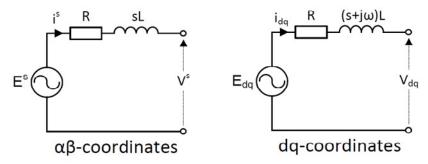

Then, applying this transformation we can find the voltage equations in  $\alpha\beta$ -coordinates

$$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} u_{S\alpha} \\ u_{S\beta} \end{bmatrix}$$

$$C \frac{du_{dc}}{dt} = \frac{3}{2} \left( S_{\alpha} i_{\alpha} + S_{\beta} i_{\beta} \right) - i_{load}.$$

(2.12)

$$C\frac{du_{dc}}{dt} = \frac{3}{2} \left( S_{\alpha} i_{\alpha} + S_{\beta} i_{\beta} \right) - i_{load}. \tag{2.13}$$

## RECTIFIER dq-EQUATIONS

Now, we need to apply the Park transformation (see APPENDIX A and [4] [12] ) which is

$$v_{dq} = v^s e^{-j\theta} (2.14)$$

where  $v^s$  is a space vector ( $v^s = v_\alpha + jv_\beta$ ). We get

$$u^{s} = Ri^{s} + L\frac{di^{s}}{dt} + u_{s}^{s} \tag{2.15}$$

$$\Leftrightarrow u_{dq}e^{j\theta} = Ri_{dq}e^{j\theta} + L\left(e^{j\theta}\left(j\omega i_{dq} + \frac{di_{dq}}{dt}\right)\right) + e^{j\theta}u_{Sdq}$$

$$\Leftrightarrow u_{dq} = Ri_{dq} + L\frac{di_{dq}}{dt} + jL\omega i_{dq} + u_{Sdq}$$

(2.16)

And finally, with separation of Real and Imaginary part we obtain

$$u_d = Ri_d + L\frac{di_d}{dt} - \omega Li_q + u_{Sd}$$

(2.17)

$$u_q = Ri_q + L\frac{di_q}{dt} + \omega Li_d + u_{Sq}$$

(2.18)

$$C\frac{du_{dc}}{dt} = \frac{3}{2}\left(S_d i_d + S_q i_q\right) - i_{load} \tag{2.19}$$

## **INSTANTANEOUS POWER [4]**

From the well known relation  $P=Re\{\underline{V}\ \underline{I}^*\}$  for single phase rms-value-scaled phasors  $\underline{V}$  and  $\underline{I}$  ("\*" indicates complex conjugate), we know that instantaneous power for three-phase system will be proportional to

$$Re\{v^{s}(i^{s})^{*}\} = Re\{v^{dq}(i^{dq})^{*}\}$$

(2.20)

Note that the formula is independent of the coordinate system.

From the space vector definition we get (the time argument "(t)" is removed for simplicity)

$$v^{s}(i^{s})^{*} = \left(\frac{2}{3}K\right)^{2} \left(v_{a} + v_{b}e^{j\frac{2\pi}{3}} + v_{c}e^{j\frac{4\pi}{3}}\right) \left(i_{a} + i_{b}e^{j\frac{2\pi}{3}} + i_{c}e^{j\frac{4\pi}{3}}\right)^{*}$$

$$= \left(\frac{2}{3}K\right)^{2} \left[v_{a}i_{a} + v_{b}i_{b} + v_{c}i_{c} + j\frac{1}{\sqrt{3}}\left(v_{a}(i_{c} - i_{b}) + v_{b}(i_{a} - i_{c}) + v_{c}(i_{b} - i_{a})\right)\right]$$

And finally, the Real part gives us the active power

$$P = \frac{3}{2K^2} Re\{v^s (i^s)^*\} = \frac{3}{2K^2} Re\{v^{dq} (i^{dq})^*\} = v_a i_a + v_b i_b + v_c i_c.$$

(2.21)

And with Imaginary part we obtain the reactive power

$$Q = \frac{3}{2K^2} Im(v^s (i^s)^*) = \frac{3}{2K^2} Im\{v^{dq} (i^{dq})^*\}$$

$$= \frac{1}{\sqrt{3}} [v_a(i_c - i_b) + v_b(i_a - i_c) + v_c(i_b - i_a)].$$

(2.22)

For ideal, positive sequence space vectors (voltage is reference)

$$v^s = KE_m e^{j\omega t}$$

and  $i^s = KI_m e^{j\omega t + \varphi}$

where  $E_m$  and  $I_m$  are amplitude, the active power is given by

$$P = \frac{3}{2K^2} Re\{v^s (i^s)^*\} = \frac{3}{2K^2} Re\{v^{dq} (i^{dq})^*\} = \frac{3}{2} E_m I_m cos \varphi = 3VI cos \varphi$$

(2.23)

Where V and I are rms-values. This previous relation will be use in the DC-link voltage controller design.

## 2.2.3 Limitations

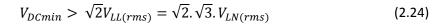

#### **MINIMUM DC-LINK VOLTAGE**

For proper operation of the rectifier, a minimum dc-link voltage is needed to obtain undistorted current waveforms. To have a full control of the rectifier, its six diodes must be polarized negatively at all value of ac-voltage supply. To keep the diodes blocked, we need to ensure a dc-link voltage higher than the peak dc-voltage generated by the diodes alone.

Theoretically for diode rectifier, the maximum dc output voltage is the peak value of line-to-line RMS voltage [9] .

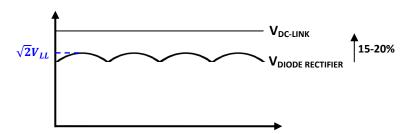

**Figure 2.5**: *DC-link voltage condition*

It will be better to select a DC-link voltage about 15-20% more than  $\sqrt{2}V_{LL}$ .

**IMPORTANT**: The previous voltage  $V_{LL(rms)}$  correspond to the converter voltage (Us). There is no line impedance taking in account here.

Nevertheless, if there is no line impedance (R =  $0\Omega$  , L=0H) we can continue to write the equation (2.24) according to the amplitude of supply voltage Em :

$$V_{DCmin} > \sqrt{2}.\sqrt{3}.V_{LN(rms)} = \sqrt{3} E_m.$$

(2.25)

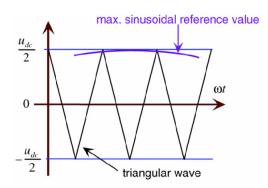

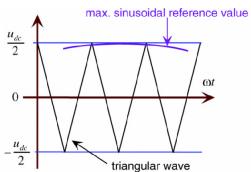

**ATTENTION:** This is a true definition but doesn't apply in all situation [9]. The DC-link voltage depends on the PWM method. In our case, we will use a sinusoidal PWM. In this case the maximum reference voltage is Vdc/2 (Figure 2.6 [23]).

Figure 2.6: Maximum sinusoidal reference voltage (converter voltage Us) for sinusoidal PWM [23]

Finally, our minimum DC-link voltage will be

$$V_{LN(peak)} = \frac{V_{DC}}{2}$$

$$\frac{V_{LL(rms)}}{\sqrt{3}} \sqrt{2} = \frac{V_{DC}}{2}$$

(2.26)

$$V_{DCmin} > 2 V_{LN(peak)} = \frac{2\sqrt{2}}{\sqrt{3}} V_{LL(rms)} = 1.663 V_{LL(rms)}$$

(2.27)

## MINIMUM DC-LINK VOLTAGE AND INDUCTANCE

The book [9] (chapter11 p434) defines a minimum DC-link voltage taking in account the line inductance value. The demonstration seems to be valid in our case for amplitude invariant (they assume a maximum converter voltage equal to  $\frac{2}{3}Vdc$  (i.e. radius of switching hexagon). It will be

$$\sqrt{\frac{3}{2}}Vdc$$

for power invariant). They define a DC-link voltage as

$$Vdc > \sqrt{3[E_m^2 + (\omega Lid)^2]}.$$

(2.28)

We can observe that R is neglected and if L = 0 (if there is no inductance voltage), we find again the equation (2.25) where  $V_{DCmin} > \sqrt{3}E_m$ .

From this equation we can get the maximum inductance value as

$$L < \frac{\sqrt{\frac{V_{DC}^2}{3} - E_m^2}}{\omega i d}.$$

(2.29)

A low inductance will give a high current ripple and will make the design more dependent on the line impedance (refer to "3.8 Grid modeling" and "3.9.3 Simulation results"). According to [9], a high value of inductance will give a low current ripple, but simultaneously reduce the operation range of the rectifier. The voltage drop across the inductance controls the current. This voltage drop is controlled by the voltage of the rectifier but its maximal value is limited by the dc-link voltage. Consequently, a high current (high power) through the inductance requires either a high dc-link voltage or a low inductance (low impedance).

## 2.3 Control strategies

## 2.3.1 Introduction

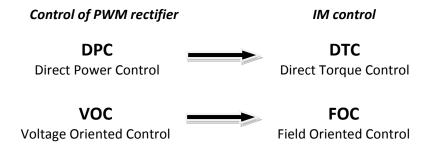

The control of PWM converter can be considered as a dual problem with vector control of an induction motor IM (see figure and table below).

**Figure 2.7**: PWM rectifier and IM control duality

| Control of PWM rectifier                              | IM control                      |

|-------------------------------------------------------|---------------------------------|

| Speed control loop of vector drive                    | dc-link voltage                 |

| Reference angle between stator current and rotor flux | Reference angle of line voltage |

**Table 2.2:** PWM rectifier and IM control duality [9]

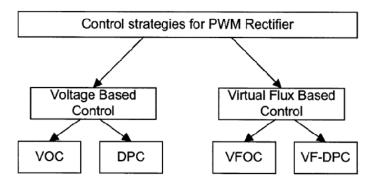

We can classify the PWM rectifier method in two categories : **voltage** based and **virtual flux** based control (See following Figure 2.8).

Figure 2.8 : Control strategies [9]

All these control strategies can achieve the same main goals, such as high power factor and near sinusoidal input current waveforms.

**The Voltage Oriented Control (VOC)** guarantees high dynamic and static performance via an internal current control loop. But the quality depends mainly on the current control strategy.

**The Direct Power Control (DPC)** is based on the instantaneous active and reactive power control loop. There are no internal current control loop and no PWM modulator block. The switching state are determined with a switching table based on the instantaneous errors between the commanded and estimated values of active and reactive power.

The Virtual Flux Based Control (VF-) correspond to a direct analogy of IM control.

## 2.3.2 <u>Direct Power Control and Virtual Flux Direct Power Control</u>

The DPC method is similar to Direct Torque Control (DTC) for induction motor. Instead of torque and stator flux the instantaneous active and reactive powers are controlled. The following figure shows the scheme of the DPC method.

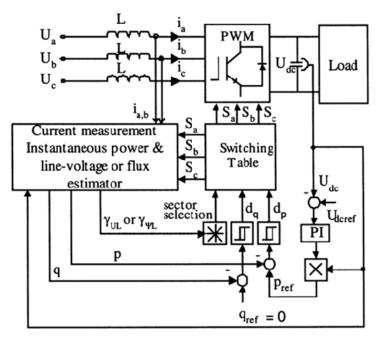

Figure 2.9: Block scheme (DPC, VF-DPC)[9]

The power estimation of DPC is based on the line voltage. An important disadvantages of the method id the need of current differentiation to estimate this power. Other relevant points can be found ([9]):

- Need high sample frequency because the estimated value are changing all the time.

- Need high inductance value because the switching frequency is not constant.

- A non-constant switching frequency means trouble to design an input filter.

- Calculation of power and voltage should be avoid during switching (errors).

The virtual flux method is an improvement of Voltage Oriented Control (VOC). The virtual flux is an integration of line voltage u<sub>L</sub>.

For the VF-DPC, we can summaries the following characteristics.

- No line voltage sensors required. Furthermore, a voltage sensor-less line power estimation is much less noisy due to natural low-pass behavior of the integrator.

- Simple and noise robust power estimation algorithm, easy to implement in a DSP.

- Lower sampling frequency (as conventional DPC).

- Sinusoidal line currents (low THD).

- No separate PWM voltage modulation block.

- No current regulation loops.

- Coordinate transformation and PI controllers not required.

- High dynamic, decoupled active and reactive power control.

- Power and voltage estimation gives the possibility to obtain instantaneous variables with all harmonic components, which has an influence for improvement of total power factor and efficiency.

- Easier calculations for p and q than voltage based method, no differentiation of line current.

The typical disadvantages of VF-DPC are:

Variable switching frequency.

Solution requires a fast microprocessor and A/D converters.

## 2.3.3 Voltage and Virtual Flux Oriented Control

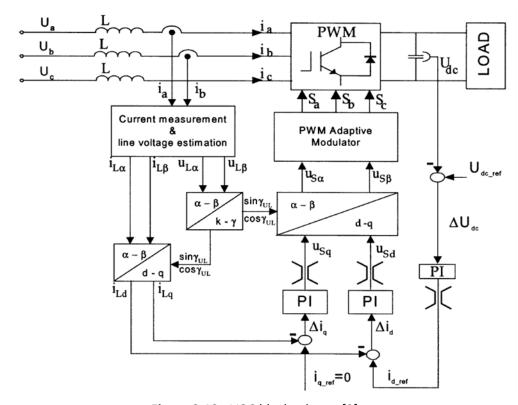

Figure 2.10: VOC block scheme [9]

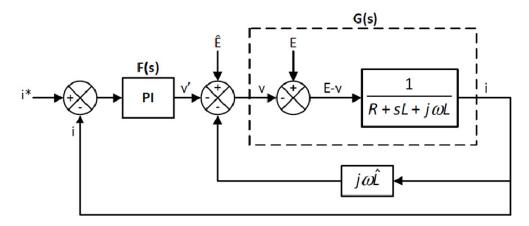

The Voltage Oriented Control (VOC) and Virtual Flux Oriented Control (VFOC) are close to Field Oriented Control for induction motor. The method is based on the transformation between stationary coordinates  $\alpha\beta$  and synchronous rotating coordinates dq. This strategy guarantees:

- Fast transient response

- High static performance via internal current control loop.

Consequently, the performance depends on the quality of the current control loop.

We can find several strategies that can be applied for current control. A widely used scheme for high performance current control is the *dq* synchronous controller, where the regulated current are DC quantities. This eliminates steady-state errors.

VOC and VFOC provide some advantages compared to DPC.

- Low sampling frequency for good performance (cheaper A/D converters and microcontroller)

- Fixed switching frequency (easier design of input filter)

Furthermore, VFOC provides improved rectifier control under non-ideal line voltage condition (because ac voltage sensorless operation is much less noisy thanks to the natural low-pass behavior of the integrator used in the flux estimator).

Both methods also have some *disadvantages*:

- Coupling occurs between active and reactive components and some decoupling solution is required.

- Coordinate transformation and PI controllers are required.

## 2.3.4 Comparison and discussion

The following table summarizes the main characteristics of the different control strategies.

| TECHNIQUE | ADVANTAGES                                                                                                                                                                                                                                                                                                                                                                                                                                | DISADVANTAGES                                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| voc       | <ul> <li>Fixed switching Freq. (easier design input filter)</li> <li>Advanced PWM strategies can be used</li> <li>Cheap A/D converters</li> </ul>                                                                                                                                                                                                                                                                                         | <ul> <li>Coordinate transformation and decoupling between active and reactive components is required</li> <li>Complex algorithm</li> <li>Input power factor lower than for DPC</li> </ul>                                                       |

| DPC       | <ul> <li>No separate PWM block</li> <li>No current regulation loop</li> <li>No coordinate transformation</li> <li>Good dynamics</li> <li>Simple algorithm</li> <li>Decoupled active and reactive power control</li> <li>Instantaneous variables with all harmonics components estimated (improve power factor and efficiency)</li> </ul>                                                                                                  | <ul> <li>High inductance and sample frequency needed</li> <li>Power and voltage estimation should be avoid at the moment of switching</li> <li>Variable switching frequency</li> <li>Fast microprocessor and A/D converters required</li> </ul> |

| VFOC      | <ul> <li>Fixed switching Freq. (easier design input filter)</li> <li>Advanced PWM strategies can be used</li> <li>Cheap A/D converters</li> </ul>                                                                                                                                                                                                                                                                                         | <ul> <li>Coordinate transformation and decoupling between active and reactive components is required</li> <li>Complex algorithm</li> <li>Input power factor lower than for VF-DPC</li> </ul>                                                    |

| VF-DPC    | <ul> <li>Simple and noise resistant power estimation algorithm, easy to implement in a DSP</li> <li>Lower sampling frequency than for DPC</li> <li>Low THD of line currents with distorted or unbalanced supply</li> <li>No separate PWM block</li> <li>No current regulation loop</li> <li>No coordinate transformation</li> <li>Good dynamics</li> <li>Simple algorithm</li> <li>Decoupled active and reactive power control</li> </ul> | ■ Variable switching frequency ■ Fast microprocessor and A/D converters required                                                                                                                                                                |

**Table 2.3 :** Control strategies comparison [9]

## **VOC vs. VFOC**

One of the only advantages of VFOC against VOC is that VFOC provides improved rectifier control under non-ideal line voltage condition (because ac voltage sensorless operation is much less noisy thanks to the natural low-pass behavior of the integrator used in the flux estimator).

#### **Switching Frequency**

A FIXED switching frequency is required in our project mainly because it means: easier design (input filter for eg.) and the sample frequency can be lower. Only VOC or VFOC can provide this feature.

#### **Power factor**

DPC has better power factor than VOC but has variable switching frequency. DPC also means complicated calculations for p and q (need differentiation of line current, risk of instability).

A good power factor can be achieved with VF-DPC and the method has lots of advantages but as we want a fixed switching frequency, VOC or VFOC should be chosen.

If the switching frequency can be variable, the VF-DPC strategy is obviously the best solution (but the cost can become a problem. The method need fast microprocessors and A/D converters).

## 2.4 Pulse Width Modulation

The Pulse Width Modulation used in our system, a sinusoidal PWM will be used.

## 2.4.1 Sinusoidal PWM

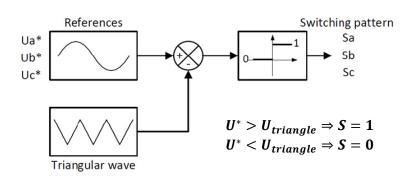

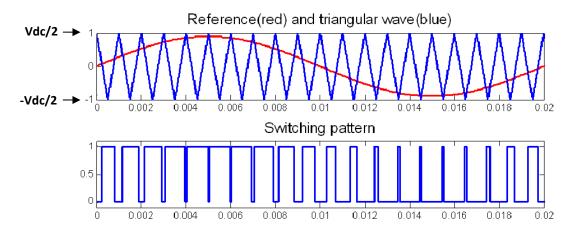

Sinusoidal modulation based on a triangular carrier signal. The idea is to compare three sinusoidal reference voltages Ua\*, **Ub\*** and **Uc\*** to this triangular wave. By comparison, the logical signals Sa, Sb and Sc, which define switching instants of power transistor, are generated. Operation with constant carrier signal concentrate voltage harmonics around switching frequency and multiple of switching frequency.

Figure 2.11: Sinusoidal PWM

Figure 2.12: Sinusoidal PWM basic waveforms

#### **○** Maximum sinusoidal reference voltage

Using a sinusoidal PWM, the maximum reference value is Vdc/2.

Figure 2.13: Maximum sinusoidal reference voltage (sinusoidal PWM) [23]

#### **○** Maximum slope

The slope of the triangular wave should be higher than the slope of the reference voltage. We can write

$$\frac{dU_{triangle}}{dt} > \frac{dU_{reference}}{dt} \tag{2.30}$$

## 2.4.2 Digital implementation

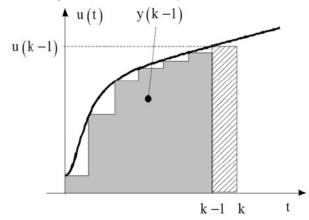

## Synchronous sampling [4]

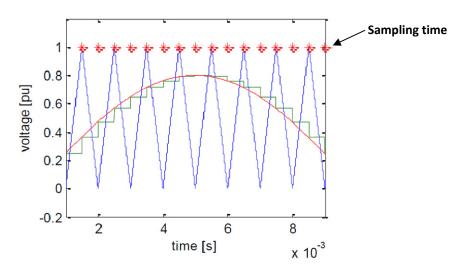

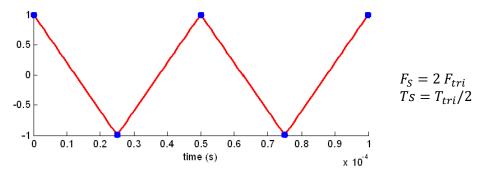

In a digital current control system, the current is sample with interval **Ts**. To avoid electromagnetic interference (EMI) due to ON/OFF switchings of the valves, it is useful to synchronize the sampling with converter switching. Current sampling are taken in between switchings. This coincide with the positive and negative peak values of the triangular waveform.

Using synchronous sampling, approximately the mean value of the current is obtained. Thus, not only EMI is avoided, but also the current ripple is reduced. This method can be effective enough to avoid low-pass filtering before sampling.

We will select the sample frequency as:

$$F_S = 2 F_{triangle \ wave} = 2 F_{SW}$$

(2.31) ( $F_{SW}$  is the switching frequency,  $F_{triangle \ wave} = F_{SW}$ )

**Figure 2.14**: Asymmetric PWM – Synchronous sampling illustration [23]

Two samples can be acquired over each switching period. According to [4] a fast sampling enables higher bandwidth of the current controller, then it's possible to reduce the sampling rate for example to the switching rate :  $F_S = F_{SW}$  (or less).

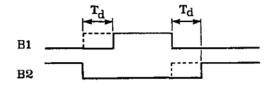

## 2.4.3 Dead time effect

When we speak about implementation of converter, we need to inject deadtime (delay) in PWM signals to avoid short circuit in DC-link (i.e. both transistor of one leg are conducting). The system becomes safer but, the performance are affected.

This is temporary a loss of control. For example in an inverter, the output voltage waveform deviates from that for which it is originally intended. Since this is repeated over and over for every switching operation, its detrimental effect may become significant in PWM inverters that operate in high switching frequency. This is known as the deadtime effect. During the delay time, both transistors of the leg cease to conduct. Another consequence of the deadtime effect is the appearance of undesirable harmonics ([31] [32]).

We can find several strategies for deadtime injection. An example is given below.

**Figure 2.15**: One leg with transistors B1 and B2 – On/Off states, deadtime Td [32]

## 3 VOLTAGE ORIENTED CONTROL - SIMULATION

## 3.1 Introduction – References chosen

As we explain in the previous section, Voltage Oriented Control (VOC) or Virtual Flux Oriented Control (VFOC) should be chosen. We decided to start with a VOC.

Before going further in the design and simulation of the controller, we need to precise some important references chosen in this report.

#### **3-PHASE SYSTEM DEFINITION**

$$u_a = E_m \cos(\omega t)$$

$$u_b = E_m \cos\left(\omega t - \frac{2\pi}{3}\right)$$

$$u_c = E_m \cos\left(\omega t - \frac{4\pi}{3}\right)$$

#### **COORDINATE TRANSFORMATION**

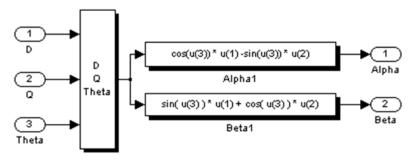

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & -\frac{1}{3} & -\frac{1}{3} \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} \text{ and } \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}$$

(2.10)(2.11)

$$\begin{bmatrix} d \\ q \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix} \text{ and } \begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \cos\theta & -\sin\theta \\ \sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} d \\ q \end{bmatrix}.$$

(3.1) (3.2)

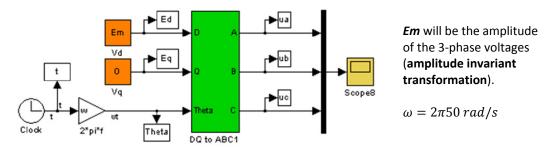

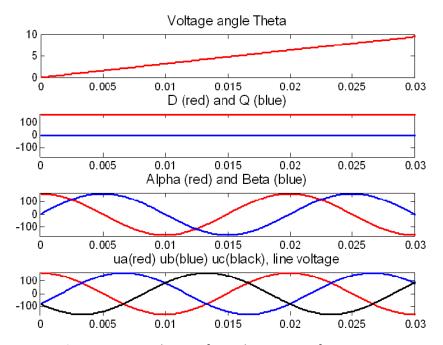

You can refer to APPENDIX A for details. We only use  $\underline{\mathsf{AMPLITUDE}\;\mathsf{INVARIANT}}$  in this thesis. Indeed, after transformation from ABC-to-dq coordinates, the d-components is equal to  $E_m$ , and the q-component equal to zero.

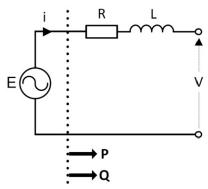

## **POWER, CURRENT DIRECTION**

We chose a reference as shown in the following schematic, the current is flowing from the grid to the rectifier.

Figure 3.1 Reference for I, P, Q

## 3.2 System block diagram

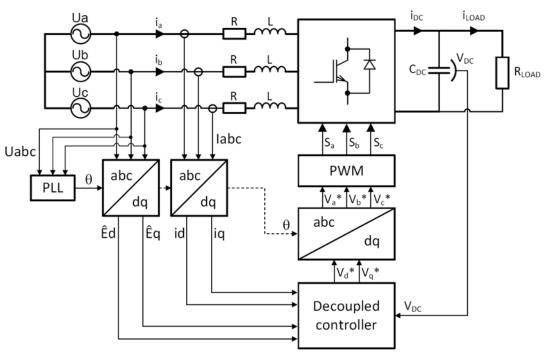

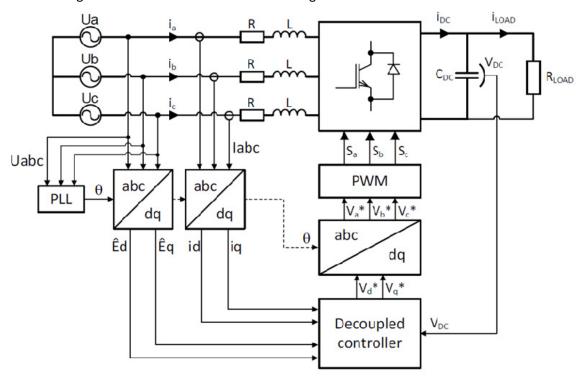

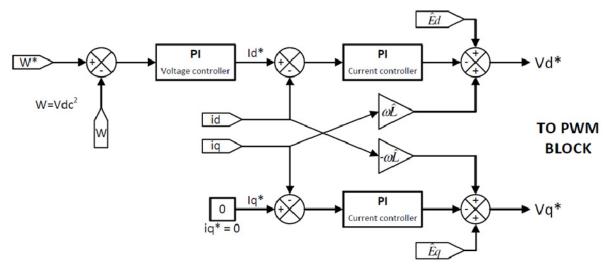

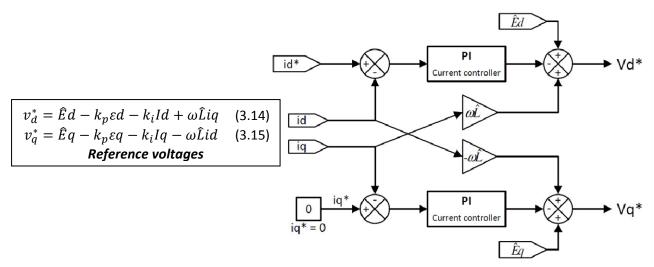

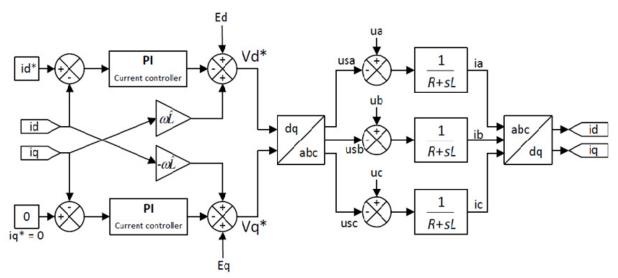

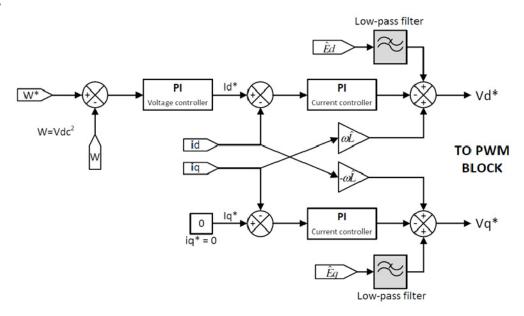

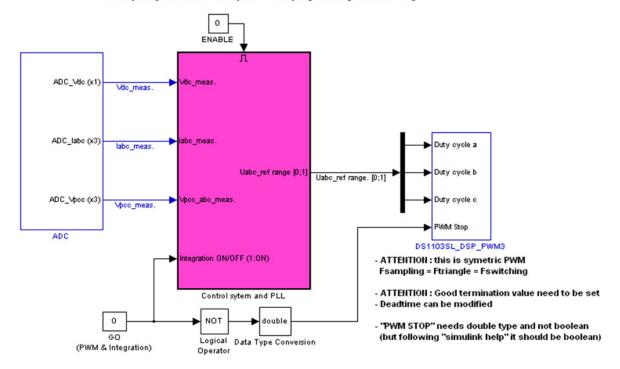

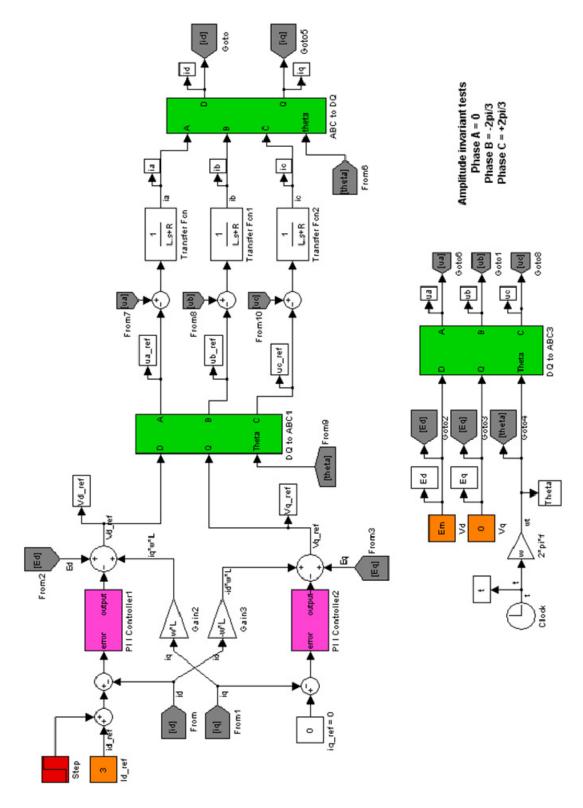

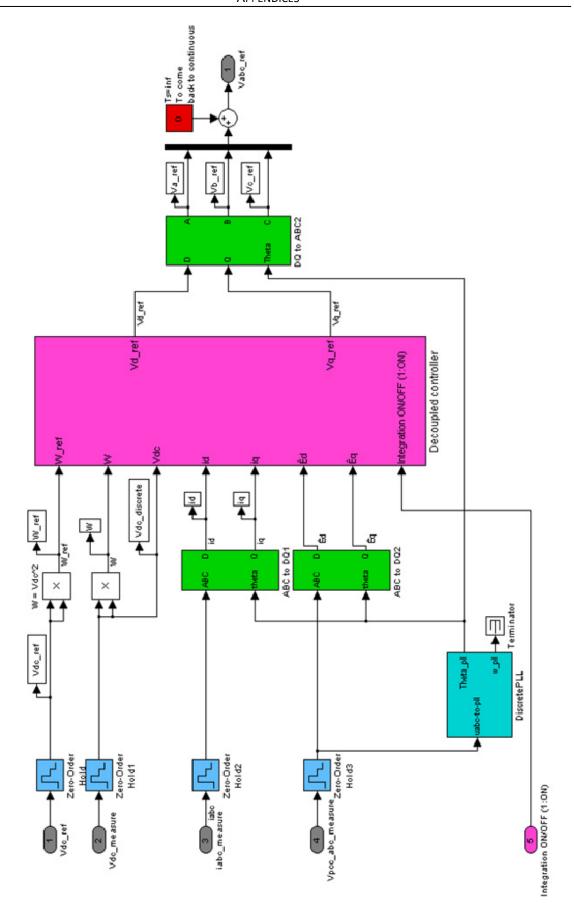

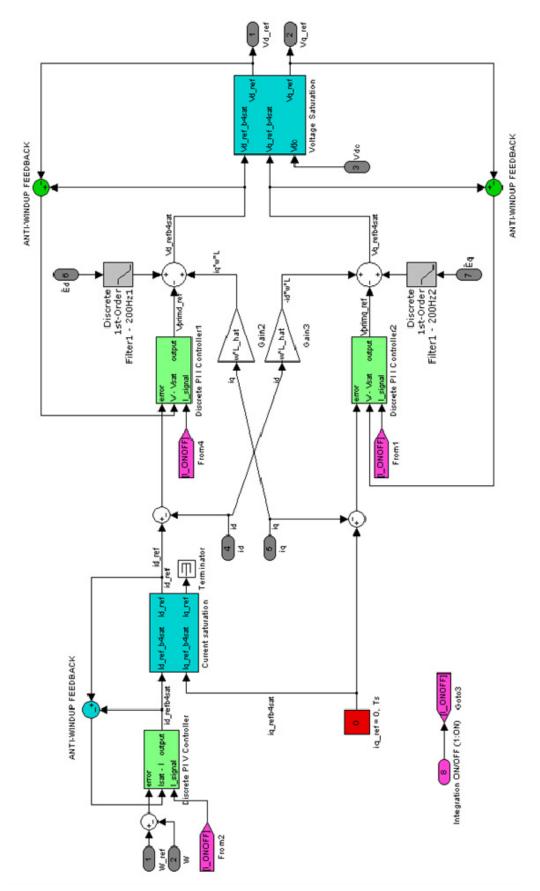

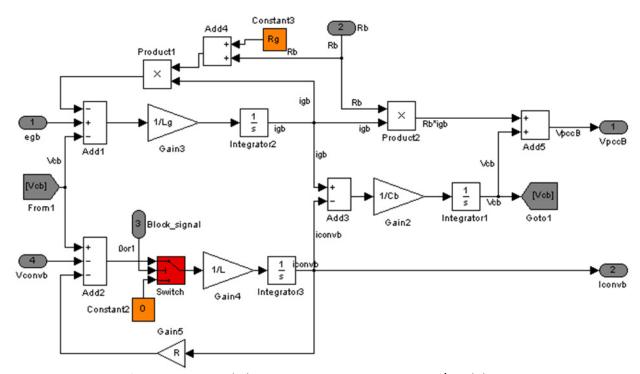

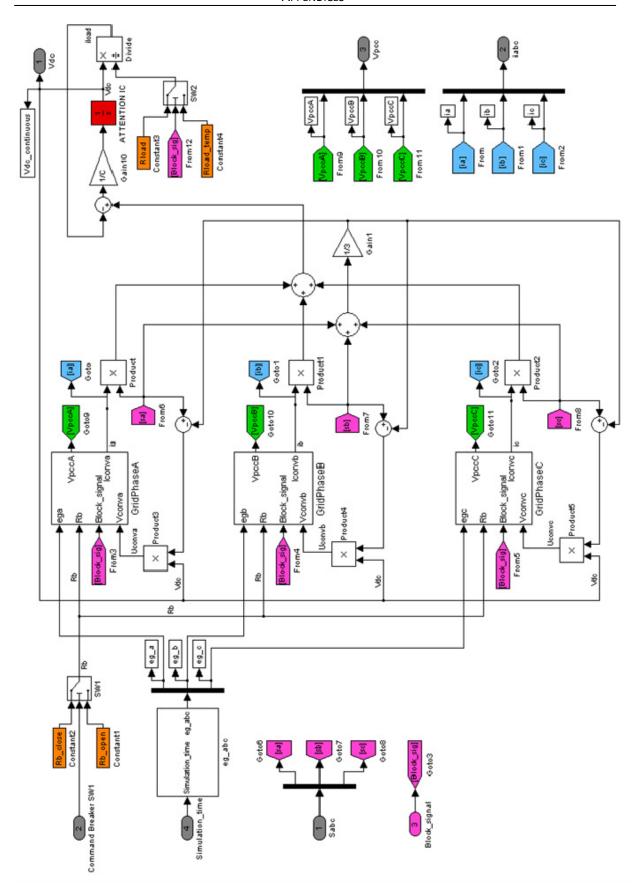

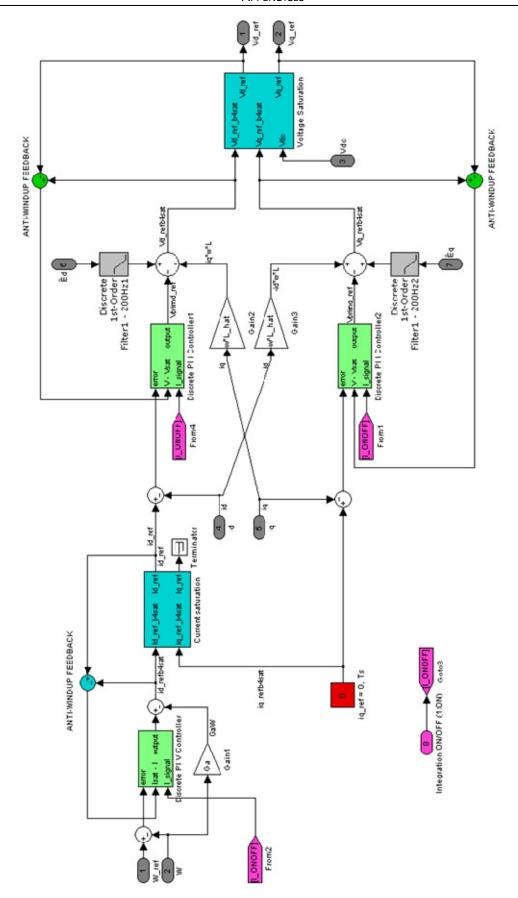

The voltage oriented control scheme is shown Figure 3.2.

**Figure 3.2**: System block diagram

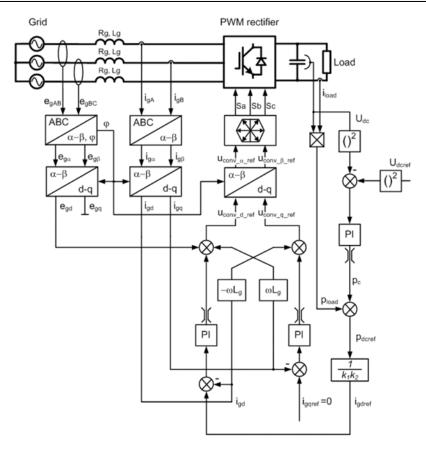

First of all, the line voltage Uabc need to feed the PLL (Phase Locked Loop, see "3.7 Phase Locked Loop (PLL)") and the voltage angle calculated is used for three-phase to dq-coordinate transformation of line current and voltage.

Secondly, the *dq*-coordinate values and the DC-link voltage value are used in a decoupled controller which will be described in the section "3.4 Current controller" and "3.5 DC-link voltage controller". Finally, the reference voltages created by the controller are sent to the PWM block (Pulse Width Modulation) to create the switching patterns *Sabc* (S = 1 means upper switch ON, lower switch OFF; S=0 means upper switch OFF, lower switch ON).

<u>Remark</u>: The reference voltage from the controller correspond to the converter voltage *Us* (see design of the current controller in section "3.4 Current controller").

The system will be simulated in Matlab/Simulink. According to the previous figure, we will have four main parts in the model: the PLL, a decoupled controller composed by a current and voltage controller, a PWM block, and a rectifier model (with grid impedance R and L included).

## 3.3 PWM Simulation

A description of the sinusoidal PWM implemented here is available in section "2.4 Pulse Width Modulation".

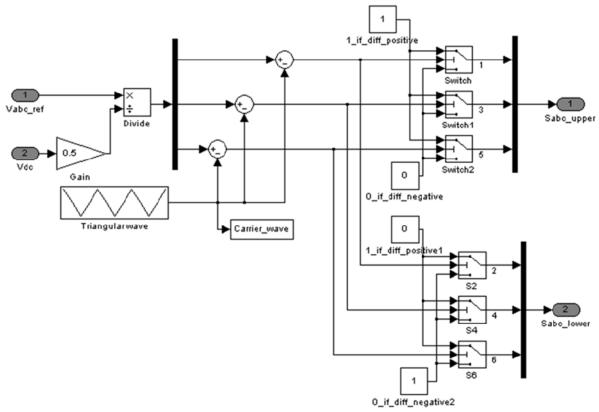

## 3.3.1 Simulink implementation of PWM

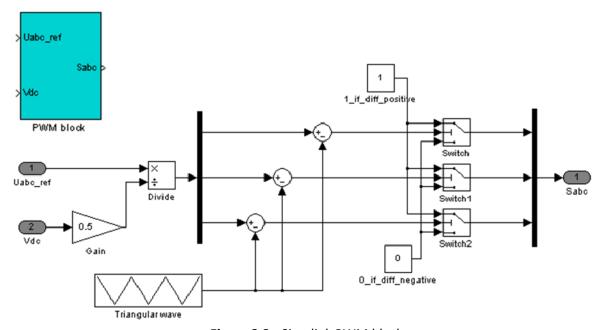

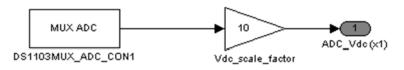

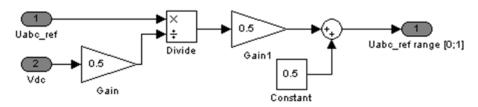

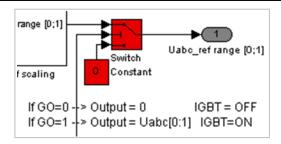

#### **⊃** PWM block using switch

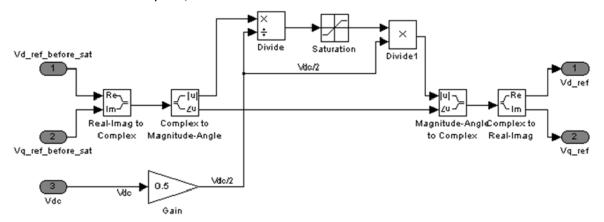

The amplitude of triangular wave should be Vdc/2. But Vdc is not constant in our case. We should first normalized the reference value by Vdc/2 and compare this value with a triangular wave with an amplitude of 1. The following figure show the Simulink block diagram.

Figure 3.3 : Simulink PWM block

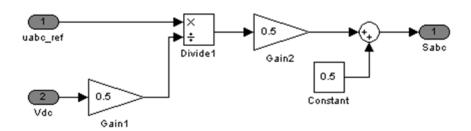

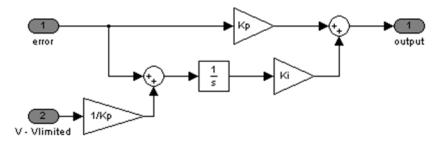

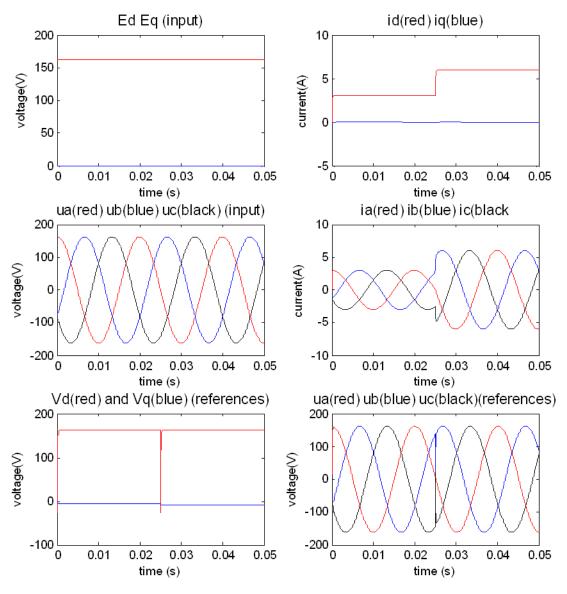

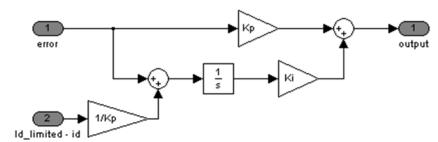

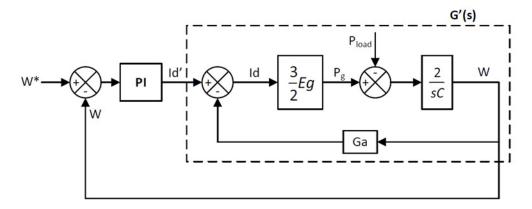

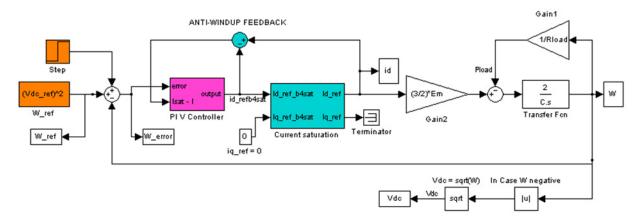

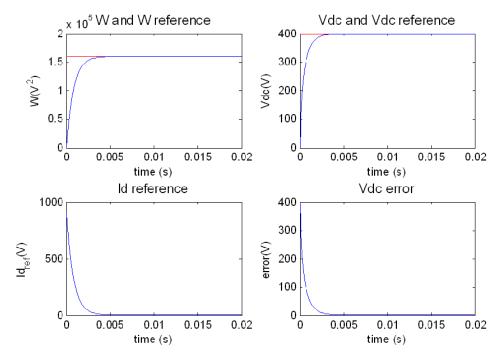

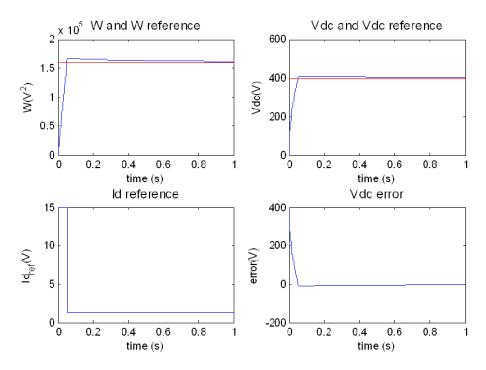

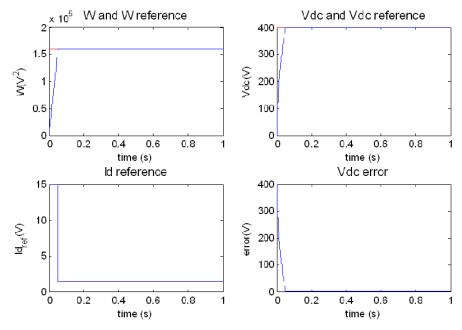

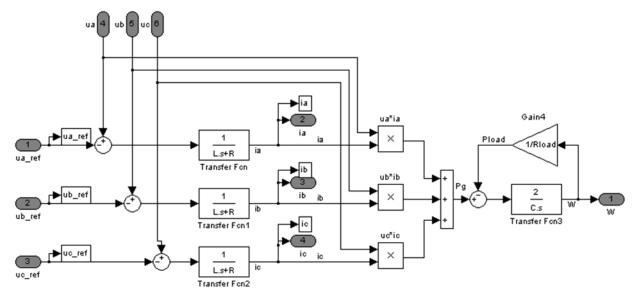

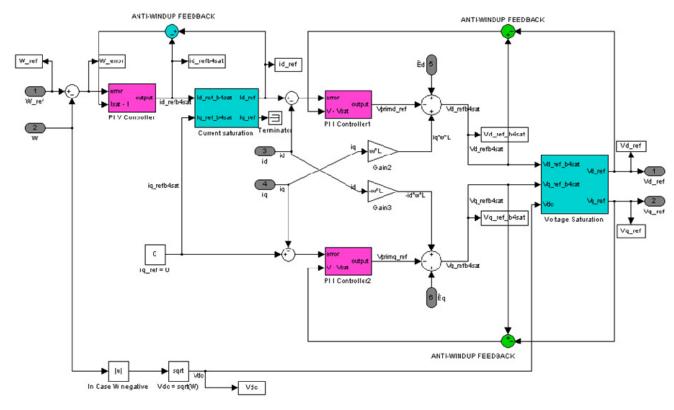

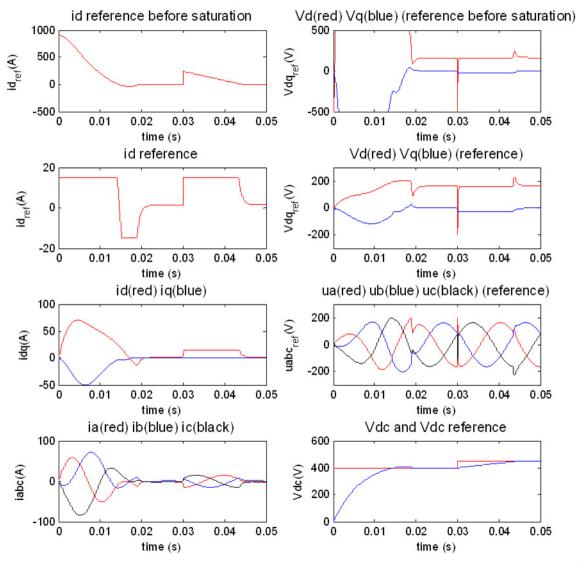

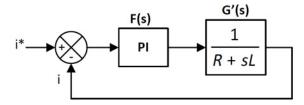

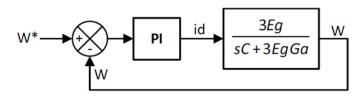

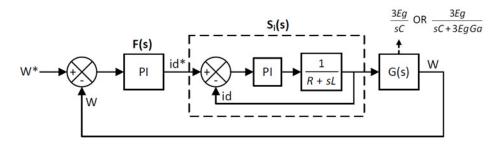

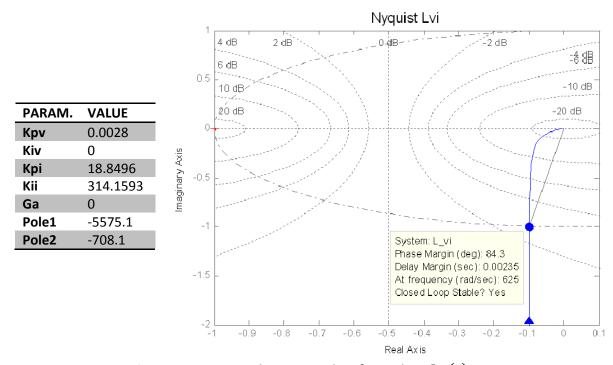

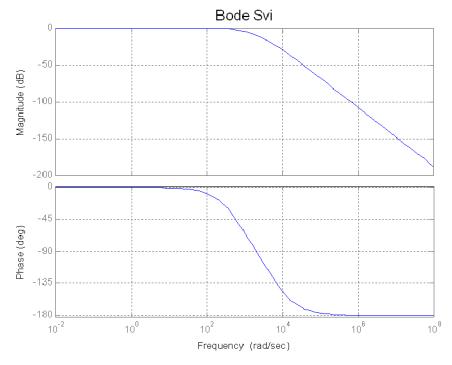

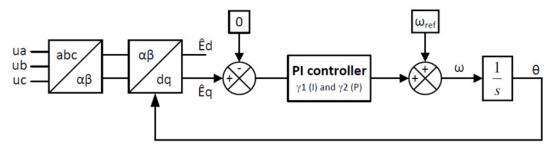

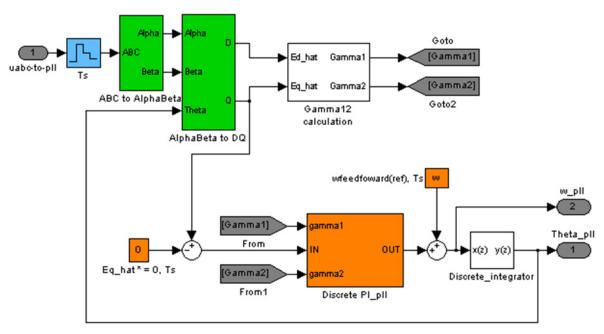

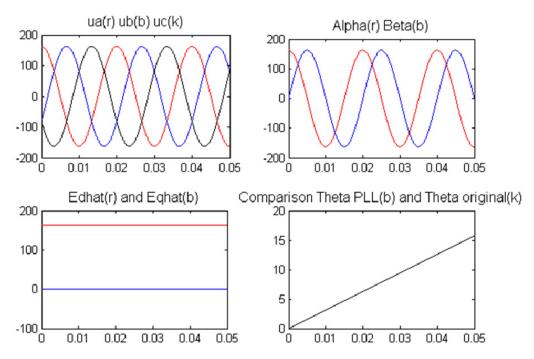

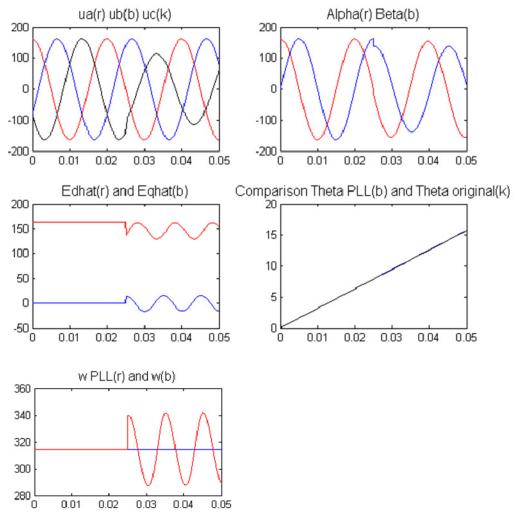

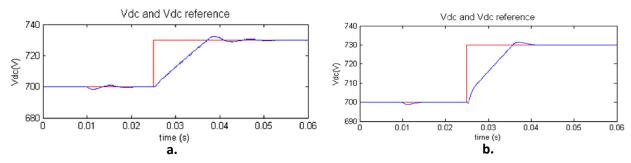

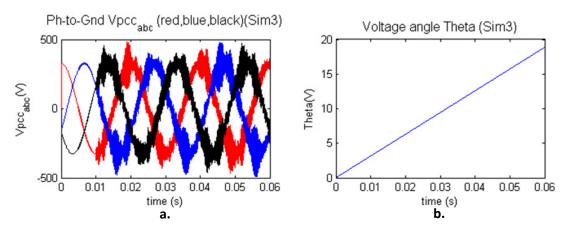

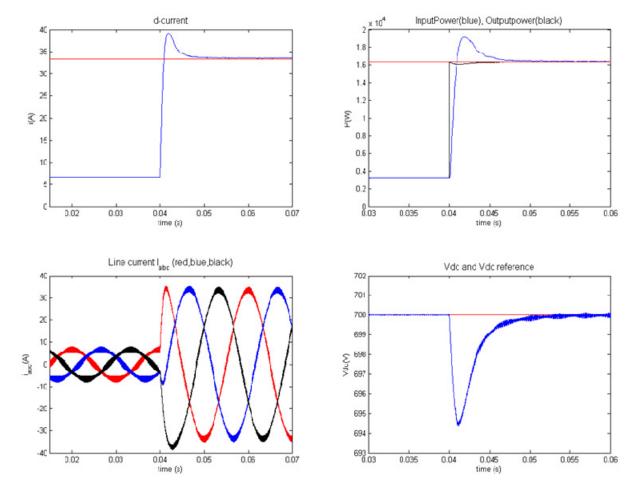

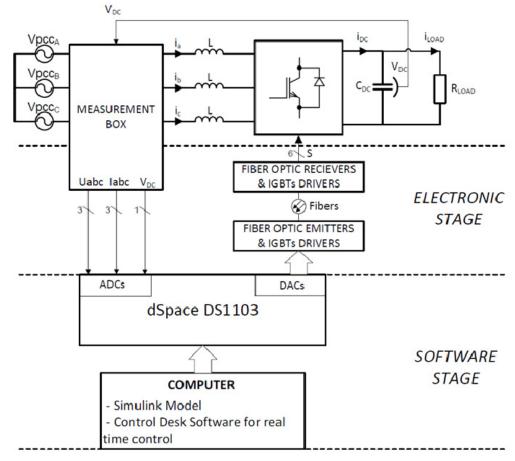

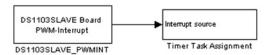

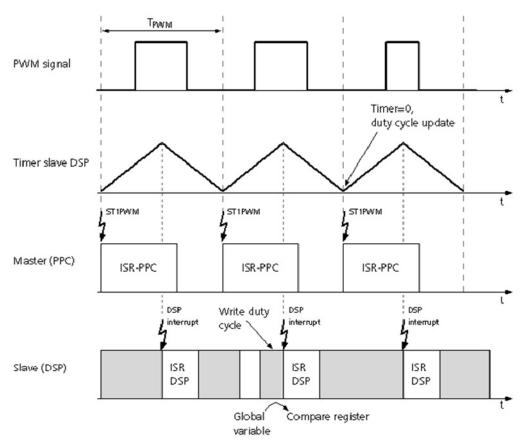

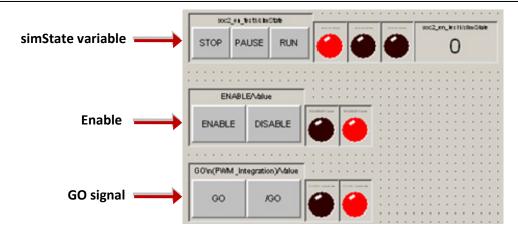

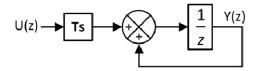

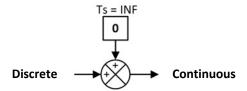

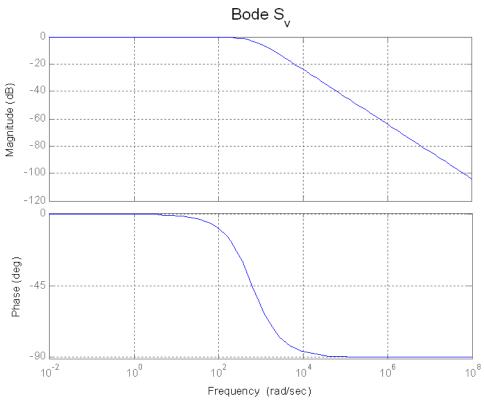

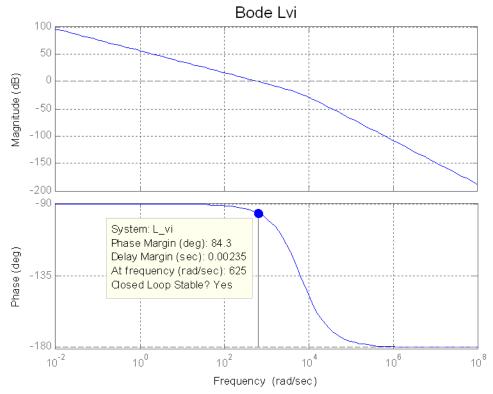

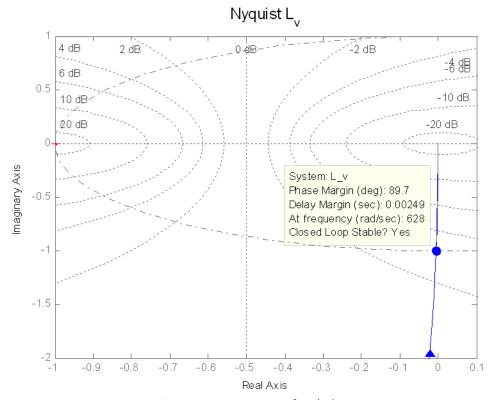

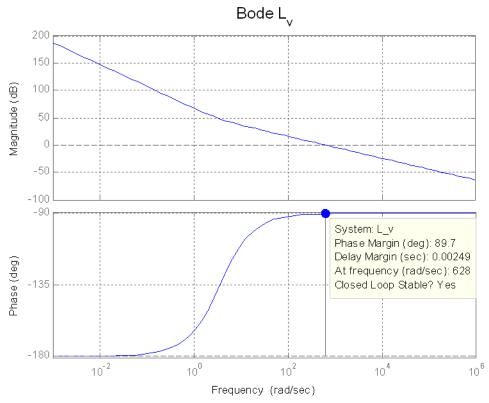

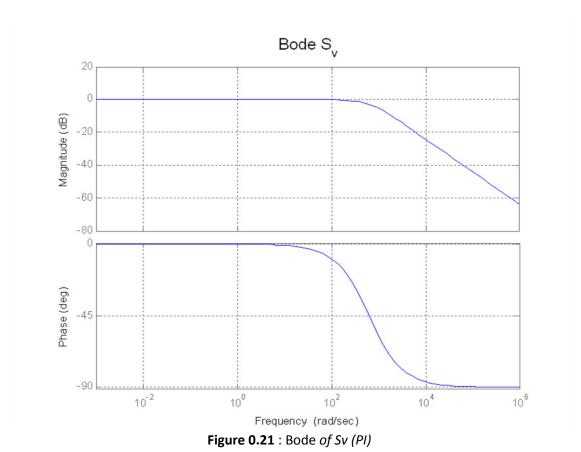

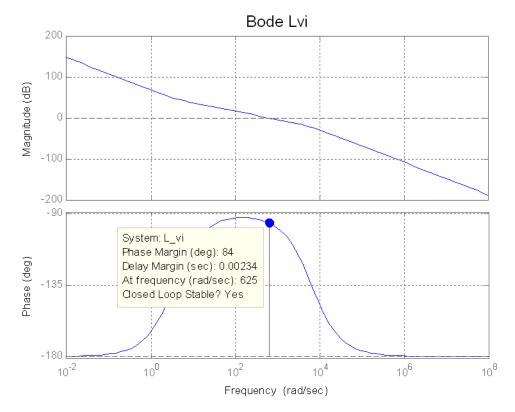

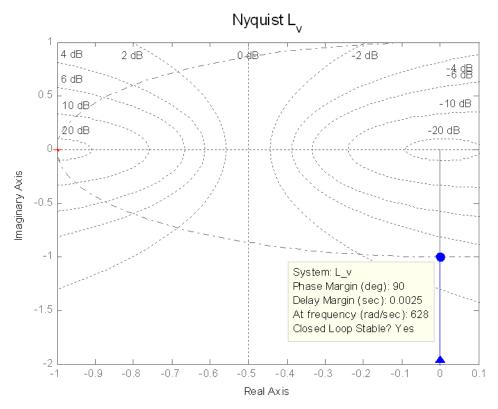

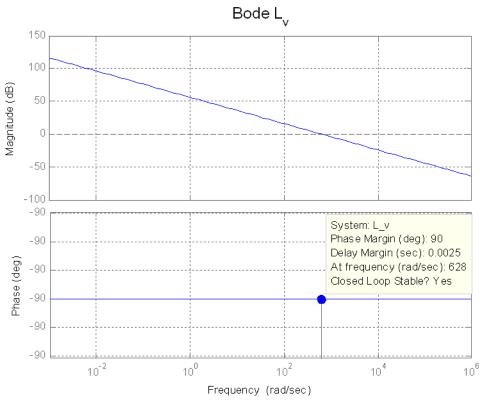

#### **⇒** PWM block without switch