# Design and Implementation of a Three-Phase Boost Battery Charger with PFC using CompactRIO Control System

COMPACTRIO

Digital input/output module. NI 9401

Master of Science Thesis in Electric Power Engineering

Analogic input module. NI 9215

# Daniel Castro Carmona Javier Fernández Mandiola

Controller

NI cRIO-9022

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden, 2012

# Design and implementation of a Three-Phase Boost Battery Charger with PFC using CompactRIO control system

Design, simulation and implementation of a 3-phase boost battery charger

By

Daniel Castro Carmona

Javier Fernández Mandiola

#### Supervisors

Saeid Haghbin

Tarik Abdulahovic

### Examiner

Ola Carlson

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden, 2012

# DESIGN AND IMPLEMENTATION OF A THREE-PHASE BOOST BATTERY CHARGER WITH PFC USING COMPACTRIO CONTROL SYSTEM

DESIGN, SIMULATION AND IMPLEMENTATION OF A 3-PHASE BOOST BATTERY CHARGER

DANIEL CASTRO CARMONA

JAVIER FERNANDEZ MANDIOLA

© DANIEL CASTRO CARMONA, 2012

© JAVIER FERNANDEZ MANDIOLA, 2012

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY SE-412 96 Göteborg Sweden Telephone : + 46 (0)31-772 1000 Göteborg, 2012

### Abstract

# Design and implementation of a Three-Phase Boost Battery Charger with PFC using CompactRIO control system

Design, simulation and implementation of a 3-phase boost battery charger

Daniel Castro Carmona

Javier Fernandez Mandiola

Department of Energy and Environment

**Division of Electric Power Engineering**

Chalmers University of Technology

In a plug-in hybrid electric vehicle, the utility grid charges the vehicle battery through a battery charger. For a three-phase grid supply voltage, three-phase boost rectifiers are commonly used as chargers. Bi-directional power transfer capability and unit power factor operation become desirable features due to the increasing power quality requirements on the grid-connected converters.

The Voltage Oriented Control is one of the methods based on high performance dqcoordinate controllers which satisfies the increasing power quality requirements. The Voltage Oriented Control method for a three-phase boost rectifier has been designed, simulated and implemented. The system simulation is performed using Matlab/Simulink software as well as Labview. A feedforward decoupled current controller is designed along with a Pulse Width Modulation scheme to control the battery charging. The controller, consisting of a current controller and a DC-link voltage controller, is designed using a method called Internal Model Control.

A National Instruments CompactRIO system is used for practical implementation. The system directly runs a Labview model to execute the control. The Labview files are developed for this purpose. A brief explanation of the system configuration is provided for the experimental system.

Keywords : battery charger, decoupled controller, Internal Model Control (IMC), Pulse Width Modulation (PWM), three-phase boost PWM rectifier, Voltage Oriented Control (VOC).

# Acknowledgements

First of all, we would like to offer our sincerest gratitude to our supervisors, Saeid Haghbin and Tarik Abdulahovic, for their support and availability during the thesis, for their understanding, patience and knowledge whilst facilitating us the room to work in our own way.

Our gratitude also goes to Ola Carlson, for giving us the opportunity to do this Master's Thesis work in the Electric Power division of Chalmers University of Technology. In addition, the Department of Electric Power Engineering has provided the support and equipment we have needed to produce and complete our thesis.

Thanks to all the employees and staff in the division who made our daily thesis work such a pleasant time. Furthermore, we would like to thank Magnus Ellsen for his availability and help for laboratory set-up as well as for letting us to use his own support material.

Daniel and Javier

Göteborg, Sweden

2012

# List of symbols, superscripts, subscripts and abbreviations

| ABBREVIATIONS        | SIGNAL OR VARIABLE                          |

|----------------------|---------------------------------------------|

| Pg                   | Power supplied by the grid                  |

| P <sub>load</sub>    | Power consumed by the battery               |

| V <sub>LL(rms)</sub> | Line-to-line voltage supply                 |

| V <sub>DC</sub>      | DC Bus voltage                              |

| $V_{LN(rms)}$        | Line-to-neutral voltage supply              |

| R <sub>load</sub>    | Load resistance                             |

| $E_m$                | Amplitude of Line-to-Neutral voltage        |

| R                    | Resistance of the line for each phase       |

| L                    | Inductance of the line for each phase       |

| ω                    | Frequency                                   |

| id                   | Current direct axis                         |

| iq                   | Current quadrature axis                     |

| I Ripple             | Ripple current                              |

| С                    | Capacitance of the inverter                 |

| $V_d^*$              | d-axis component of the reference voltage   |

| $V_q^*$              | q-axis component of the reference voltage   |

| θ                    | Voltage angle                               |

| $\alpha_i$           | Current controller bandwidth                |

| $\alpha_{v}$         | Voltage controller bandwidth                |

| $K_{pv}$             | Voltage controller proportional coefficient |

| K <sub>iv</sub>      | Voltage controller integrator coefficient   |

| K <sub>ii</sub>      | Current controller integrator coefficient   |

| K <sub>pi</sub>      | Current controller proportional coefficient |

| γ <sub>1</sub>       | PLL integrator coefficient                  |

| $\gamma_2$           | PLL proportional coefficient                |

| W                    | $Vdc^2$                                     |

| fsw                  | Switching frequency                         |

| Tj                   | Temperature in the junction                 |

| VOC                  | Voltage Oriented Control                    |

| PLL                  | Phase locked loop                           |

| IGBT                 | Insulated gate bipolar transistor           |

| VFOC                 | Virtual Flux Oriented Control               |

| PWM                  | Pulse Width Modulation                      |

| UPF                  | Unit Power Factor                           |

| DPC                  | Direct Power Control                        |

# **TABLE OF CONTENTS**

| Design and Implementation of a Three-Phase Boost Battery Charger with PFC using<br>CompactRIO Control System | i   |

|--------------------------------------------------------------------------------------------------------------|-----|

| Abstract                                                                                                     |     |

| Acknowledgements                                                                                             | vi  |

| List of symbols, superscripts, subscripts and abbreviations                                                  | vii |

|                                                                                                              |     |

| Chapter 1. Introduction                                                                                      | 1   |

| 1.1. | Background of the thesis and previous work. | 1 |

|------|---------------------------------------------|---|

| 1.2. | Purpose of the thesis                       | 1 |

| 1.3. | Outline of the thesis                       | 1 |

| Chapter 2. | Modeling and voltage oriented control of the rectifier        | 3   |

|------------|---------------------------------------------------------------|-----|

| 2.1. Thi   | ee phase controlled rectifiers                                | . 3 |

| 2.2. Vo    | tage oriented control                                         | .4  |

| 2.2.1.     | Space vector definition for voltage and current               | . 5 |

| 2.2.2.     | From abc to $\alpha\text{-}\beta$ using Clarke transformation | . 5 |

| 2.2.3.     | From $\alpha\text{-}\beta$ to d-q using Park transformation   | .6  |

| 2.2.4.     | Active and reactive power.                                    | .6  |

| Chapter 3. | System design                                      | 8  |

|------------|----------------------------------------------------|----|

| 3.1. Ha    | rdware design                                      | 9  |

| 3.1.1.     | Minimum DC-link voltage                            | 9  |

| 3.1.2.     | Load resistance.                                   | 11 |

| 3.1.3.     | Line inductance and ripple analysis.               | 11 |

| 3.1.4.     | Capacitance of the inverter.                       | 15 |

| 3.1.5.     | Switching frequency used in pulse width modulation | 15 |

| 3.1.6.     | Temperature limitation for the inverter            | 16 |

| 3.1.7.     | Measurement cards design                           | 19 |

| 3.1.7      | 7.1. Voltage measurement cards                     | 19 |

| 3.1.7      | 7.2. Current measurement cards                     | 21 |

| 3.1.8.     | Filter design                                      | 22 |

|      | 3.1.8 | .1. Voltage filter      | .22  |

|------|-------|-------------------------|------|

|      | 3.1.8 | .2. Current filter      | . 22 |

| 3.2. | MA    | TLAB simulations        | .24  |

| 3    | .2.1. | Continuous simulations. | .24  |

| 3    | .2.2. | Discrete simulations    | .25  |

| Chapter 4. Software development                                          | 27 |

|--------------------------------------------------------------------------|----|

| 4.1. Complete system and description of the simulation blocks            | 27 |

| 4.1.1. Inputs for the controller block                                   | 28 |

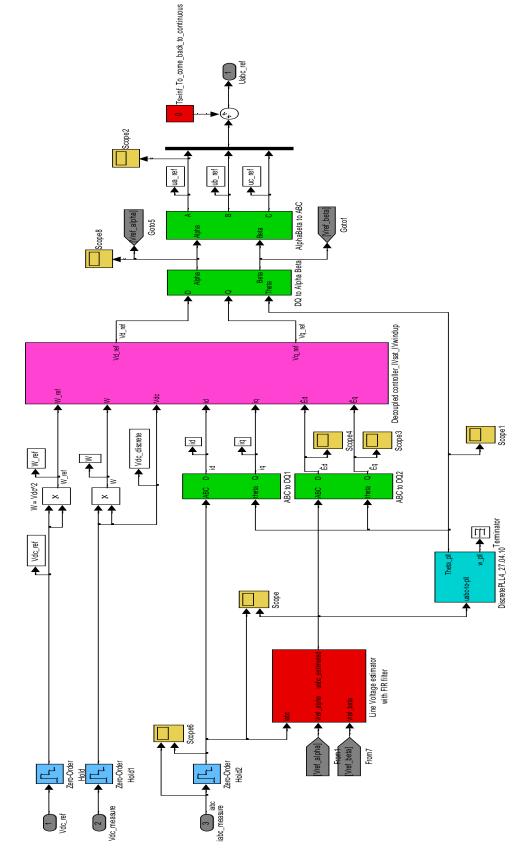

| 4.1.2. Controller block                                                  | 31 |

| 4.1.2.1. DC-link voltage controller.                                     | 32 |

| <ul> <li>Current saturation.</li> <li>Anti-windup Integrator.</li> </ul> |    |

| 4.1.2.2. Current controller                                              | 33 |

| <ul> <li>Voltage saturation.</li> <li>Anti-windup Integrator.</li> </ul> |    |

| 4.1.3. DQ-to-ABC transformation block                                    | 36 |

| 4.1.4. Sinusoidal pulse width modulation block.                          | 37 |

| 4.1.5. Rectifier model block                                             | 38 |

| 4.2. Simulation procedure.                                               | 41 |

### 5.1.2. 5.1.3. Measurement box......47 5.1.4. 5.1.5. Inverter and load......51 5.1.6.1. FPGA Programming......53 5.1.6.2.

| Chapter 6. Conclusions & Future work60                 |  |

|--------------------------------------------------------|--|

| 6.1. Conclusions                                       |  |

| 6.2. Future work                                       |  |

|                                                        |  |

| References                                             |  |

|                                                        |  |

| Appendix A: Hardware datasheets64                      |  |

| CompactRIO controller                                  |  |

| CompactRIO analog input module NI 921566               |  |

| CompactRIO digital input/output module NI 940168       |  |

| Isolation amplifier for the voltage transducers70      |  |

| LEM Current transducer74                               |  |

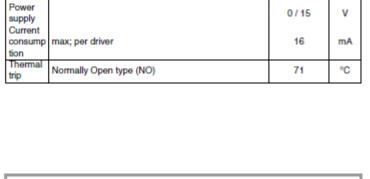

| Semistack Semikron inverter76                          |  |

|                                                        |  |

| Appendix B: Simulink simulations77                     |  |

| Complete simulation scheme77                           |  |

| PLL, Line voltage estimator and decoupled controller78 |  |

| PLL discrete block                                     |  |

| Line voltage estimator                                 |  |

| Decoupled controller                                   |  |

| Rectifier model                                        |  |

| PWM discrete block82                                   |  |

| Matlab code                                            |  |

# Chapter 1. Introduction.

In this introductory chapter, the project background, main objectives and thesis outline are described.

# **1.1.** Background of the thesis and previous work.

Nowadays, the level of pollution and the fossil fuel availability problem has contributed to a quick evolution of the hybrid and electric vehicles.

Electric and hybrid vehicles use electric power from the grid to charge their batteries but they usually do not use the traction system during charging. Since the battery charging and traction power do not happen at the same time, both inverter and engine can be used as a charger avoiding the need of building one with a rectifier. The possibility of using a motor as a double set of inductors during the charge time allows the implementation of an integrated charger to achieve a considerable reduction of weight, volume and price [1].

According to [2], the proposed charger is an isolated high power integrated charger based in the use of half of the windings of the engine during the charge. The use of this specific engine with the charger will be a new project to in a near future.

# **1.2. Purpose of the thesis.**

The main purpose of this thesis is to design and implement an integrated charger for an electrical or hybrid vehicle with a power requirement of 15KW and unit power factor operation as well as achieving the control of the inverter.

Firstly, the design of the different hardware is done. After this, simulations are conducted on Matlab/Simulink software [3] to check the validity of the design.

Secondly, the control system is developed by programming on LabView and implemented using a CompactRIO control device.

Finally, the experimental system is implemented in the laboratory and the results are obtained.

# **1.3. Outline of the thesis.**

This thesis is divided into 6 chapters. After this first chapter of introduction, the modeling and the selected type of control for the rectifier are explained in chapter 2. In chapter 3, the design of the system as well as the Matlab simulations are included. After that, chapter 4 includes the simulations of all the control programmed in Labview followed by chapter 5, in which the practical implementation is included.

Finally, in chapter 6, all the results and conclusions are shown as well as the future work.

Appendices are added to this report as part of the thesis. Matlab code used in simulations, lab setup diagrams and datasheets of the lab components are shown in appendices.

# Chapter 2. Modeling and voltage oriented control of the rectifier.

In this chapter, the rectifier topology is discussed. After that, the selected type of control (VOC) is presented as well as the mathematical model used to carry it out.

# 2.1. Three phase controlled rectifiers.

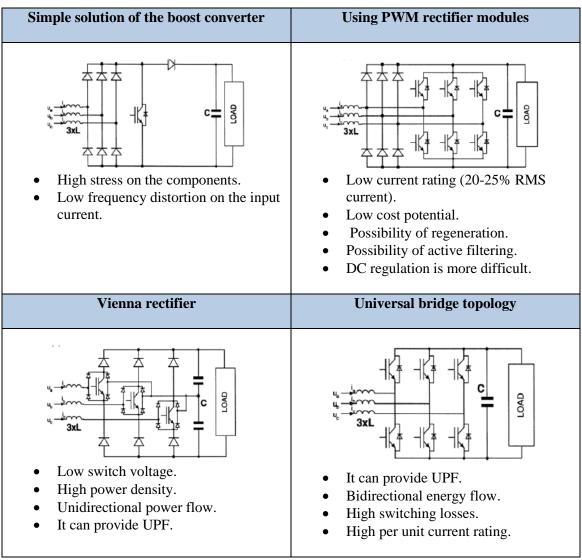

The aim of the thesis is to develop a three phase charger with unit power factor operation. To achieve that, several topologies have been compared and analyzed in Figure 1 in order to choose the topology which fulfills the requirements better.

Figure 1: Comparison of topologies [4][5].

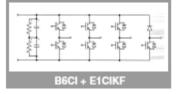

According to the specifications, the universal bridge topology is chosen and implemented using the SEMIKRON inverter.

### 2.2. Voltage oriented control.

Comparing several control methods, a VOC (Voltage Oriented Control) or VFOC (Virtual Field Oriented Control) can be implemented because both methods have the same advantages:

- Fixed switching frequency, which makes easier to design the input filter.

- Low sampling frequency for good performance.

- Advanced PWM is feasible with this control.

- A/D converters are cheap.

These control methods have also some disadvantages it is necessary to deal with:

- Decoupling between active and reactive power is required.

- Complex algorithm.

- Input power factor is lower than using DPC (Direct Power Control) or VF-DPC (Virtual Flux Direct Power Control).

The main advantage of the VFOC control against VOC is the better behaviour under non-linear conditions in the line voltage. In order to simplify the algorithm and due to the requirements of the system, the VOC control is implemented [3].

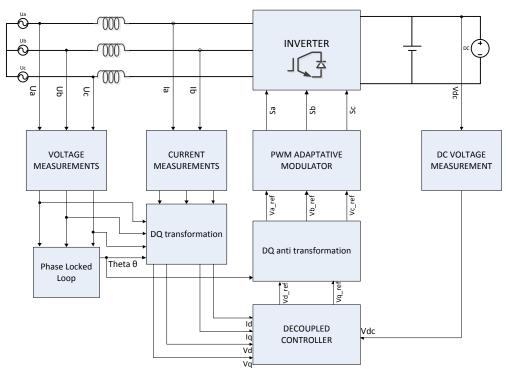

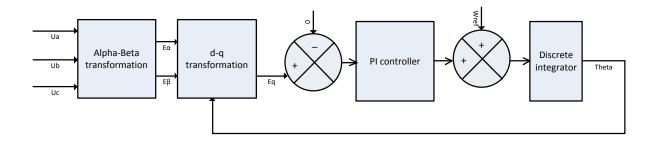

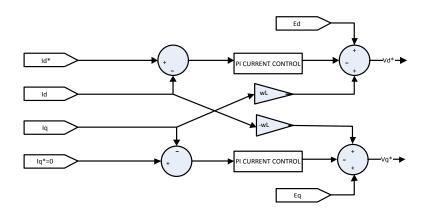

The Voltage Oriented Control is based on a series of transformations from a three phase stationary reference system *abc* to a synchronous rotating reference system *d-q* through a two phase stationary reference system  $\alpha$ - $\beta$ . With these transformations, the control voltages remain constant and become DC values, making all the control process more simple. A closed-loop current control is used. A scheme of the Voltage Oriented Control is shown in Figure 2.

Figure 2: VOC scheme.

The mathematical model and transformations used for the control are the following:

### 2.2.1. Space vector definition for voltage and current.

In a three phase system, the voltages and currents are defined by the equations 2.1 and 2.2.

$$Ua = \sqrt{2}V_{LN(rms)} \cdot \cos \omega t$$

$$Ub = \sqrt{2}V_{LN(rms)} \cdot \cos(\omega t - \frac{2\pi}{3})$$

$$Uc = \sqrt{2}V_{LN(rms)} \cdot \cos(\omega t + \frac{2\pi}{3})$$

(2.1)

$$Ia = Im \cdot \cos(\omega t + \varphi)$$

$$Ib = Im \cdot \cos(\omega t + \varphi - \frac{2\pi}{3})$$

$$Ic = Im \cdot \cos(\omega t + \varphi + \frac{2\pi}{3})$$

(2.2)

These three voltages or currents can be split in only two components  $\alpha$  and  $\beta$  (real and imaginary respectively) [6][7][8].

$$v^{s} = v_{\alpha} + jv_{\beta} = \frac{2}{3}k(v_{\alpha} + v_{b}e^{j\frac{2\pi}{3}} + v_{c}e^{-j\frac{2\pi}{3}})$$

(2.3)

For the control system that is going to be developed K=1 gives an amplitude invariant which facilitates the control. In other applications another K can be interesting in order to have power invariant ( $k=\sqrt{3/2}$ ) or RMS invariant ( $k=1/\sqrt{2}$ ) [8].

### **2.2.2.** From abc to $\alpha$ - $\beta$ using Clarke transformation.

The  $\alpha$ - $\beta$  transformation can be expressed applying the matrix form of the space vector definition.

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & -\frac{1}{3} & -\frac{1}{3} \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(2.4)

After the transformation the voltage equation can be written as follows.

$$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} u_{S\alpha} \\ u_{S\beta} \end{bmatrix}$$

(2.5)

### 2.2.3. From $\alpha$ - $\beta$ to d-q using Park transformation.

Physically, after the Clarke transformation, it is required to control 2 voltages ( $\alpha$ - $\beta$ ) instead of 3 voltages (abc), which simplifies the control. However,  $u_{\alpha}$  and  $u_{\beta}$  are still sinusoidal signals rotating physically with the angular speed of the electrical system  $\omega$ . Changing again the reference axis onto new axis, which are rotating at the same angular speed  $\omega$ , an amplitude invariance can be achieved. Applying Park transformation in d-q axis, the  $\alpha$ - $\beta$  axis are displaced by the angle  $\theta$ , as shown in [6] [7] [8].

$$v_{dq} = v^s e^{-j\theta} \tag{2.6}$$

After applying the  $\theta$  transformation.

$$u_{dq} = Ri_{dq} + L\frac{di_{dq}}{dt} + jL\omega i_{dq} + u_{Sdq}$$

(2.7)

After that, the real and the imaginary part are identified.

$$u_{d} = Ri_{d} + L\frac{di_{d}}{dt} - \omega Li_{q} + u_{Sd}$$

$$u_{q} = Ri_{q} + L\frac{di_{q}}{dt} + \omega Li_{d} + u_{Sq}$$

$$C\frac{du_{dc}}{dt} = \frac{3}{2}(S_{d}i_{d} + S_{q}i_{q}) - i_{load}$$

(2.8)

### 2.2.4. Active and reactive power.

Using the transformations shown before, an expression for the active and reactive power can be obtained [7].

$$Re\{v^{s}(i^{s})^{*}\} = Re\{v^{dq}(i^{dq})^{*}\}$$

$$v^{s}(i^{s})^{*} = \left(\frac{2}{3}K\right)^{2} \left(v_{a} + v_{b}e^{j\frac{2\pi}{3}} + v_{c}e^{j\frac{4\pi}{3}}\right) \left(i_{a} + i_{b}e^{j\frac{2\pi}{3}} + i_{c}e^{j\frac{4\pi}{3}}\right)^{*}$$

$$= \left(\frac{2}{3}K\right)^{2} \left[v_{a}i_{a} + v_{b}i_{b} + v_{c}i_{c} + j\frac{1}{\sqrt{3}}\left(v_{a}(i_{c} - i_{b}) + v_{b}(i_{a} - i_{c}) + v_{c}(i_{b} - i_{a})\right)\right]$$

(2.9)

From the real part, the active power is obtained.

$$P = \frac{3}{2K^2} Re\{v^s \ (i^s)^*\} = \frac{3}{2K^2} Re\{v^{dq} \ (i^{dq})^*\} = v_a i_a + v_b i_b + v_c i_c \qquad (2.10)$$

From the imaginary part, the reactive power can be calculated.

$$Q = \frac{3}{2K^2} Im(v^s (i^s)^*) = \frac{3}{2K^2} Im\{v^{dq} (i^{dq})^*\}$$

=  $\frac{1}{\sqrt{3}} [v_a(i_c - i_b) + v_b(i_a - i_c) + v_c(i_b - i_a)].$  (2.11)

In this particular case, as consequence of the transformation to d-q axes, the q component of the voltage is zero. Because a charger with unit power factor is being implemented, the current will be synchronized with the voltage and therefore, the q component of the current will also be zero as well. This simplifies the equations of the active and reactive power to.

$$P = \frac{3}{2}E_d I_d \qquad \qquad Q = 0 \tag{2.12}$$

# Chapter 3. System design.

In this chapter, all the parameters of the components that are used in the following chapters are calculated (see Figure 3). To check the validity of these calculations, given Simulink/MATLAB files are used modifying the design parameters to satisfy the new power requirement [3].

This chapter is divided in two parts:

- I. The first one contains the calculations needed to design the hardware and choose the appropriate components.

- II. The second one contains the simulations in Simulink/MATLAB to verify the behavior of the system and if it follows the specifications and requirements.

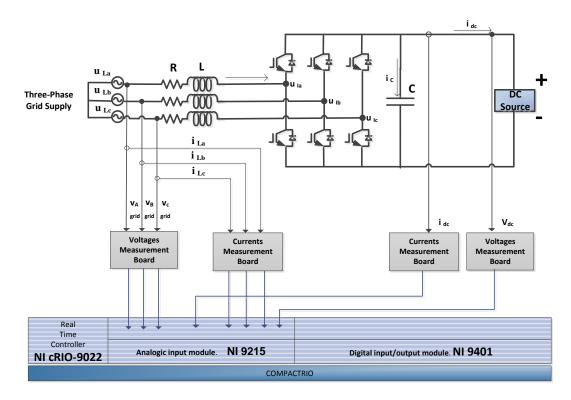

Figure 3: General view of the system scheme.

The design of the components of the charger starts from the desired power level for the system.

| <i>P<sub>g</sub></i> =15 KW | <i>V<sub>LL(rms)</sub></i> = 400 V (line-to line) |

|-----------------------------|---------------------------------------------------|

### 3.1. Hardware design.

### 3.1.1. Minimum DC-link voltage.

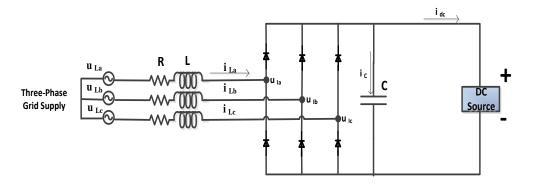

The correct selection of the DC-link voltage needs to be done in order to assure a complete control of the inverter. The voltage should be high enough to polarize the diodes in inverse mode (Figure 4) but always taking into account the limit of the inverter, in our case the semi teach IGBT's.

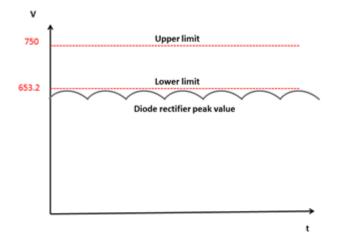

Following the specifications of our inverter, the voltage should be less than 750 V [9].

$$V_{DC} < 750 \text{ V}$$

(3.1)

To polarize a diode in inverse mode, the DC voltage has to be higher than the peak value of the diode rectifier line-to-line voltage [4].

Figure 4: Three phase diode rectifier.

$$V_{DC} > \sqrt{2}V_{LL(rms)} = \sqrt{2}.\sqrt{3}.V_{LN(rms)}$$

(3.2)

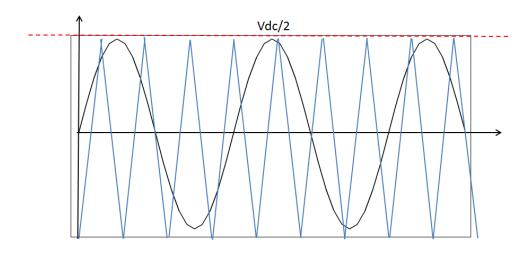

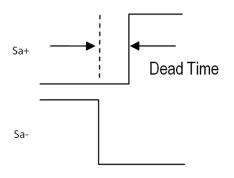

Note that the maximum line-to-line voltage in the rectifier will depend on the control mode of the inverter, in this case sinusoidal pulse width modulation. In this control, three-phase reference voltages are compared with a triangular wave with fixed amplitude and frequency (Figure 5). Each comparator will obtain the switching pattern for each leg of the inverter.

Depending on the switching state, the positive or negative half of the  $V_{DC}$  will be applied in the inverter, this is very important to fix the lower limit for the DC bus. [10]

Figure 5: Maximum reference value achievable in PWM.

Using Sinusoidal pulse with modulation, the minimum DC voltage becomes the DC voltage that is provided by the diode rectifier and the maximum DC voltage is established from the limitations of the inverter as shown in Figure 6.

$$V_{LN(peak)} = \frac{V_{DC}}{2}$$

$$\frac{V_{LL(rms)}}{\sqrt{3}}\sqrt{2} = \frac{V_{DC}}{2}$$

$$V_{DCmin} > 2 V_{LN(peak)} = \frac{2\sqrt{2}}{\sqrt{3}} V_{LL(rms)} = 653.19 V$$

(3.3)

Figure 6: Range of DC bus voltage between the diode rectifier behavior and inverter limit.

*V<sub>DC</sub>*=700 V

### **3.1.2.** Load resistance.

For the first approximation, in this thesis a resistor is going to be used as load on the DC bus. After the implementation, a DC source is used to have a model closer to a real battery. The load resistance that is needed to fulfill the power specifications depends on the selected DC voltage. It can be calculated in two different ways.

Considering the inverter has no losses.

$$P_{g} = P_{load} = \frac{v_{dc}^{2}}{R_{load}}$$

$$R_{load} = \frac{v_{dc}^{2}}{P_{g}} = \frac{700^{2}}{15000} = 32.66\Omega$$

(3.4)

Taking into account the performance of the inverter and supposing a value of 95-98 % for performance of an auto switched inverter with IGBT technology [9].

$$P_{load} = \frac{v_{dc}^2}{R_{load}}$$

$$R_{load} = \frac{v_{dc}^2}{R_{load}} = \frac{700^2}{0.95(15000)} = 34.38\Omega$$

(3.5)

Finally, for simplicity, a  $33\Omega$  resistor is chosen.

### **3.1.3.** Line inductance and ripple analysis.

Following the Chapter 11 in reference [4], a minimum value of DC voltage is defined taking into consideration the inductance. This formula is valid in our case due to the amplitude invariance transformation.

The DC bus voltage has to be high enough to compensate the voltage drop in the inductance. It can be checked that if the inductance value is zero the formula is equivalent to (3.3).

$$V_{DC} > \sqrt{4[E_m^2 + (\omega Lid)^2]}$$

$$L < \frac{\sqrt{\frac{V_{DC}^2}{4} - E_m^2}}{\omega i d}$$

(3.6)

Based on the d-q transformations, equations for active and reactive power are obtained.

$$P = \frac{3}{2} Re\{v^{dq}(i^{dq})^*\} = \frac{3}{2}(v_d i_d + v_q i_q) = \frac{3}{2}(E_d i_d + E_q i_q)$$

$$Q = \frac{3}{2} Im\{v^{dq}(i^{dq})^*\} = \frac{3}{2}(v_q i_d - v_d i_q) = \frac{3}{2}(E_q i_d - E_d i_q)$$

(3.7)

In our system a unitary power factor is demanded so a decoupled current control design will be achieved to obtain  $i_q = 0$ . Using this control, the active and reactive power can be written as [3]:

$$P = \frac{3}{2} E_d i_d$$

$$Q = 0$$

$$id = \frac{2}{3E_g} P_g = 30.61 \text{ A}$$

(3.8)

This value is confirmed in the simulations of the system.

According with the grid voltage specifications,  ${\cal E}_{g}$  is calculated.

$$E_g = \sqrt{2} \frac{400}{\sqrt{3}} = 326.6 V \text{ (Phase-to-Ground)}$$

(3.9)

Finally, in order to obtain the limit for the inductance, the initial formula is used.

$$L < \frac{\sqrt{\frac{V_{DC}^2}{4} - E_g^2}}{\omega i d}$$

$$L < \frac{\sqrt{\frac{700^2}{4} - 326.6^2}}{2\pi 50 \times 30.61}$$

(3.10)

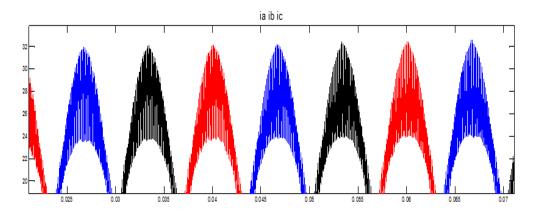

The minimum value that can be used for the inductance depends on the maximum current ripple for the system. A series of simulations of the complete system have been carried out with different values of the inductance to analyze the current ripple.

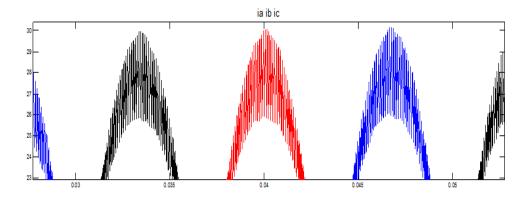

Using 1mH, as it is a very common value for Boost converters, the current ripple is shown in the following simulation figure (Figure 7).

Figure 7: Current ripple with L= 1mH.

I Ripple =

$$31,8-23,5=8,3$$

A (3.11)

Theoretically, the current ripple is calculated using the equation of the voltage drop in an inductance.

$$\Delta i_L = \frac{\frac{V_{DC} - U}{2}}{Lf} \cdot D = \frac{\frac{700 - 400}{2}}{Lf} \cdot 0,5 = 6A$$

(3.12)

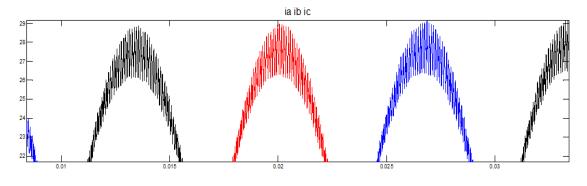

Using a value for the inductance of 2mH, according to the simulation results (Figure 8) the current ripple is also calculated.

Figure 8: Current ripple with L=2mH.

$$I_{Ripple} = 29,7 - 25,4 = 4,3 A \tag{3.13}$$

Theoretically, the current ripple is calculated using the equation of the voltage drop in an inductance.

$$\Delta i_L = \frac{\frac{V_{DC}}{2} \frac{U}{\sqrt{3}}}{Lf} \cdot D = \frac{\frac{700}{2} \frac{400}{\sqrt{3}}}{Lf} \cdot 0,5 = 3A$$

(3.14)

According to the simulation results shown in Figure 9 , the current ripple using a 3mH inductance is calculated.

Figure 9: Current ripple with L= 3mH.

$$I_{Ripple} = 29 - 26, 4 = 2, 6 A \tag{3.15}$$

Theoretically, the equation of the voltage drop in an inductance is used to calculate the current ripple.

$$\Delta i_L = \frac{\frac{V_{DC}}{2} \frac{U}{\sqrt{3}}}{Lf} \cdot D = \frac{\frac{700}{2} \frac{400}{\sqrt{3}}}{Lf} \cdot 0,5 = 1,98A$$

(3.16)

Finally, referencing to the acceptable current ripple in Boost converters applications, 3 mH has been chosen as inductance value.

### **3.1.4.** Capacitance of the inverter.

According to the inverter specifications, the filtering capacitors are electrolytic capacitors with an individual value of  $2200\mu$ F/400V, two connected in series and two in parallel.

For all the calculations the equivalent capacitance of the complete DC bus is used [11].

$C = 1100 \mu F / 800 V$

### 3.1.5. Switching frequency used in pulse width modulation.

A fixed switching frequency is used in Voltage Oriented Control in order to have an easier design and to achieve a lower sample frequency. To minimize the effect of the harmonics on system performance, the PWM frequency should be high. But a higher frequency also means higher switching losses, so an intermediate value is used.

fsw = 10 KHz

| Resume template                             |

|---------------------------------------------|

| <i>P<sub>IN</sub></i> =15 KW                |

| V <sub>LL(rms)</sub> = 400 V (line-to line) |

| <i>V<sub>DC</sub></i> =700 V                |

| $R_{load}=33\Omega$                         |

| L = 3mH                                     |

| $C = 1100 \mu F/800V$                       |

| fsw = 10 KHz                                |

| Table 1: Design parameters conclusion.      |

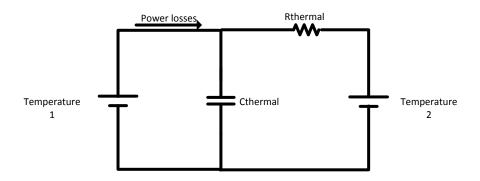

### **3.1.6.** Temperature limitation for the inverter.

It is very important to know what the temperature limit of the junction is.

The junction temperature  $T_{jmax}$  is usually 150,° but for safety reasons 125° is more appropriate value to consider. As mentioned before, an inverter using the IGBT technology has efficiency of 95-98%.

Losses have to be dissipated to maintain components in a safe range of temperatures. This is the reason why it is necessary to calculate the equivalent thermal impedance of the system and check if the temperature is lower than the maximum temperature on the junction.

The thermal impedance can be modeled as a capacitor and a resistance, as shown in Figure 10.

Figure 10: Equivalent thermal circuit.

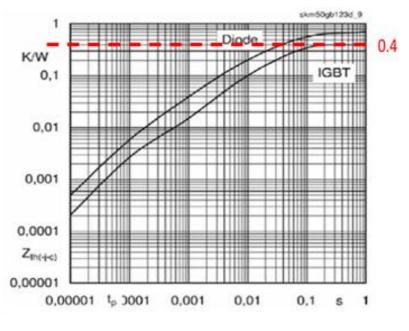

Following the impedance values given in the datasheet of our inverter, it is possible to check that the value changes over time, but after 0.5 s of transient state, the capacitor value is neglected and only the resistance is taken into consideration. For nominal operation of the inverter the value of the thermal resistance is 0.4 K/W (see Figure 11).

Figure 11: Thermal resistance VS time.

In the worst case scenario the inverter has efficiency of 95%, supposing steady state and that the 6 IGBT's produce the same losses, the temperature in the junction can be calculated as follows.

$$\Delta T = \frac{0.4 \cdot 15000 \cdot 0.05}{6} = 50 \text{K}$$

$$Tj = 20^{\circ} + 50^{\circ} = 70^{\circ}$$

(3.17)

In order to have a more accurate estimation of the losses, the conduction losses and the switching losses are calculated following the expressions from datasheet [9].

The switching losses appear during the commutation due to the switching patterns.

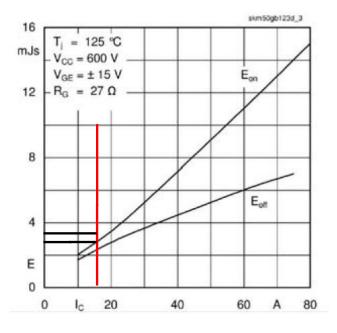

The switching losses (on+off) for a 3 phase inverter, using the graph in Figure 12 are calculated.

$$P_{ON+OFF(IGBT)} = \frac{\sqrt{2Irms}}{\pi} \cdot fsw \cdot U \cdot K$$

$$P = fsw \cdot (Eon + Eoff))$$

$$P=10kH(2,6+3,4)=60W$$

(3.18)

Figure 12: Switching losses from the datasheet of the inverter.

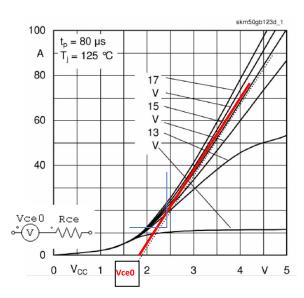

The conduction losses in an IGBT are the result of the product of the current and the voltage (collector-emitter) during the conduction period.

The conduction losses for IGBT's in a 3 phase inverter can be estimated by.

$$P_{cond(IGBT)} = \frac{1}{2} \cdot \left(\frac{1}{\pi} \cdot Vceo + r \cdot \frac{I^2}{4}\right) + m \cdot cos\varphi \cdot (Vceo \cdot \frac{I}{8} + \frac{rI^2}{3\pi})$$

(3.19)

Where *m* is a degree of modulation and  $V_{ce0}$  and *r* are determined graphically from the datasheet curves. This depends on the application, and can be calculated using the rms value of the current. The parameters for the conduction losses are calculated, using Figure 13.

Figure 13: Conduction losses from the datasheet of the inverter

$$I_{\rm rms} = \frac{29,7}{\sqrt{3}} = 17,14 \text{A}$$

$$V ce0 = 1,9 \text{V}$$

$$r = \Delta u / \Delta I = 1 \text{V} / 30 \text{A} = 0,03 \Omega$$

*lumbers* 400

$$m = \frac{\frac{0.7ms}{\sqrt{3}}}{\frac{Udc}{2}} = \frac{\frac{400}{\sqrt{3}}}{\frac{700}{2}} = 0,659$$

#### Pcond=4,703W

$$Plosses=64,7W \tag{3.21}$$

$$\Delta T = 0.4 \cdot 64, 7 = 25,88 \text{K}$$

Tj=20°+25,88°=45,88°

This temperature in the junction is much lower than the limit given in the data sheet. For this reason, the inverter can be used in the setup for this power level.

### 3.1.7. Measurement cards design.

In order to develop the control system, certain measures of voltages and currents are necessary.

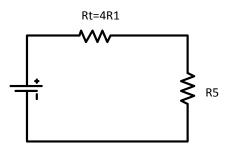

#### **3.1.7.1. Voltage measurement cards.**

For this purpose, voltage transducers UMAT2 are used. They have three channels to measure three different signals with a common neutral point. The three channels of one of the voltage transducers are used to measure the three-phase voltage and only one channel of another voltage transducer is used to measure the DC voltage [1].

The transducer is an electronic device that converts energy from one form to another. In our case, the transducer UMAT2 is used as a voltage divider to give a low voltage output that our control system can manage.

The compactRIO system is an electronic system made of modules. This is very useful and can be used for different applications and purposes. In this case, the corresponding module with analog inputs has a range of ±10 V input ranges [12].

Figure 14: Voltage divider circuit.

For the transducer measuring the three-phase voltage, the maximum voltage phase-to-ground that can be measured is 327V, so the calculations are set taking into account this value.

$$U_{1} = \pm 400V$$

$$U_{2} = \pm 10V$$

$$R_{t} = \sum R_{1} + R_{2} + R_{3} + R_{4} = 4 \cdot R_{1}$$

(3.22)

Applying the voltage divider formula, the ratio between both peak values is obtained.

$$\frac{U_2}{U_1} = \frac{R_5}{R_5 + R_t} = 10V/400V = 0.025$$

(3.23)

Standard values for resistors are chosen.

$$R_5 = 12k\Omega$$

$$R_1 = R_2 = R_3 = R_4 = 120k\Omega$$

(3.24)

With these values, the voltage ratio is obtained.

$$\frac{U_2}{U_1} = \frac{R_5}{R_5 + R_t} = 0.02439 \tag{3.25}$$

For the transducer measuring the DC voltage, the voltage of 750 V is chosen as a maximum because it is the maximum DC voltage that the inverter can support.

$$U_{1} = \pm 750V \\ U_{2} = \pm 10V \\ R_{t} = \sum R_{1} + R_{2} + R_{3} + R_{4} = 4 \cdot R_{1}$$

(3.26)

Applying the voltage divider formula, the ratio between both peak values is obtained.

$$\frac{U_2}{U_1} = \frac{R_5}{R_5 + R_t} = \frac{10V}{750V} = 0.01333 \tag{3.27}$$

Standard values for resistors are chosen.

$$R_{5} = 13k\Omega$$

$$R_{1} = R_{2} = R_{3} = R_{4} = 240k\Omega$$

(3.28)

With these values, the voltage ratio is obtained.

(3.29)

The error between the theoretical and the calculated value is 0.23%, which is sufficiently accurate.

Using this transducer, the maximum value of the DC voltage (750V) corresponds to 10.02V, which is within the range of measurement of the compactRIO module for analogic inputs [12].

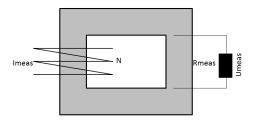

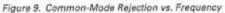

### 3.1.7.2. Current measurement cards.

In the same way as with the voltage, transducers are used. These transducers are four LEM LA 50-S/SP1 are going to be used. This electronic device produces a voltage drop  $U_{meas}$  in a resistance  $R_{meas}$  because of the current  $I_2$ , which is proportional to the current measured in a factor that depends on the number of turns [1].

#### Figure 15: LEM scheme

Using an identical compact RIO module for analogical inputs with a range of  $\pm 10$  V and the datasheet of the transducer, the relationship between currents is obtained.

$$\frac{I_{meas}}{I_2} = \frac{2000}{N}$$

(3.30)

where N is the number of turns in the LEM device. By choosing a number of turns that provides a good accuracy, it is possible to calculate the value of  $R_{meas}$ .

$$N=10 \text{ turns}$$

$$\frac{I_{meas}}{I_2}=200$$

$$I_{meas} = 200I_2 = 200\frac{U_{meas}}{R_{meas}}$$

$$R_{meas} = 40\Omega$$

(3.31)

Selecting this value of  $R_{meas}$ , the relationship of the output voltage with the current measured is  $\frac{1}{5}$ . This is an appropriate value for our system because the maximum value of the current is ±50A, which corresponds to an output voltage of ±10 V. This is the exact range of the National Instruments analogic input module which is used [12].

### 3.1.8. Filter design.

Filters are very important in data acquisition systems to remove the undesirable frequencies from the signal that is being measured. To achieve this, analog filters are used before the analog to digital converter [13].

#### 3.1.8.1. Voltage filter.

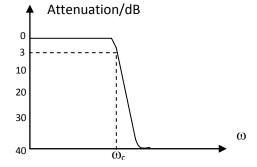

Operating with a switching frequency of 10kHz, a sample frequency of 1kHz is enough to sample the 50 Hz voltages because this is more than the double of frequency and it is sufficient to keep the desired frequency below the Nyquist limit [14].

A cut-off frequency of 1kHz in the low pass filter is enough for the voltage before the digital conversion. Taking into account the anti aliasing effect, the chosen frequency is 2kHz [15].

The design of the passive first order filter is completed using the well-known formula.

$$fc = \frac{1}{2\pi RC} \tag{3.32}$$

Figure 16: Attenuation scheme using a low pass filter.

Making the calculations and choosing a capacitor of C=10nF, the resistor value is calculated as R=7,95k $\Omega$ . Finally, for simplicity, R=10 k $\Omega$  is chosen.

#### 3.1.8.2. Current filter.

Calculations are done in the same way as for the voltage filter but using a sampling frequency of 5kHz. Choosing a capacitor of C=10nF, the resistor value obtained is R=3,18  $\Omega$ . Finally, selecting a standard value, R=3,3 k $\Omega$  is chosen.

Figure 17: Data communication between CompactRIO and the system.

| Signal | Measure range | Input CRIO<br>range | Units | Sampling<br>Frequency |

|--------|---------------|---------------------|-------|-----------------------|

| Ua     | $\pm 400$     | <u>+</u> 10         | V     | 1 kHz                 |

| Ub     | $\pm 400$     | <u>+</u> 10         | V     | 1 kHz                 |

| Uc     | $\pm 400$     | $\pm 10$            | V     | 1 kHz                 |

| la     | $\pm 50$      | <u>+</u> 10         | V     | 5 kHz                 |

| lb     | <u>±</u> 50   | $\pm 10$            | V     | 5 kHz                 |

| lc     | <u>±</u> 50   | $\pm 10$            | V     | 5 kHz                 |

| Udc    | 750           | $\pm 10$            | V     | 1 kHz                 |

| Idc    | <u>±</u> 50   | $\pm 10$            | V     | 5 kHz                 |

Table 2: Range of measurements and sample rate.

| Voltage measurement board |         |    |  |

|---------------------------|---------|----|--|

| <i>R5</i>                 | 12      | KΩ |  |

| <i>R1=R2=R3=R4</i>        | 480     | KΩ |  |

| Ratio of conversion       | 0.02439 |    |  |

|                           |         |    |  |

Table 3: Voltage measurement board.

| Voltage DC measurement board           |         |    |  |  |

|----------------------------------------|---------|----|--|--|

| R5                                     | 13      | KΩ |  |  |

| <i>R1=R2=R3=R4</i>                     | 240     | KΩ |  |  |

| Ratio of conversion                    | 0.01336 |    |  |  |

| Table 4: DC voltage measurement board. |         |    |  |  |

| Current measurement board |     |       |  |

|---------------------------|-----|-------|--|

| Ν                         | 10  | turns |  |

| Rmeas                     | 40  | Ω     |  |

| Ratio of conversion       | 0.2 |       |  |

Table 5: Current measurement board.

| Voltage antialiasing filt             | er |           |  |

|---------------------------------------|----|-----------|--|

| С                                     | 10 | nF        |  |

| R                                     | 10 | $k\Omega$ |  |

| frequency                             | 2  | kHz       |  |

| Table 6: Voltage antialiasing filter. |    |           |  |

| Current antialiasing fil             | ter |           |  |  |

|--------------------------------------|-----|-----------|--|--|

| С                                    | 10  | nF        |  |  |

| R                                    | 3,3 | $k\Omega$ |  |  |

| frequency                            | 5   | kHz       |  |  |

| Table 7. Connect antiolissing filter |     |           |  |  |

Table 7: Current antialiasing filter.

### **3.2.** MATLAB simulations.

In order to check the validity of all the calculated parameters of the system, simulations in continuous mode and in discrete mode have been carried out.

### **3.2.1.** Continuous simulations.

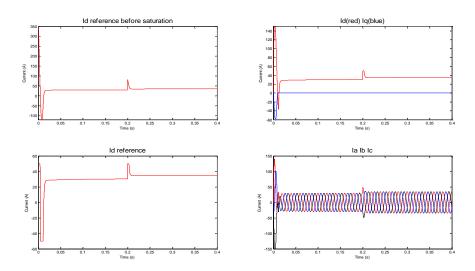

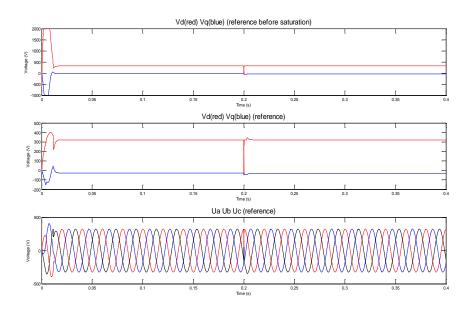

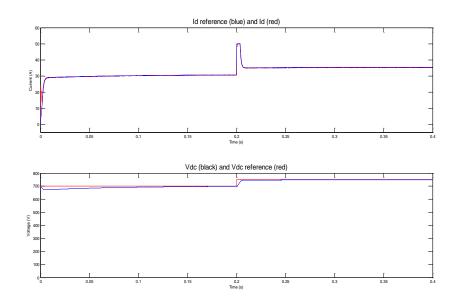

In all the simulations the behavior after a DC voltage step is checked. As shown for the currents results in Figure 18, the current values for the desired power level are around 35 A. This quantity is much lower than the limit of the inverter, which is 50A. In Figure 19, the reference voltages are shown before saturation as well as after saturation referred to d-q axis. Besides, the ABC reference voltages after anti transformation are shown in the third graph.

Figure 18: Currents in continuous simulation

Figure 19: Voltages in continuous simulation

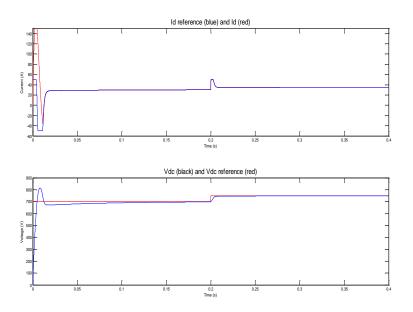

In order to verify the behavior of the system under a step variation in the DC voltage, the current referred to d-q axis is shown in Figure 20.

Figure 20: System behavior after DC voltage step.

### **3.2.2. Discrete simulations.**

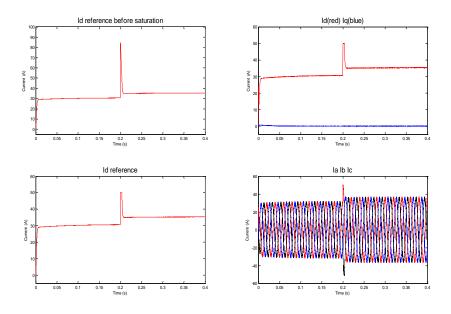

Carrying out an equivalent simulation with a step in the DC voltage, the current is limited to a value of 50 A during the transient state after the perturbation, as can be seen in Figure 21.

Figure 21: Currents in discrete simulation.

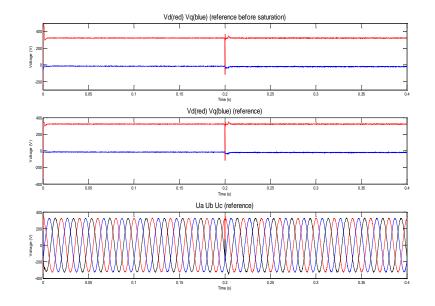

### On Figure 22, the reference voltages after Park's transformation are shown.

Figure 22: Voltages in discrete simulation.

The last figure of the simulations, Figure 23, shows the DC voltage and the d axis current. A good and quick response is observed because of the little integration time that was used (Ts=1\*10-5s).

Figure 23: System behavior after DC voltage step.

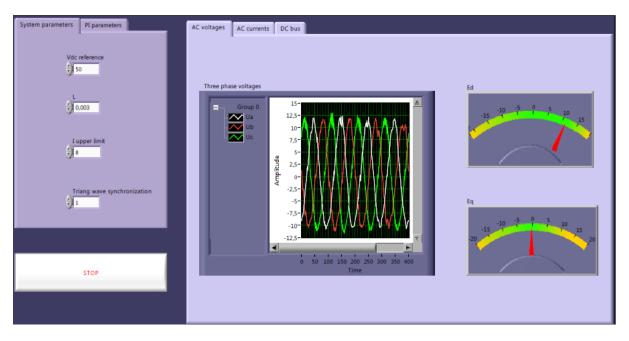

## Chapter 4. Software development.

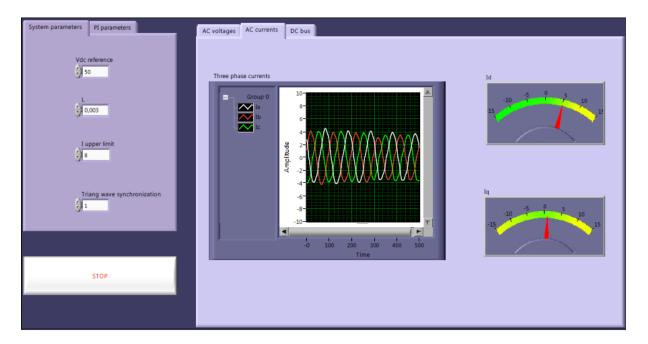

In this chapter, all the simulations of the system and the control of the inverter are developed using Labview, which is the system design software created by National Instruments. In the first part, all the blocks used in the simulation are described in detail. In the second part, the running of the program is explained from the starting up to the steady state.

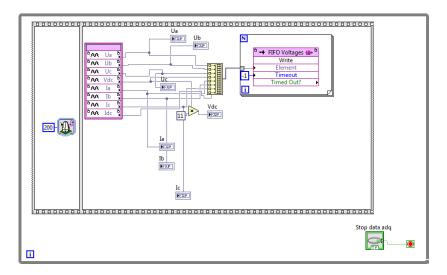

## 4.1. Complete system and description of the simulation blocks.

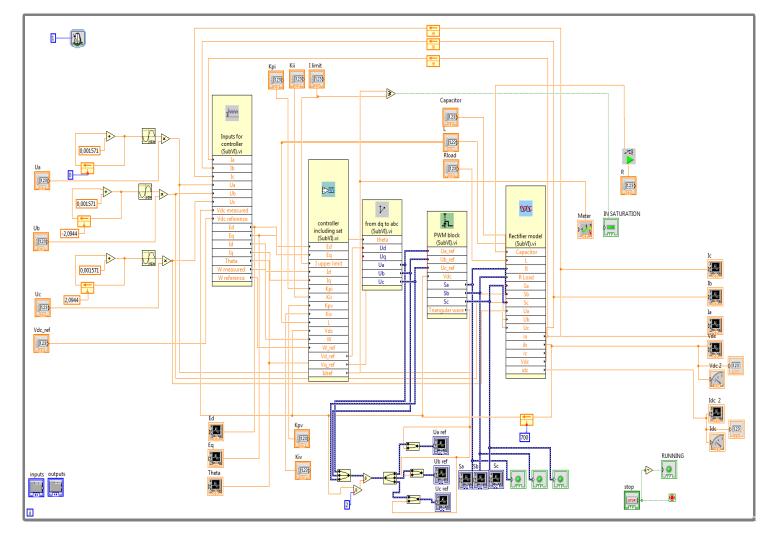

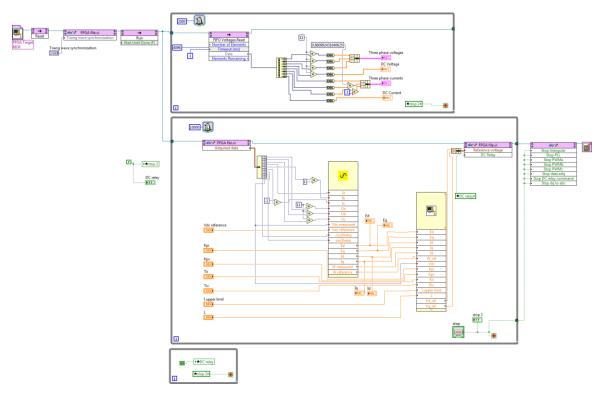

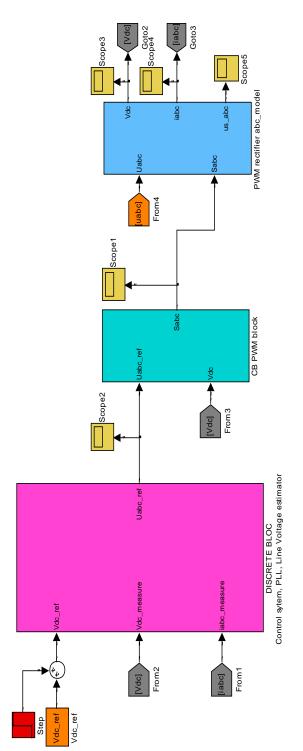

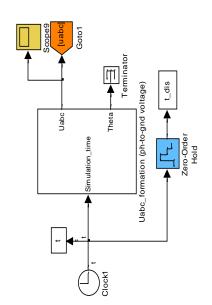

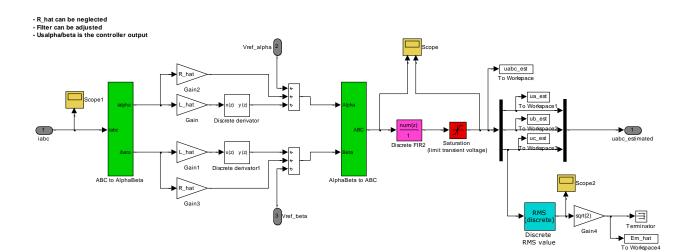

The complete system is shown in Figure 24, which contains all the simulation elements from the creation of the sinusoidal inputs to the rectifier model.

Figure 24: Overall view of all the simulation system.

| \$ <mark>₽₩₩₩</mark>     |                               |                                             |

|--------------------------|-------------------------------|---------------------------------------------|

| Inputs for<br>controller | Inputs                        | Outputs                                     |

| (SubVI).vi<br>Ia         | la                            | Ed                                          |

| Ib                       | Ib                            | Eq                                          |

| Ic                       | Ic                            | Id                                          |

| Ua<br>Ub                 | Uq                            | Iq                                          |

| Uc                       | Ub                            | Theta                                       |

| Vdc measured             | Uc                            | Wmeasured                                   |

| Vdc reference<br>Ed      | Vdc measured                  | Wreference                                  |

| Eq 🕨                     | Vdc medsured<br>Vdc reference | -                                           |

| Id  Iq Iq W measured     |                               | utputs for Inputs for the controller subVI. |

| W reference              |                               |                                             |

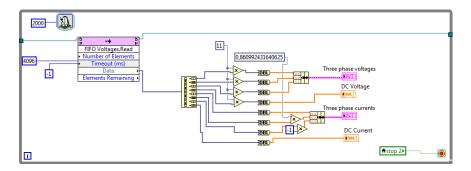

#### 4.1.1. Inputs for the controller block.

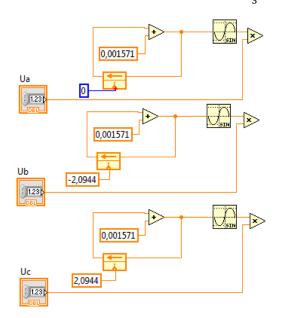

Figure 25: Inputs for controller block.

The main function of this block is to provide the appropriate inputs for the controller. For this purpose, it uses as inputs the currents and voltages of the system. The currents that are flowing through the system and the DC voltage through the load are calculated with a model of the rectifier and then used as inputs again in a loop. The three sinusoidal voltage waves have been created point by point in a discrete way (Figure 26). To do that, the phase of each wave is increased for every loop of the whole system and, by multiplying the sine of this angle by the amplitude, the sinusoidal wave is obtained. The initialization for the phase of Ub is -2,0944 radians, which is  $-\frac{2\pi}{3}$ , and, doing the same for Uc, the initial value of the phase is 2,0944 radians, which is  $\frac{2\pi}{3}$ .

Figure 26: Generation of three sinusoidal waves of voltage.

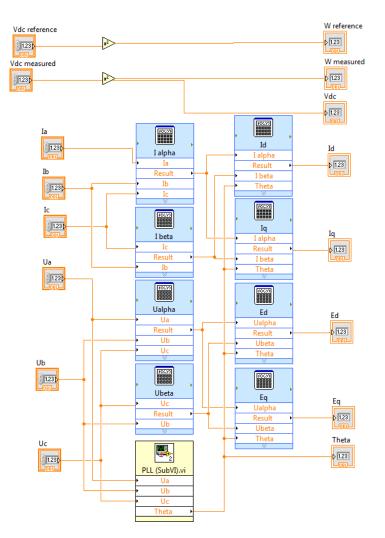

Inside the block different operations are made. The PLL, the "W measured" and "W reference" calculations, and the DQ transformations are achieved as shown in Figure 27.

Figure 27: Inputs for the controller block, inside view.

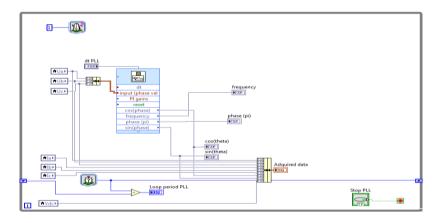

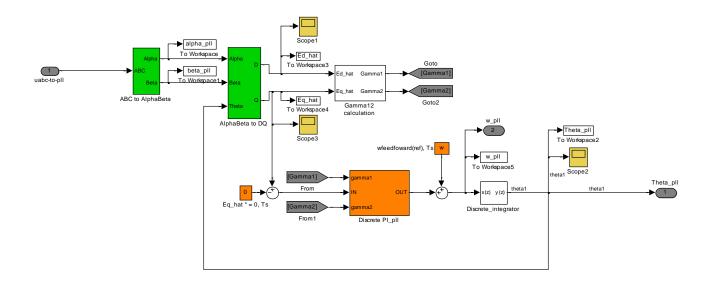

The Phase Locked Loop (PLL) is developed as a numeric method to calculate the electric angle of the three phase system, which is necessary for the d-q transformation following the Park's equations in chapter 2. According to [7] and [16] the PLL is designed.

$$\dot{\omega} = \gamma_1 \varepsilon \tag{4.1}$$

$$\dot{\theta} = \omega + \gamma_2 \varepsilon$$

where  $\gamma_1$  and  $\gamma_2$  are the gain parameters (ki and kp respectively) of the PI controller, which uses Eq as the error signal since a d-oriented control is used. In order to calculate gain parameters, the equations 4.2 are used.

$$\gamma_1 = \frac{\rho^2}{\hat{E}_g}, \qquad \gamma_2 = \frac{2\rho}{\hat{E}_g}, \qquad \hat{E}_g = \sqrt{\hat{E}_d^2 + \hat{E}_q^2}$$

(4.2)

where  $\rho$  is the bandwidth of the PLL in rad/s (in this case a frequency of 20 Hz is used) and  $\hat{E}_g$  is the grid voltage modulus. The PLL scheme is presented in Figure 28.

Figure 28: PLL theoretical implementation scheme.

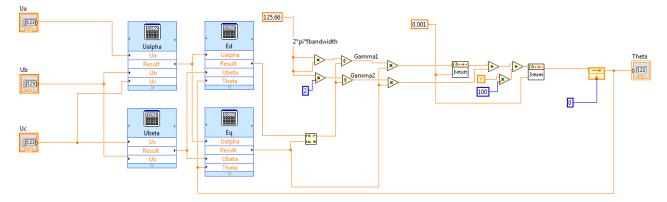

Following the steps mentioned before, the model is implemented using two discrete integrators, one for the PI controller and the other one to obtain the electric angle from the angular speed. The integration step used in the program is 0,001s as can be checked in the Labview scheme shown in Figure 29.

Figure 29: PLL Implementation in Labview.

## 4.1.2. Controller block.

|                                               | Inputs                      | Outputs                   |

|-----------------------------------------------|-----------------------------|---------------------------|

|                                               | Ed                          | Vd_ref                    |

|                                               | Eq                          | Vq_ref                    |

| ► Ed                                          | I upper limit               | Idref                     |

| <ul> <li>Eq</li> <li>I upper limit</li> </ul> | Id                          | -                         |

| ► Id                                          | Iq                          | -                         |

| ► Iq<br>► Kpi                                 | Крі                         | -                         |

| ► Kii<br>► Kpv                                | Kii                         | -                         |

| <ul> <li>Kiv</li> </ul>                       | Крv                         | -                         |

| ► L<br>► Vdc                                  | Kiv                         | -                         |

|                                               | L                           | -                         |

| Vd_ref •                                      | Vdc                         | -                         |

| Vq_ref •<br>Idref •                           | W                           | -                         |

|                                               | W_ref                       | -                         |

| Figure 30:controller block.                   | Table 9: Inputs and outputs | for the controller subVI. |

|                                               |                             |                           |

| DC-link voltage                               |                             | Current                   |

| Kiv                                           | Кіі                         | controller                |

| controller                                    |                             |                           |

|                                               | ANTI WINDUP FEEDBACK        | ANTI_WINDUP FEEDBACK      |

| Isat-I                                        | V-Vsat                      |                           |

|                                               |                             |                           |

| W_ref                                         |                             |                           |

|                                               | Idref                       |                           |

|                                               |                             |                           |

| Id_ref_b4sat                                  |                             |                           |

|                                               |                             | Vd_ref                    |

|                                               |                             | Vdb4saturation            |

| Id                                            |                             | Vqb4saturation Vq_ref     |

| Current saturation                            | wLlq                        |                           |

|                                               | wLId                        | Voltage saturation        |

|                                               |                             |                           |

| Iq                                            |                             |                           |

|                                               |                             | Vq_ref                    |

|                                               | V-Vsat                      |                           |

|                                               | - Interes                   |                           |

|                                               |                             |                           |

|                                               |                             |                           |

|                                               |                             |                           |

|                                               |                             |                           |

| Kpv                                           | X                           | Fa Vdr                    |

|                                               | Kpi                         | Eq Vdc                    |

|                                               | [][23]<br>Idref             |                           |

|                                               |                             |                           |

|                                               | -                           |                           |

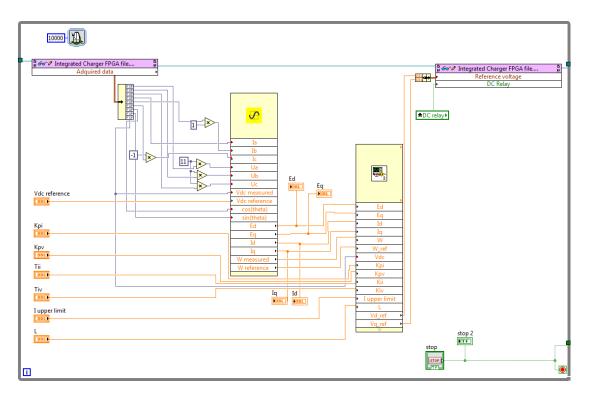

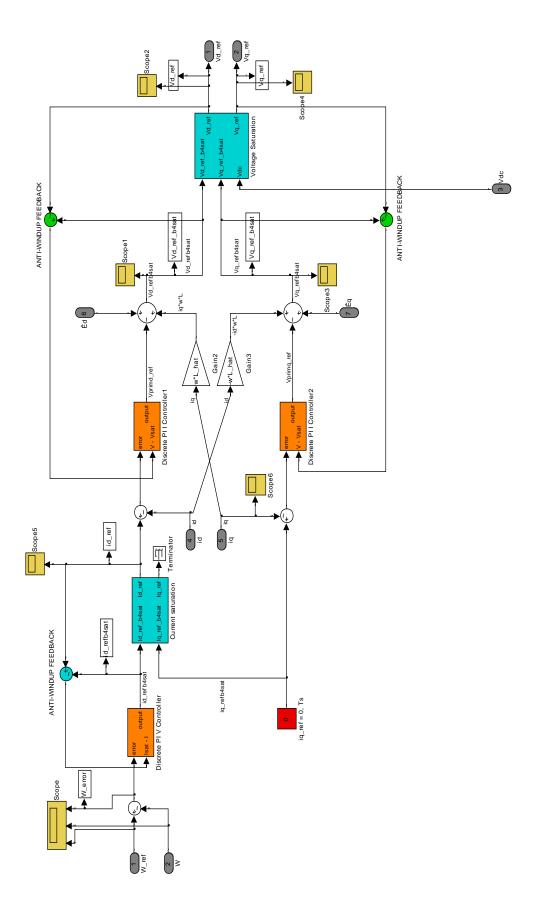

Figure 31: Inside view of the controller block.

#### 4.1.2.1. DC-link voltage controller.

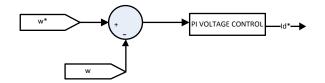

The ultimate goal of the controller is to obtain a desired voltage in the DC-link. By measuring the instantaneous voltage and comparing its square value with the square value of the reference voltage, an error that is fed to the controller is obtained.

$$\varepsilon = W_{ref} - W = V_{dc\,ref}^2 - V_{dc}^2 \tag{4.3}$$

By implementing a PI control, a reference current for the system,  $id^*$ , is calculated [3].

$$I_d^* = k_p \varepsilon + k_i \frac{\varepsilon}{s} \tag{4.4}$$

The PI control parameters are calculated as detailed in [2].

$$K_{pv} = \frac{\alpha_v C}{3E_m} \quad \text{and} \quad K_{iv} = 0,01 \tag{4.5}$$

where we choose  $\alpha_v$  two decades smaller than the switching frequency  $\alpha_v = \frac{2\pi f_{Sw}}{100}$ .

If there is a considerable difference between the reference DC voltage and the measured DC voltage, this results in an unacceptably high reference current calculated by the controller, which has to be limited. Therefore a saturation block is used.

Figure 32: DC –link voltage controller

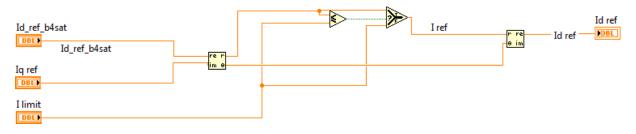

#### • Current saturation.

In order to protect the inverter, which maximum rms current allowed is 30A, there is a need to add a limitation. The saturation control is carried out with the current Id module in such a way that the upper and the lower limit are controlled at the same time.

Figure 33: Implementation of the current saturation.

#### • Anti-windup Integrator.

In practically all controllers, there are nonlinear effects that must be accounted to achieve a good and realistic control. Windup is a phenomena caused by the interactions between integral action and saturations [17]. To avoid the integrator of the control calculating a high current over the limit, the difference between the current calculated and the limit is fed back to reduce the error going inside the integral part of the controller. The new error is  $\bar{\varepsilon}$  and the current calculated by the PI control is referred as  $\bar{I}_d^*$ . The new equations of the PI control with anti-windup loop are given below [3].

$$\bar{\varepsilon} = \varepsilon + \frac{\overline{I_d^* - I_d^*}}{k_p}$$

$$I_d^* = k_p \varepsilon + k_i \frac{\bar{\varepsilon}}{s}$$

(4.6)

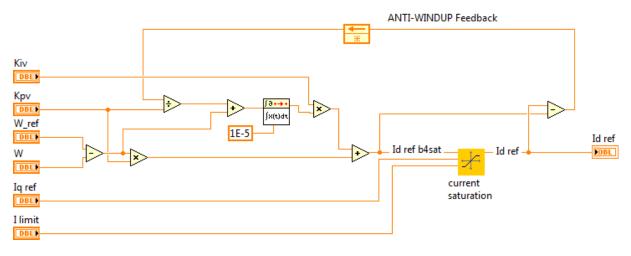

The complete scheme of the DC-link voltage controller implemented in Labview is shown in Figure 34.

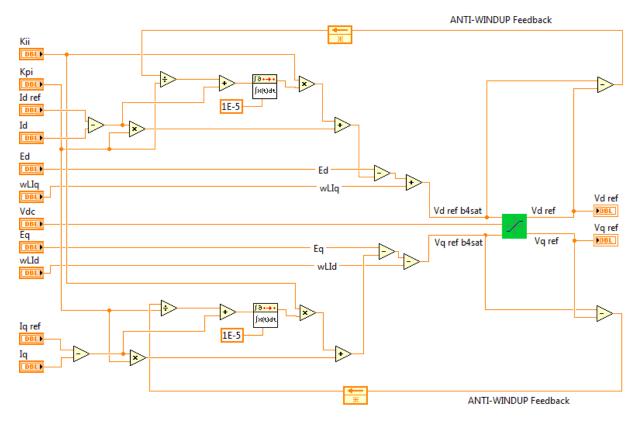

#### 4.1.2.2. Current controller.

Once a DC-link voltage control is established, the reference current  $I_d^*$ , which is used to control the DC voltage, is calculated. In addition, due to the unit power factor operation of the system, the q-axis reference current  $I_q^*$  is set to zero. To obtain these reference currents in the system, a current control is performed, resulting in a reference voltage which is calculated in the dq-axis system. The implementation of the controller is done in two PI control loops, one for each component of the current,  $I_d^*$  and  $I_q^*$ . The outputs of the two PI controls are  $V_d^*$  and  $V_q^*$  respectively. The components of this reference voltage are calculated using [3].

$$V_{d}^{*} = E_{d} - k_{p}\varepsilon_{d} - k_{i}\frac{\varepsilon_{d}}{s} + \omega LI_{q} \qquad \text{being } \varepsilon_{d} = I_{d}^{*} - I_{d}$$

$$V_{q}^{*} = E_{q} - k_{p}\varepsilon_{q} - k_{i}\frac{\varepsilon_{q}}{s} - \omega LI_{d} \qquad \text{being } \varepsilon_{q} = I_{q}^{*} - I_{q} \qquad (4.7)$$

Figure 35: Current controller block diagram.

The PI control parameters are calculated as detailed in [2].

$$K_{pi} = \alpha_i L$$

and  $K_{ii} = \alpha_i R$  (4.8)

where we choose  $\alpha_i$  a decade smaller than the switching frequency  $\alpha_i = \frac{2\pi f_{sw}}{10}$ .

As in the case of the DC-link voltage controller, a saturation block is needed to keep the outputs in a defined range.

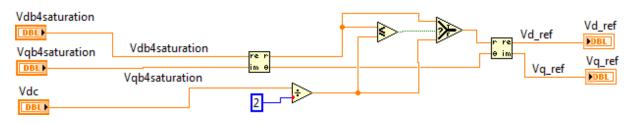

• Voltage saturation.

As explained in the chapter 2.1., using a sinusoidal PWM, the maximum reference value that can be used is  $V_{dc}/2$  [18]. Therefore, the saturation block calculates the modulus of the reference voltage and compares it with  $V_{dc}/2$ . In case the value of the reference voltage is higher, it is limited to  $V_{dc}/2$ . The components  $V_d^*$  and  $V_q^*$  after saturation are then recalculated using the original phase of the reference voltage, as shown in Figure 36.

Figure 36: Voltage saturation block.

#### • Anti-windup Integrator.

As explained for the DC-link voltage controller, there is a risk of obtaining a too high reference voltage at the output of the controller due to the action of the integrator. To avoid this uncontrollable increase of the voltage an integrator with anti-windup is used. The difference

between the voltage calculated by the Pi controller and the voltage limit is fed back to the integrator to reduce the value of the output reference voltage. The equations of the components of the reference voltage with an anti-windup integrator are obtained using equations from [3]:

$$V_{d}^{*} = E_{d} - k_{p}\varepsilon_{d} - k_{i}\frac{\overline{\varepsilon_{d}}}{s} + \omega LI_{q} \qquad \text{being } \varepsilon_{d} = I_{d}^{*} - I_{d} \text{ and } \overline{\varepsilon_{d}} = \varepsilon_{d} + \frac{V_{d}^{*} - \overline{V_{d}^{*}}}{k_{p}} \qquad (4.9)$$

$$V_{q}^{*} = E_{q} - k_{p}\varepsilon_{q} - k_{i}\frac{\overline{\varepsilon_{q}}}{s} - \omega LI_{d} \qquad \text{being } \varepsilon_{q} = I_{q}^{*} - I_{q} \text{ and } \overline{\varepsilon_{q}} = \varepsilon_{q} + \frac{V_{q}^{*} - \overline{V_{q}^{*}}}{k_{p}}$$

The complete scheme of the current controller with an anti-windup integrator implemented in Labview is presented in Figure 37.

Figure 37: Current controller.

#### from dq to abc (SubVI).vi theta Ud Uq Ua Ub Uc V

| Inputs | Outputs |

|--------|---------|

| theta  | Ua      |

| Ud     | Ub      |

| Uq     | Uc      |

Table 10: Inputs and outputs of From dq to abc subVI.

Figure 38: From dq to abc block.

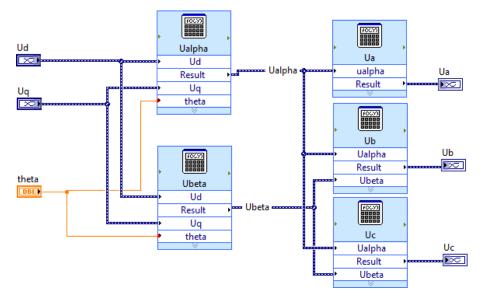

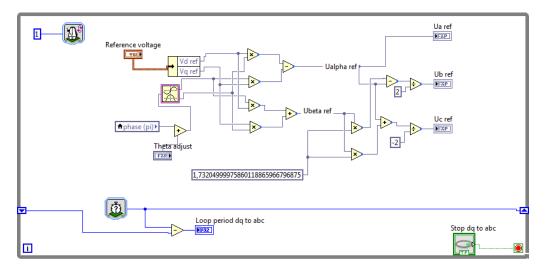

The output of the decoupled controller is a reference voltage whose components are expressed in dq-axes. Since the input of the PWM block is a reference voltage expressed in abc axes, a transformation block is needed. The transformation is done using the equations 4.8 and 4.9.

$$U_{\alpha} = V_d \cos \theta - V_q \sin \theta$$

$$U_{\beta} = V_d \sin \theta + V_q \cos \theta$$

(4.10)

$$U_{a} = U_{\alpha}$$

$$U_{b} = -\frac{1}{2}U_{\alpha} + \frac{\sqrt{3}}{2}U_{\beta}$$

$$U_{b} = -\frac{1}{2}U_{\alpha} - \frac{\sqrt{3}}{2}U_{\beta}$$

$$(4.11)$$

These equations are implemented in Labview and shown in Figure 38.

Figure 39: DQ-to-ABC transformation block.

### 4.1.3. DQ-to-ABC transformation block.

|      | Ł         |     |

|------|-----------|-----|

| ۱.   | Ua_ref    |     |

| •    | Ub_ref    |     |

| ۱.   | Uc_ref    |     |

| ۱.   | Vdc       |     |

|      | Sa        | •   |

|      | Sb        | •   |

|      | Sc        | •   |

| Tria | ngular wa | ave |

| 4.1.4. | Sinusoidal | pulse | width | modulation | block. |

|--------|------------|-------|-------|------------|--------|

|--------|------------|-------|-------|------------|--------|

| Inputs                                       | Outputs         |  |

|----------------------------------------------|-----------------|--|

| Ua_ref                                       | Sa              |  |

| Ub_ref                                       | Sb              |  |

| Uc_ref                                       | Sc              |  |

| Vdc                                          | Triangular wave |  |

| Table 11: Inputs and outputs for SPWM subVI. |                 |  |

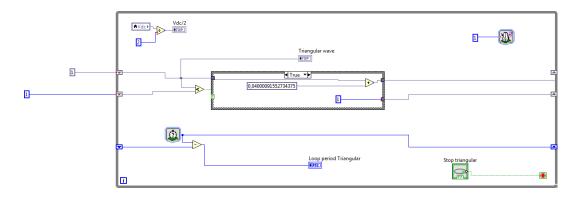

Figure 40:SPWM block.

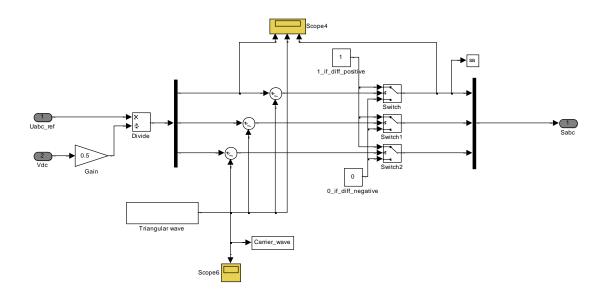

PWM modulation is based on the comparison between the three sinusoidal reference voltage waves and a triangular carrier wave. Using this comparison, three pulse signals, Sa, Sb and Sc, are created in order to define the duty cycles of the IGBT's.

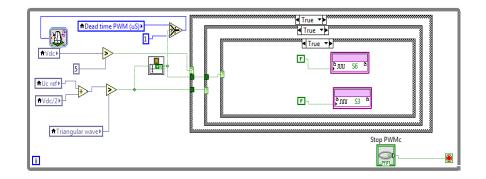

The PWM block was created in Labview as shown in Figure 41.

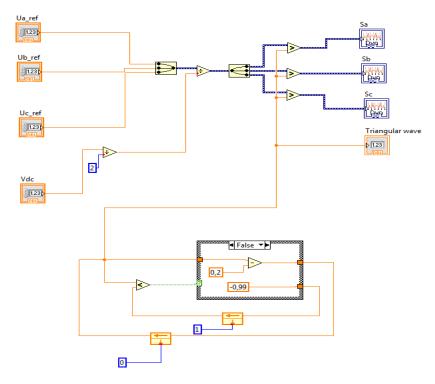

Figure 41: SPWM block, inside view.

The triangular wave is created by dividing the period of the signal according with the switching frequency into the number of discrete points that are necessary. Using the number of discrete points needed, the increment of the amplitude is calculated to achieve a triangular wave with unitary value.

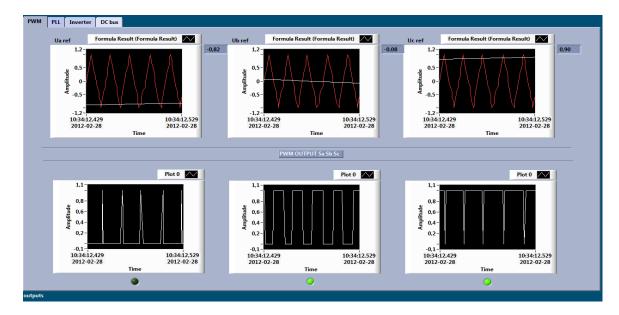

The front panel of this VI shows the comparison between the triangular wave and the three sinusoidal voltages in the upper part, and the three switching patterns of Sa, Sb and Sc in the lower

part. The switching frequency is 10 kHz, and the sampling frequency used to generate the triangular wave and compare it with the control signal is 200 kHz, that is, 20 points per switching period.

Figure 42: PWM front panel.

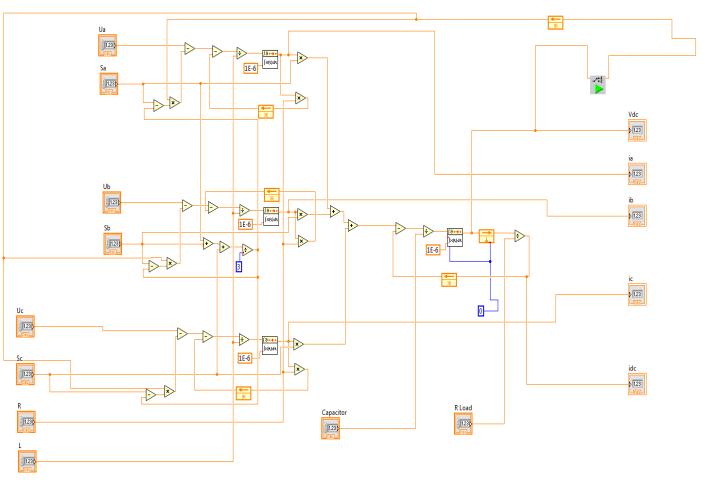

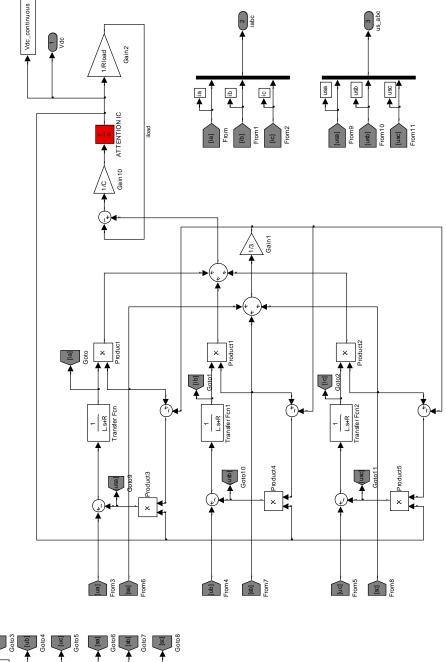

#### 4.1.5. Rectifier model block.

| 12712                      |             |                                           |

|----------------------------|-------------|-------------------------------------------|

| Rectifier model            | Inputs      | Outputs                                   |

| (SubVI).vi<br>Capacitor    | Capacitance | ia                                        |

|                            | L           | ib                                        |

| ► R                        | R           | ic                                        |

| <ul> <li>R Load</li> </ul> | R Load      | Vdc                                       |

| ► Sa                       | Sa          | Idc                                       |

| ▶ Sb                       | Sb          | -                                         |

| ► Sc                       | Sc          | -                                         |

| ► Ua                       | Ua          | -                                         |

| ▶ Ub                       | Ub          | -                                         |

| ► Uc                       | Uc          | -                                         |

| ia 🔸                       |             | nd outputs for the rectifier model subVI. |

| ib 🔸                       |             |                                           |

| ic 🔸                       |             |                                           |

| Vdc 🔸                      |             |                                           |

| idc 🕨                      |             |                                           |

Figure 43: Rectifier model block.

According to [4], a rectifier model can be implemented using only three switches (Sa, Sb and Sc) by determining the voltage applied depending on the ON/OFF state of the switches. For simulations it is accepted that, in the

same leg of the inverter, one switch is always ON while the other one is OFF. However, in the implementation chapter it is explained that a dead time between commutations is used to avoid short circuits in the same leg.

$$u_{Sab} = (Sa - Sb) u_{dc}$$

$$u_{Sbc} = (Sb - Sc) u_{dc}$$

$$u_{Sca} = (Sc - Sa) u_{dc}$$

(4.12)

where Sa, Sb and Sc represent the state of the three top switches, one for each leg of the inverter. The value of Sa, Sb and Sc is "1" if the corresponding switch is On and "0" if the switch is OFF.

$$u_{Sa} = f_a \cdot u_{dc}$$

$$u_{Sb} = f_b \cdot u_{dc}$$

$$u_{Sc} = f_c \cdot u_{dc}$$

(4.13)

where fa, fb and fc are calculated as follows.

$$f_{a} = S_{a} - S^{*} = S_{a} - \frac{1}{3}(S_{a} + S_{b} + S_{c}) = \frac{2S_{a} - (S_{b} + S_{c})}{3}$$

$$f_{b} = \frac{2S_{b} - (S_{a} + S_{c})}{3}$$

$$f_{c} = \frac{2S_{c} - (S_{a} + S_{b})}{3}$$

(4.14)

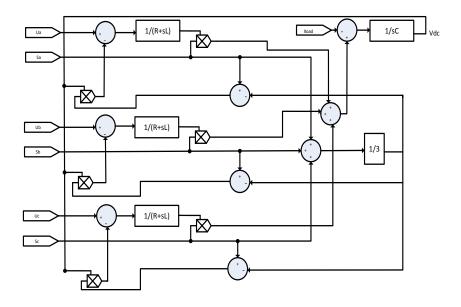

Using the equations of a rectifier, one for each leg, the model of the rectifier is implemented for the simulations (Figure 44).

$$\begin{bmatrix}

u_{a} \\

u_{b} \\

u_{c}

\end{bmatrix} = R \begin{bmatrix}

i_{a} \\

i_{b} \\

i_{c}

\end{bmatrix} + L \frac{d}{dt} \begin{bmatrix}

i_{a} \\

i_{b} \\

i_{c}

\end{bmatrix} + \begin{bmatrix}

u_{Sa} \\

u_{Sb} \\

u_{Sc}

\end{bmatrix}$$

$$C \frac{du_{dc}}{dt} = S_{a}i_{a} + S_{b}i_{b} + S_{c}i_{c} - i_{load}$$

(4.15)

Figure 44: Rectifier theoretical scheme.

Implementing this model in Labview, the rectifier model obtained is shown in Figure 45.

Figure 45: Rectifier Labview implementation.

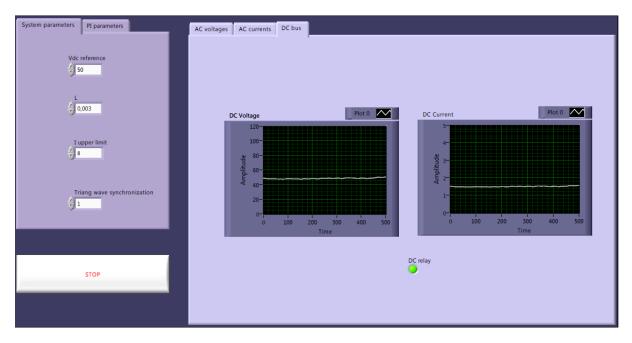

## 4.2. Simulation procedure.

This part of the chapter includes a detailed explanation of how the simulation is developed. At the beginning all the relays and switches are off and the connection sequence is done as shown in Figure 46.

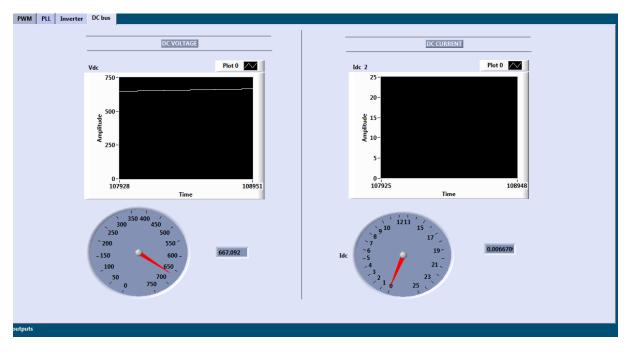

Figure 46: Start up procedure in the simulation.

1. With the relays open and the Sa, Sb and Sc switches (and the corresponding switches of the same legs) in OFF state, the system acts like a diode rectifier raising the DC voltage until it reaches the peak value of the line voltage. With a 400 V line-to-line supply, the DC voltage should reach a maximum value of 560 V minus the losses on each line, which is approximately 500V. As shown in Figure 47, the current is very low because the load is disconnected and the current is flowing through a high resistance in parallel with the load.

Figure 47: DC bus control with diode rectifier.

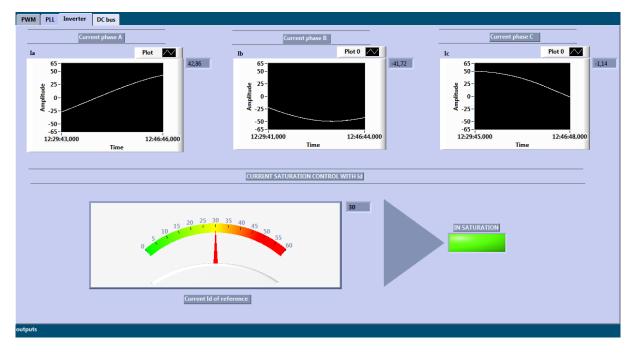

2. In the simulation, once the DC voltage reaches 500 V, the inrush current limiter is bypassed and the PWM signals start to be transmitted until the control raises the DC voltage up to the reference value. During this period of rise, the d-axis component of the reference current saturates at 30A and the AC currents are higher than in the steady state (Figure 48).

Figure 48: Inverter front panel with PWM controlling in saturation.

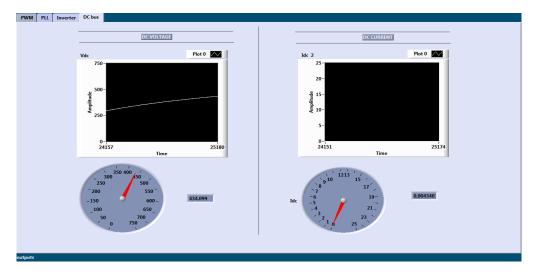

During this period, the load is still disconnected and consequently, the DC current is very low (see Figure 49).

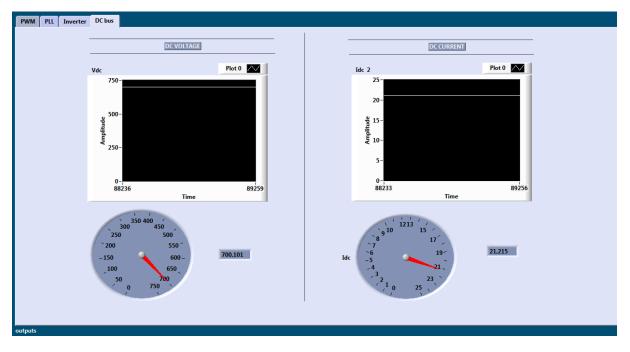

Figure 49: DC bus front panel with PWM controlling in saturation.

3. When the system is under control, after the DC voltage reaches 700V, the load is connected producing a raise of the DC current up to its steady state value, which provides the 15 kW required (see Figure 50).

Figure 50: DC bus front panel in steady state.

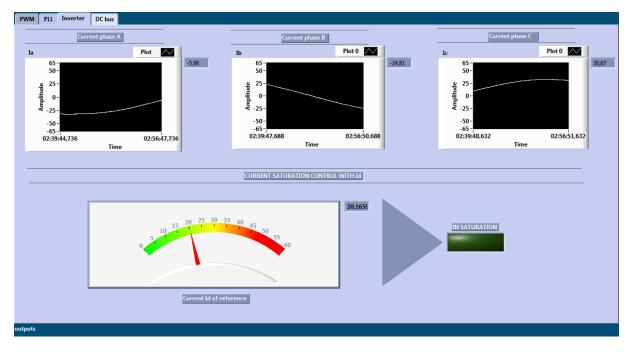

During steady state, the currents are stable and the d-axis component of the reference current does not saturate anymore, as shown in Figure 51.

Figure 51: Inverter front panel in steady state.

# Chapter 5.Hardware implementation.

In this chapter all the hardware used is explained as well as the CompactRIO programming.

### 5.1. System composition.

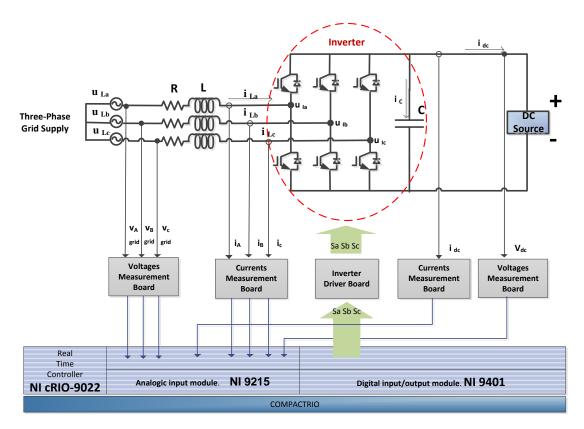

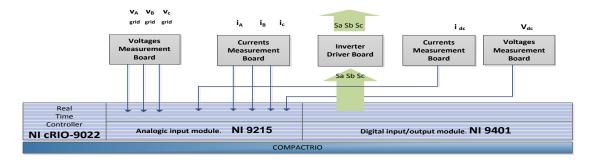

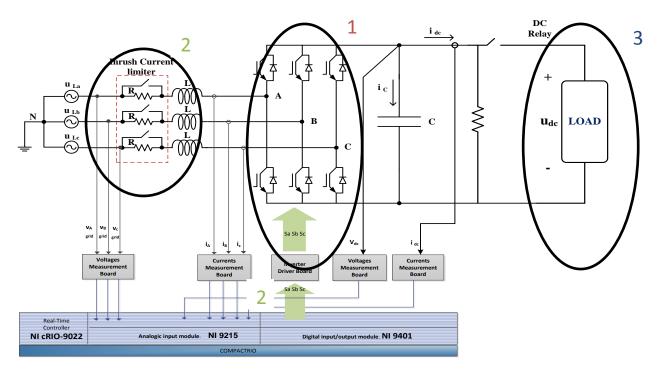

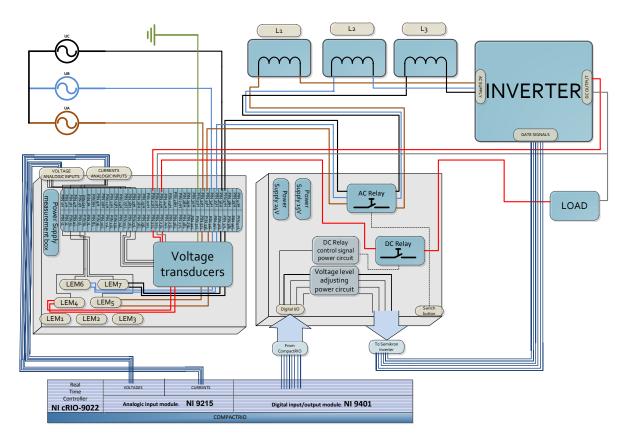

The system implemented follows the schematic shown in Figure 52.

Figure 52: Complete system schematic.

This system is composed by:

- AC voltage supply.

- Three inductors of 3mH.

- The measurement box.

- The box containing the DC sources and the relays.

- The inverter with the load connected on the DC side.

- The CompactRIO device.

Figure 53: General overview of the complete system.

#### 5.1.1. AC voltage supply.

Because of the diameter of the existent wires in the measurement box, the voltage level has to be lowered in order to be able to use the measurement box that already exists and operate within safety limits.

To provide the new voltage level, an autotransformer is placed in the lab providing the power level needed and also isolation between the set up and the grid.

Finally, the voltage level used is 20 V line-to-line.

Figure 54: View of the three-phase autotransformer.

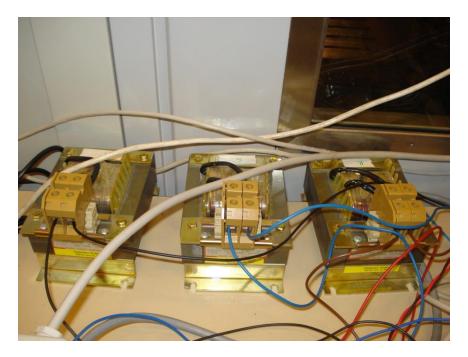

#### 5.1.2. Inductors.

After the calculations made in the design chapter and taking into consideration the ripple for the current and the limit needed in the voltage, the inductors were chosen with a value of 3mH.

Figure 55: View of the inductors.

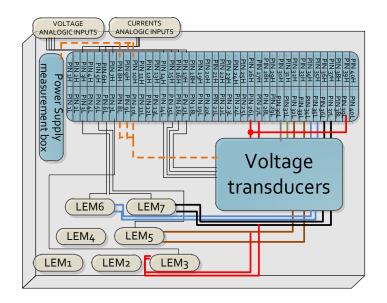

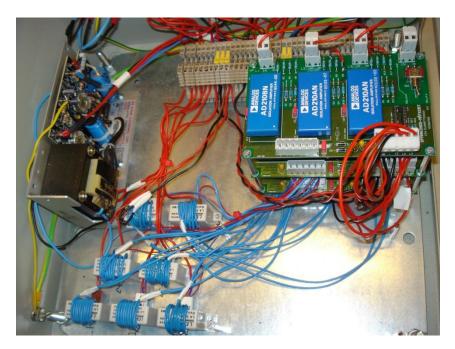

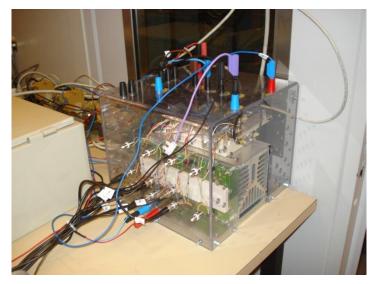

#### 5.1.3. Measurement box.

The measurement box includes:

- DC voltage source of 15V in order to feed the LEMs and the UMAT2.

- Three voltage transducers UMAT2 with three channels each one.

- Seven current sensors LEM LA 50-S but only four of them in use.

The measurement box is used to measure the voltage and the currents that are needed to control the system. For this reason, 8 measures are taken, 4 for the voltages and 4 for the currents. The following Figure 56 shows where the measures are taken.

The four LEM LA 50-S/SP1 current measuring modules are used providing galvanic isolation between the primary and the secondary circuits as already explained in the design chapter. These modules are used also to measure the DC current because of a high frequency power transmission that allows the modules to measure all kinds of currents. As explained in the design chapter, the resulting current goes through a resistor to induce a voltage drop that can be read by the analogic inputs of the CompactRIO device.

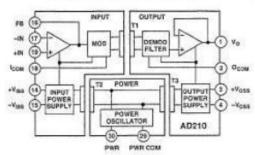

The voltage measurements are taken by three voltage transducers UMAT2 but only two of them are in use. The three channels of one of them are used to measure the three AC phase voltages and only one channel of the other one is used to measure the DC voltage. In order to measure the voltages, the voltage goes through a voltage divider previously calculated in the design chapter. After that, the reduced signal goes to the AD210, which is an isolated amplifier.

Figure 56: Definition of the points where the measures are taken.

As can be checked in the measurement box connections in Figure 57, to measure the voltage and current of each phase, the wire coming from the voltage source is connected to a pin which output is connected to the two different measurement circuits: the voltage measurement circuit connected in parallel and the current measurement circuit connected in series.

Figure 57: Measurement box schematic.

Figure 58: View of the measurement box.

The Table 13 details all the pins in use in the measurement box and which signal or wire is connected to each of them.

| PIN       | CONNECTED TO           | PIN | CONNECTED TO                     | PIN | CONNECTED TO                 |

|-----------|------------------------|-----|----------------------------------|-----|------------------------------|

| 1H        | Analog output Idc      | 14L | Lower Volt. Trans. Output (L3)   | 28H | Not in use                   |

| 1L        | LEM 4 output           | 15H | Analog output Va                 | 28L | Not in use                   |

| 2H        | Not in use             | 15L | Mid volt. Trans.outp. L1         | 29H | Not in use                   |

| <b>2L</b> | Not in use             | 16H | Analog output Vb                 | 29L | Not in use                   |

| 3H        | Not in use             | 16L | Mid volt. Trans.outp. L2         | 30H | Vdc-                         |

| 3L        | Not in use             | 17H | Analog output Vc                 | 30L | Low volt. Trans Input (N)    |

| 4H        | Not in use             | 17L | Mid volt. Trans.outp. L3         | 31H | Not in use                   |

| 4L        | Not in use             | 18H | Not in use                       | 31L | Not in use                   |

| 5H        | Analog output Ia       | 18L | Not in use                       | 32H | PhasevoltageUa               |

| 5L        | LEM 5 output           | 19H | Not in use                       | 32L | MId volt.TransInputL1 &LEML5 |

| 6H        | Analog output Ib       | 19L | Not in use                       | 33H | AC Relay input phase A       |

| 6L        | LEM 6 output           | 20H | Not in use                       | 33L | LEM L5 return                |

| 7H        | Analog output Ic       | 20L | Not in use                       | 34H | PhasevoltageUb               |

| 7L        | LEM 3 output           | 21H | Vdc+                             | 34L | MId volt.TransInputL2 &LEML6 |

| 8H        | -15V                   | 21L | Low volt. Trans Input L3 & LEM 4 | 35H | AC Relay input phase B       |

| 8L        | Transducerssupply      | 22H | Vdc-                             | 35L | LEM L6 return                |

| 9H        | 0V                     | 22L | Lower Volt. Trans. Input (N)     | 36H | PhasevoltageUc               |

| 9L        | Transducersupply (GND) | 23H | DC Relay Input                   | 36L | Mid volt.TransInput L3       |

| 10H       | +15V                   | 23L | LEM L4return                     | 37H | Not in use                   |

| 10L       | Transducerssupply      | 24H | Not in use                       | 37L | Not in use                   |

| 11H       | Not in use             | 24L | Not in use                       | 38H | Not in use                   |

| 11L       | Not in use             | 25H | Not in use                       | 38L | Not in use                   |

| 12H       | Not in use             | 25L | Not in use                       | 39H | Vdc+                         |

| 12L       | Not in use             | 26H | PhasevoltageUc                   | 39L | Upper volt. Trans Input L2   |

| 13H       | Not in use             | 26L | LEM L3                           | 40H | Not in use                   |

| 13L       | Not in use             | 27H | AC Relay input phase C           | 40L | Not in use                   |

| 14H       | Analog output Vdc      | 27L | LEM L3 return                    | -   |                              |

Table 13: Pin terminal connections inside the measurement box.

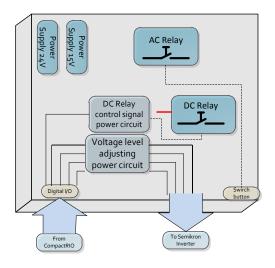

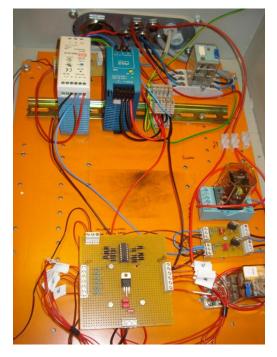

#### 5.1.4. The DC sources and relays box.

The DC sources and relays box includes (See Figure 59):

- A 15 Vdc voltage source that feeds the inverter and the electronic board that adjusts to an appropriate voltage level the TTL gate signals to control the inverter.

- A 24 Vdc voltage source that feeds the AC and DC relays.

- An AC relay (C3-A 30) for the connection of the system to the grid.

- A DC relay to connect the load to the rectifier.

- An electronic board to drive the DC relay.

- An electronic board to drive the AC relay.

- An electronic board to adjust the TTL gate signals voltage level to 15 V, which is the required voltage level of the gate signals in the inverter.

Figure 59: DC sources and relays box.

Figure 60: View of the DC sources and relays box.

#### 5.1.5. Inverter and load.

The inverter used for this system is a Semikron inverter AN-8005. The control of the inverter switching is carried out by SPWM pulses generated by the CompactRIO device, with 10 kHz frequency. The connection between the inverter's control circuit and CompactRIO is done by a 25-pin D type connector that transmits six PWM signals, as well as one more command signal to connect the load in the DC side.

Figure 61: View of the Semikron inverter AN-8005.

The load value is 33 Ohms, as calculated in the design chapter. That way, even after changing the voltage level, the current and the voltage are reduced in the same ratio. To obtain the required load, a potentiometer of 47 Ohms is used. It is adjusted at 70% of the total resistance to achieve the 33 Ohms required for the system.

Figure 62: View of the potentiometer.

#### 5.1.6. CompactRIO.

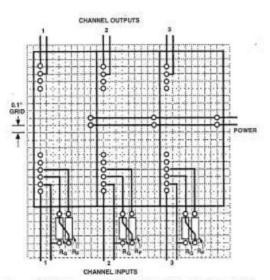

CompactRIO is a reconfigurable control and acquisition system. The CompactRIO system's architecture includes I/O modules, a reconfigurable FPGA chassis, and an embedded controller. The CompactRIO has been programmed with Labview graphical programming tools [8]. In this thesis the compactRIO system used is composed by the following elements:

- A real-time controller NI cRIO 9022.

- 2 analog input modules NI 9215 with BNC connectors.

- An analog output module NI 9263 (not used).

- 2 digital input/output modules NI 9401 (only one in use).

Figure 63: View of the compactRIO system.