# Formal Verification of UML-RT Capsules using Model Checking

Master of Science Thesis in Secure and Dependable Computer Systems

MATS CARLSSON LARS JOHANSSON

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Göteborg, Sweden, June 2009 The Author grants to Chalmers University of Technology and University of Gothenburg the non-exclusive right to publish the Work electronically and in a non-commercial purpose make it accessible on the Internet. The Author warrants that he/she is the author to the Work, and warrants that the Work does not contain text, pictures or other material that violates copyright law.

The Author shall, when transferring the rights of the Work to a third party (for example a publisher or a company), acknowledge the third party about this agreement. If the Author has signed a copyright agreement with a third party regarding the Work, the Author warrants hereby that he/she has obtained any necessary permission from this third party to let Chalmers University of Technology and University of Gothenburg store the Work electronically and make it accessible on the Internet.

Formal Verification of UML-RT Capsules using Model Checking

Mats Carlsson Lars Johansson

- ©MATS CARLSSON, June 2009.

- ©LARS JOHANSSON, June 2009.

Examiner: Wolfgang Ahrendt

Department of Computer Science and Engineering Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone + 46 (0)31-772 1000

Department of Computer Science and Engineering Göteborg, Sweden, June 2009

#### Abstract

Formal verification methods have successfully been used to ensure correctness of both hardware and software systems. In contrast to testing methods, that can demonstrate the presence of faults in a system, formal methods can prove their absence.

A department of the telecommunications company Ericsson AB in Gothenburg, Sweden, uses the UML-RT language to model software used in WCDMA radio base stations. These concurrent and reactive systems can be modeled in the Eclipse-based RSARTE environment.

Previous work underlines a need of narrowing the gap between software development tools used in industry and formal verification tools. This thesis examines the feasibility of using model checking to verify properties of UML-RT capsules. We present a prototype tool for generating verification models in the Promela language for the model checker Spin. The tool is implemented as a model-to-text transformation using the JET tool and is integrated into RSARTE.

The result of the work establishes that it, for a subset of constructs in UML-RT, is possible to automate generation of verification models that can be used to demonstrate properties of the original UML-RT capsules. We demonstrate this with example models created in RSARTE.

**Keywords** formal verification, model checking, model-to-text, Promela, RSARTE, Spin, UML-RT.

#### Sammanfattning

Formella verifieringsmetoder har med framgång använts för att säkerställa korrekthet av både hårdvaru- och mjukvarusystem. Till skillnad från testmetoder, vilka enbart kan visa förekomst av fel i system, kan formella metoder bevisa frånvaron av dessa.

En avdelning på telekommunikationsföretaget Ericsson AB i Göteborg använder modelleringsspråket UML-RT för att modellera mjukvara för användning i radiobasstationer för WCDMA. Dessa parallella och reaktiva system kan modelleras i den Eclipse-baserade utvecklingsmiljön RSARTE.

Tidigare arbeten understryker ett behov av att minska avståndet mellan industriella mjukvaruutvecklingsverktyg och verktyg för formell verifiering. Detta arbete utforskar möjligheten att använda model checking för att verifiera egenskaper hos UML-RT-kapslar. Vi presenterar ett prototypverktyg för att generera verifieringsmodeller i språket Promela, som används av model checkingverktyget Spin. Prototypverktyget är implementerat i form av en model-to-text-transformation med hjälp av verktyget JET och är integrerat i RSARTE.

Resultatet av arbetet fastställer att det, för en delmängd av byggstenarna i UML-RT, är möjligt att automatisera framställning av verifieringsmodeller, som därefter kan användas för att påvisa egenskaper hos de ursprungliga UML-RT-kapslarna. Vi demonstrerar detta med hjälp av ett antal exempelmodeller som skapats med RSARTE.

**Sökord** formell verifiering, model checking, model-to-text, Promela, RSARTE, Spin, UML-RT.

# Preface

This report is the result of a Master of Science thesis project in the program Secure and Dependable Computer Systems at Chalmers University of Technology in Gothenburg, Sweden. The work has been conducted between February and June of 2009 for Ericsson AB, at a department developing application software for WCDMA radio base stations.

The examiner for the thesis has been Dr. Wolfgang Ahrendt from the Department of Computer Science and Engineering at Chalmers University of Technology, whose advice and support we gratefully acknowledge. Our supervisors at Ericsson have been Anders Borghed, Peter Eriksson and Sebastian Holmgren, all of whom have provided much appreciated support, guidance and encouragement throughout our work.

# Contents

| P        | refac                                                   | e                                              | $\mathbf{V}$ |  |  |  |

|----------|---------------------------------------------------------|------------------------------------------------|--------------|--|--|--|

| 1        | Intr                                                    | roduction                                      | 1            |  |  |  |

|          | 1.1                                                     | Background                                     | 2            |  |  |  |

|          | 1.2                                                     | Aim                                            | 3            |  |  |  |

|          | 1.3                                                     | Limitations                                    | 3            |  |  |  |

|          | 1.4                                                     | Disposition                                    | 4            |  |  |  |

| <b>2</b> | The                                                     | eory                                           | 5            |  |  |  |

|          | 2.1                                                     | Formal Verification                            | 5            |  |  |  |

|          | 2.2                                                     | Model Checking                                 | 6            |  |  |  |

|          |                                                         | 2.2.1 Model checking workflow                  | 6            |  |  |  |

|          | 2.3                                                     | The Spin model checker                         | 7            |  |  |  |

|          |                                                         | 2.3.1 The Promela specification language       | 8            |  |  |  |

|          |                                                         | 2.3.2 A Promela example                        | 8            |  |  |  |

|          |                                                         | 2.3.3 Property specification in Spin using LTL | 10           |  |  |  |

|          |                                                         | 2.3.4 LTL property verification                | 11           |  |  |  |

|          |                                                         | 2.3.5 Problem space reduction                  | 11           |  |  |  |

| 3        | Me                                                      | thod                                           | 13           |  |  |  |

|          | 3.1                                                     | Configuration of test system                   | 14           |  |  |  |

| 4        | Des                                                     | scription of modeling environment              | <b>15</b>    |  |  |  |

|          | 4.1                                                     | Historic context                               | 15           |  |  |  |

|          |                                                         | 4.1.1 Modeling reactive systems                | 15           |  |  |  |

|          | 4.2                                                     | Modeling constructs in UML-RT                  | 16           |  |  |  |

|          | 4.3                                                     | UML-RT tools at the department                 | 17           |  |  |  |

| 5        | Previous work and tools for software model verification |                                                |              |  |  |  |

|          | 5.1                                                     | vUML                                           | 19           |  |  |  |

|          | 5.2                                                     | Hugo                                           | 20           |  |  |  |

|          | 5.3                                                     | VIP and v-Promela                              | 20           |  |  |  |

|          | 5.4                                                     | TABU                                           | 20           |  |  |  |

|   | $5.5 \\ 5.6$ | SMARRT                                                  | 21<br>21 |

|---|--------------|---------------------------------------------------------|----------|

| 6 | Pro          | totype system integrating RSARTE with Spin              | 22       |

|   | 6.1          | Verification model extraction options                   | 22       |

|   |              | 6.1.1 Code generation in RSARTE using JET               | 23       |

|   | 6.2          | Verification model overview                             | 25       |

|   |              | 6.2.1 Modeling capsule interaction with the environment | 25       |

|   |              | 6.2.2 Mapping concepts in UML-RT to Promela             | 26       |

|   |              | 6.2.3 Signal producers and consumers                    | 27       |

|   |              | 6.2.4 Embedded Promela code                             | 28       |

|   |              | 6.2.5 Property verification                             | 28       |

|   | 6.3          | Verification model options                              | 28       |

|   | 6.4          | JET transformation structure                            | 29       |

| 7 | Pro          | perty specification                                     | 30       |

|   | 7.1          | Internally specified properties                         | 30       |

|   | 7.2          | Externally specified properties                         | 31       |

|   | 7.3          | Properties of primary interest                          | 32       |

|   |              | 7.3.1 Signal handling guarantee                         | 32       |

|   |              | 7.3.2 Trap detection                                    | 32       |

|   | 7.4          | Limitations in property specification                   | 33       |

| 8 | Mo           | del examples                                            | 34       |

|   | 8.1          | A model of a traffic light system                       | 34       |

|   |              | 8.1.1 Model description                                 | 34       |

|   |              | 8.1.2 Properties                                        | 35       |

|   |              | 8.1.3 First version                                     | 35       |

|   |              | 8.1.4 Second version                                    | 36       |

|   |              | 8.1.5 Third version                                     | 37       |

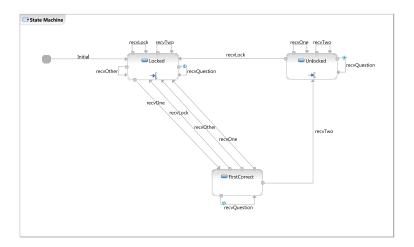

|   | 8.2          | A model of an electronic lock                           | 42       |

|   |              | 8.2.1 Model description                                 | 42       |

|   |              | 8.2.2 Properties                                        | 43       |

|   |              | 8.2.3 First version                                     | 43       |

|   |              | 8.2.4 Second version                                    | 44       |

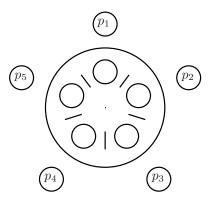

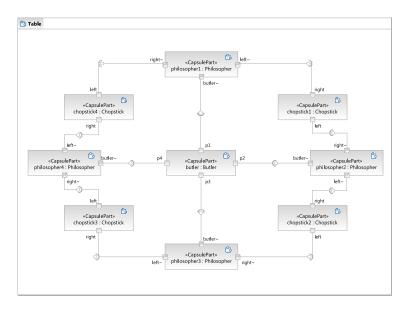

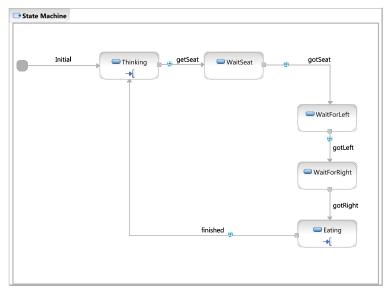

|   | 8.3          | The dining philosophers                                 | 45       |

|   |              | 8.3.1 Problem scenario                                  | 45       |

|   |              | 8.3.2 Model description                                 | 47       |

|   |              | 8.3.3 Properties                                        | 47       |

|   |              | 8.3.4 Model implementation                              | 48       |

|   | 8.4          | A model with intentional errors                         | 49       |

|   |              | 8.4.1 Model description and properties                  | 49       |

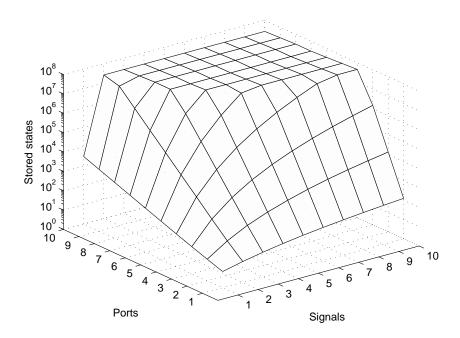

|   | 8.5          | A complexity experiment                                 | 50       |

| 9 | Res          | sults                                                   | 55       |

|   | 9.1          | Traffic light system                                    | 55       |

|   |              | 9.1.1 First version                                     | 55       |

|   |              | 9.1.2 Second version                                    | 57       |

|   |              | 9.1.3 Third version                                     | 59       |

|   | 9.2          | Electronic lock                                         | 61       |

|              |      | 9.2.1 First version                  | 31 |

|--------------|------|--------------------------------------|----|

|              |      | 9.2.2 Second version                 | 34 |

|              | 9.3  | Dining philosophers                  | 64 |

|              | 9.4  | Model with intentional errors        | 70 |

|              | 9.5  | Complexity experiment                | 70 |

| 10           | Con  | clusions 7                           | 3  |

|              | 10.1 | Answers to questions                 | 73 |

|              |      |                                      | 77 |

|              |      | 10.2.1 Benefits and drawbacks        | 77 |

|              |      | 10.2.2 Primary application areas     | 77 |

|              |      | 10.2.3 Important verification issues | 78 |

|              | 10.3 | Future work                          | 79 |

|              |      | 10.3.1 Properties                    | 79 |

|              |      | 10.3.2 Model transformation          | 79 |

|              |      | 10.3.3 Scalability                   | 30 |

| $\mathbf{A}$ | Pro  | nela model example 8                 | 5  |

| В            | JET  | transformation templates 9           | 5  |

# List of Figures

| 2.1  | Outline of a general model checking workflow                      | 7  |

|------|-------------------------------------------------------------------|----|

| 4.1  | Example of actors in ROOM                                         | 16 |

| 6.1  | Prototype system outline                                          | 24 |

| 6.2  | Illustration of capsule interaction                               | 25 |

| 6.3  | JET transformation project structure                              | 29 |

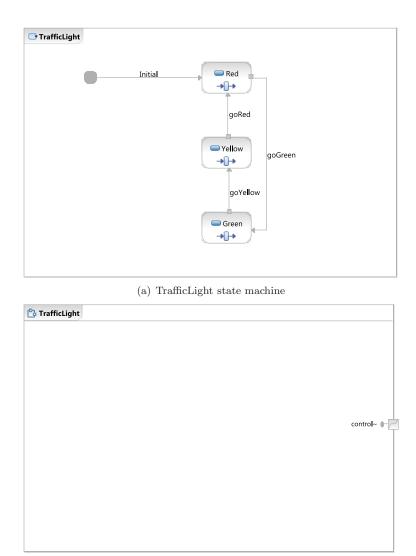

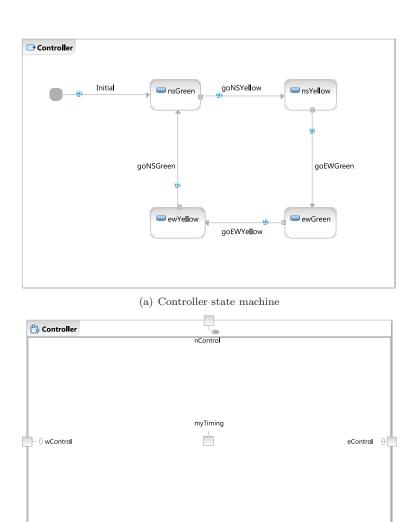

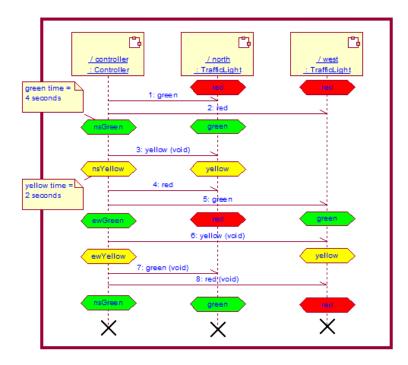

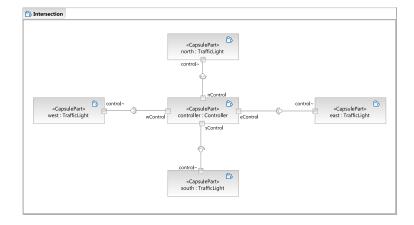

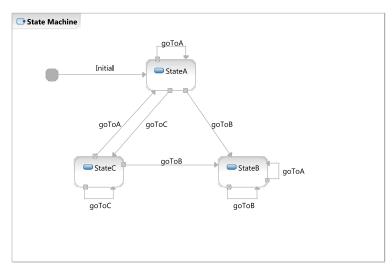

| 8.1  | Traffic light capsule state machine and structure diagram         | 38 |

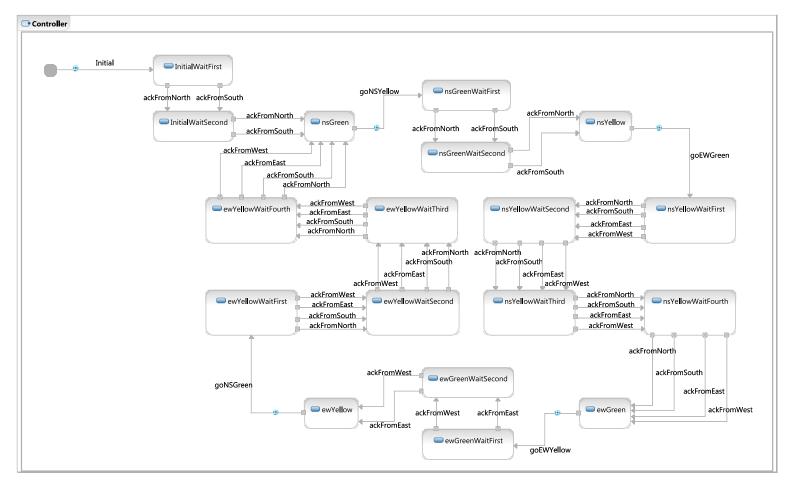

| 8.2  | Original controller capsule state machine and structure diagram . | 39 |

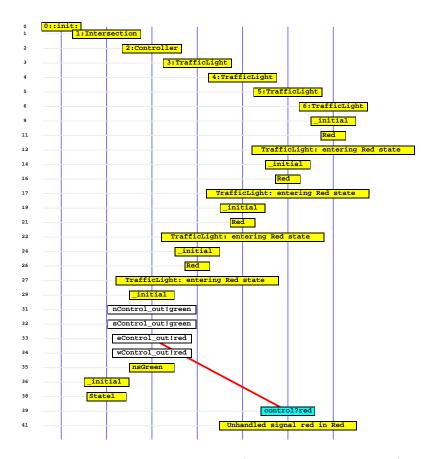

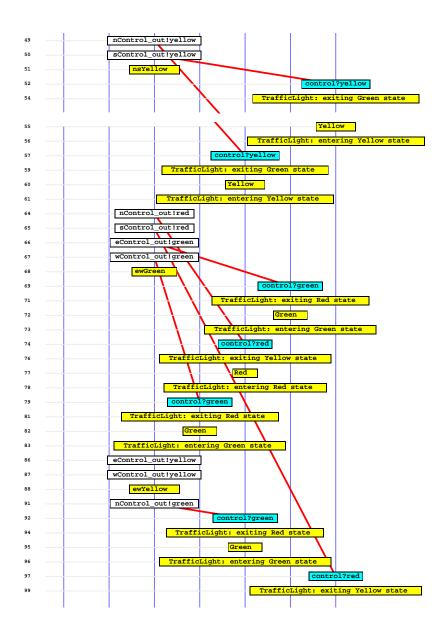

| 8.3  | Traffic light system sequence diagram                             | 40 |

| 8.4  | Intersection capsule structure diagram                            | 40 |

| 8.5  | Controller capsule modified state machine diagram                 | 41 |

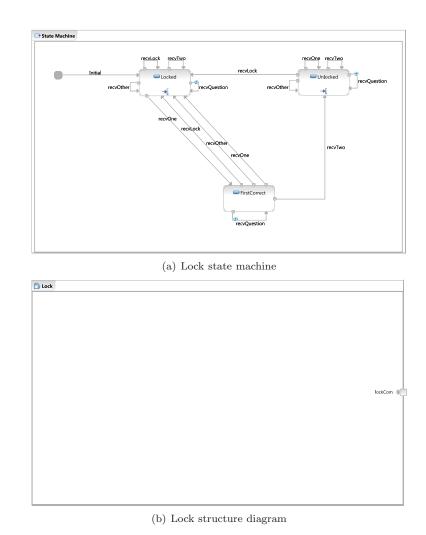

| 8.6  | Lock capsule state machine and structure diagram                  | 44 |

| 8.7  | Lock capsule modified state machine diagram                       | 45 |

| 8.8  | The Dining philosophers                                           | 45 |

| 8.9  | Table capsule structure diagram                                   | 48 |

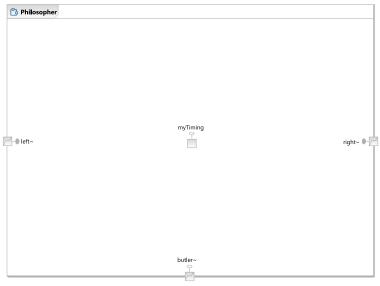

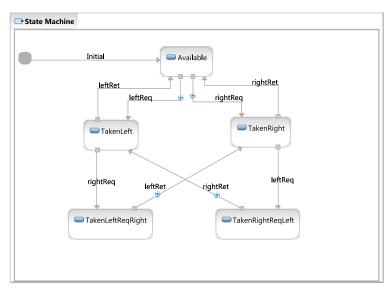

| 8.10 | Philosopher capsule state machine and structure diagram           | 51 |

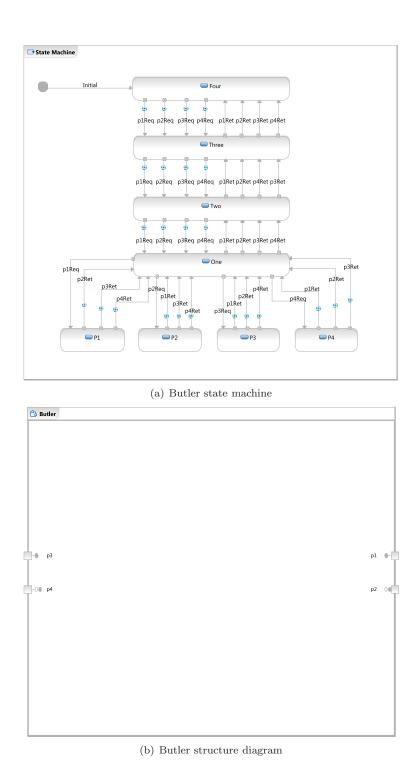

| 8.11 | Butler capsule state machine and structure diagram                | 52 |

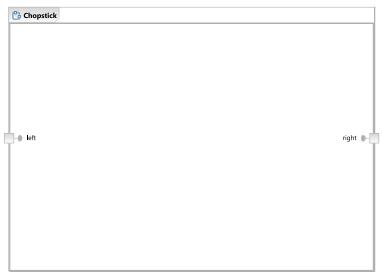

| 8.12 | Chopstick capsule state machine and structure diagram             | 53 |

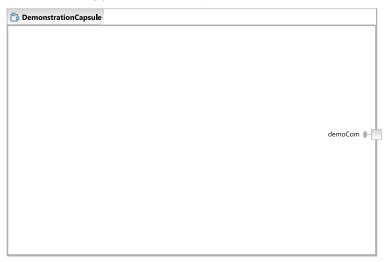

| 8.13 | Demonstration capsule state machine and structure diagram         | 54 |

| 9.1  | Error scenario: first traffic light system model, property 1      | 56 |

| 9.2  | Error scenario: second traffic light system model, property 3     | 60 |

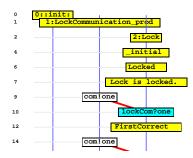

| 9.3  | Error scenario: first electronic lock model, property 2           | 63 |

| 9.4  | Error scenario: first electronic lock model, property 4           | 65 |

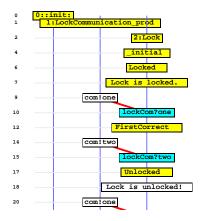

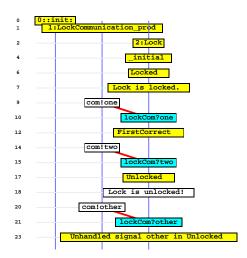

| 9.5  | Error scenario: second electronic lock model, property 1          | 66 |

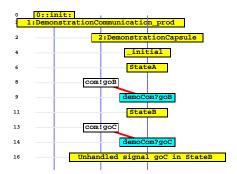

| 9.6  | Error scenario: demonstration model, property 1                   | 71 |

| 9.7  | Results: Complexity experiment                                    | 72 |

# Listings

| 2.1  | Promela model vulnerable to a data race situation                       | 9  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Spin output showing an assertion violation                              | 0  |

| 8.1  | Transition effect code of the first traffic light system controller . 3 | 86 |

| 8.2  | Stimulus process for the electronic lock capsule                        | 12 |

| 9.1  | Results: first traffic light system model, property 1 5                 | 6  |

| 9.2  | Results: second traffic light system model, property 1 5                | 7  |

| 9.3  | Results: second traffic light system model, property 2 5                | 8  |

| 9.4  | Results: second traffic light system model, property 3 5                | 8  |

| 9.5  | Results: third traffic light system model, property 1 5                 | 69 |

| 9.6  | Results: third traffic light system model, property 2 6                 | i1 |

| 9.7  | Results: third traffic light system model, property 3 6                 | 32 |

| 9.8  | Results: first electronic lock model, property 1 6                      | 32 |

| 9.9  | Results: first electronic lock model, property 2 6                      | 3  |

| 9.10 | Results: first electronic lock model, property 3 6                      | 64 |

| 9.11 | Results: first electronic lock model, property 4 6                      | 55 |

| 9.12 | Results: second electronic lock model, property 1 6                     | 66 |

| 9.13 | Results: dining philosophers model, property 1 6                        | 57 |

| 9.14 | Results: dining philosophers model, property 2 6                        | 8  |

| 9.15 | Results: dining philosophers model, property 3 6                        | 69 |

| 9.16 | Results: dining philosophers model, property 4 6                        | 69 |

| 9.17 | Results: demonstration model, property 1                                | 0  |

|      |                                                                         | 1  |

|      |                                                                         | 86 |

| B.1  |                                                                         | 96 |

| R 2  |                                                                         | 7  |

# Terminology

# Acronyms

CTL Computation Tree Logic

**FSM** Finite State Machine

**JET** Java Emitter Template

LTL Linear Time Logic

**OTD** ObjecTime Developer

OTI Object Technology International

Promela Process Meta Language

**PSL** Property Specification Language

**ROOM** Real-Time Object-Oriented Methodology

**RoseRT** IBM Rational Rose RealTime

**RSARTE** Rational Software Architect Real Time Edition

**SMARRT** Static Model checking and Analysis for Rose RealTime

**SMV** Symbolic Model Verifier

Spin Simple Promela Interpreter

**TABU** Tool for the Active Behaviour of UML

**UML-RT** UML Real Time

UML Unified Modeling LanguageVIP Visual Interface to Promela

WCDMA Wideband Code Division Multiple Access

XMI XML Metadata Interchange

**XML** Extensible Markup Language

**XPath** XML Path Language

# CHAPTER 1

#### Introduction

The presence of errors in computer systems, both originating from incorrect design choices as well as from implementation mistakes, remains a challenge in the industry. Despite traditional validation and verification counter measures, such as simulation and testing, mistakes are costly. Figures released in 2002 estimated that the industry cost of software faults in the United States alone, approached 60 billion dollars (NIS 2002).

Faults may be present in the design or implementation of a system and certain conditions may activate a fault, causing an error to be produced. Unless such an error is properly handled, it may propagate and cause the system output to deviate from the specified output, resulting in a failure (Avizienis, Laprie, Randell & Landwehr 2004).

Software and hardware testing can expose faults that may exist in the system, provided that a test case has been constructed, which activates the fault and exposes the resulting error. The task of constructing suitable test cases is not trivial and attempting to ensure that all faults are found by testing the system exhaustively is often an impossible task (Clarke, Grumberg & Peled 1999, p. 2). As will be illustrated by the following two examples, gathering even overwhelming amounts of empirical evidence to support a claim does not *prove* its correctness.

The first example is the floating point unit of Pentium processors which was found to be flawed in 1994. The fault lay in a lookup table used for division operations and was due to entries missing from the table. This, in turn, caused certain instructions related to floating point division to produce results deviating from the correct output. The probability of activating the fault by applying one of the affected instructions to a randomly chosen value from the input space was 1 to 9 billion, according to analysis by Intel (Int 1994).

A more theoretical example of a problem which is difficult to analyze correctly using testing is the following: We can claim that there exists no positive integer n such that  $991 \cdot n^2 + 1$  is a perfect square, apart from the trivial solution of n = 0. This claim happens to be incorrect, but the first positive integer

solution does not occur until

n = 12,055,735,790,331,359,447,442,538,767

(Rotman 1998), suggesting that it is difficult to falsify the hypothesis using testing. The only feasible method of refuting the hypothesis is to use a method that relies on proofs rather than on an exhaustive search.

Formal verification methods rely on techniques from logic and mathematics, in practice usually supported by computer tools, to prove properties about systems. Such methods have been used successfully in the development of systems that require a very high degree of confidence that the product meets its specification.

There are many reasons to why a system may demand rigorous design validation. Safety requirements, such as in air traffic control systems or flight control systems; security requirements, such as in implementations of cryptographic protocols; or the cost of failure may all motivate the use of formal verification. Legal requirements, such as in digital signing of programs or documents to ensure authenticity and non-repudiation; certification requirements; or legal implications of failure in any of the above scenarios may also warrant the use of formal methods (Elamkulam, Glazberg, Rabinovitz, Kowlali, Gupta, Kohli, Dattathrani & Macia 2006).

# 1.1 Background

The telecommunications company Ericsson AB develops software for radio base stations for the Wideband Code Division Multiple Access (WCDMA) standard at a department at Lindholmen in Gothenburg (hereinafter referred to only as the "department"). The software is developed with visual tools that support modeling in a dialect of UML and C++ code is then generated directly from the models. The modeling language in use at the department is UML Real Time (UML-RT), currently supported by the tool IBM Rational Rose RealTime (RoseRT) but being superseded by the Rational Software Architect Real Time Edition (RSARTE) tool.

UML-RT, described in more detail in Chapter 4, is for example used at the department to model hierarchies of concurrently operating system components called *capsules*, whose behaviors are defined using state machines and that communicate with each other using message passing. The behavior of a single capsule can be very complex and the combined behavior of several capsules even more so.

Testing of both normal and failure cases is performed at the department. However, there is always a possibility that faults in capsules remain undiscovered and appear when least expected. In the words of Dijkstra (1970, p. 7), "Program testing can be used to show the presence of bugs, but never to show their absence!" For this reason, the department is interested in understanding and exploring the possibility of using formal verification methods as a complement to the testing procedures in current use.

#### 1.2 Aim

The purpose of the thesis is to evaluate how formal verification can be integrated in the model based development process used for developing the application software for WCDMA base stations at the department. This thesis aims to provide answers to the following questions:

- 1. What methods and tools for formal verification of software models are available in the academic, industrial or open source communities? We decompose this question into the following sub-questions:

- (a) What approach could be used as a basis for verification of models developed at the department?

- (b) Are there existing tools for formal verification that can be directly used to verify properties of models in the development environment at the department? If this is not the case, are there existing tools that can serve as a foundation for implementing such a tool?

- (c) Can these tools be integrated into the development environment at the department?

- 2. What properties are of interest to the department to verify?

- 3. How should models be developed to allow such properties to be formally verified using the chosen method?

- 4. What can be gained from applying formal verification methods to the department's software models?

Furthermore, since it is of interest to the department that the viewpoints of the software designer are considered throughout the work, decisions regarding the verification approach, tool selection and design choices will be made with the potential future user of the tool in mind.

#### 1.3 Limitations

Any prototypical tool implemented is intended to serve as a proof of concept, outlining a possible method for property verification. For this reason, it is not an aim to handle models of the same size or complexity as can be found in the department's products. In addition to varying greatly in complexity, the models developed at the department are produced with tools that support a large number of modeling constructs. The scope of this thesis is limited to a subset of the available constructs (see Section 6.2.2).

The verification is intended to target only properties of the model and not to make any claims about correctness of code embedded in the model. Therefore, no code analysis methods for extracting information from embedded code are considered. This in turn implies that any fully automated verification procedure is beyond the scope of this thesis.

Any model properties related to time (in the sense that can be measured numerically, not in the sense of ordering of events) will be either treated on an abstract level or be completely disregarded. This is a common practice when modeling concurrent or distributed systems, because as Ben-Ari (2008, p. 173) explains,

"Algorithms for these systems are designed to be independent of the speed of execution of a process or the speed at which a message is delivered, so it is sufficient to know that there are no errors caused by interleaving statements and messages."

## 1.4 Disposition

Abbreviations, terminology and names used in this disposition are explained as they are later introduced. The remainder of this thesis is ordered as follows:

- Chapter 2 presents an introduction to the field of formal verification, as well as a brief introduction to the verification tool Spin, which is used in the prototype tool.

- Chapter 3 presents the method chosen for addressing the questions that this thesis aims to answer.

- Chapter 4 presents the background of UML-RT and a description of the modeling tools used at the department. A presentation of modeling concepts and building blocks of UML-RT is also given, together with an explanation of the link between UML-RT and the two modeling tools RoseRT and RSARTE.

- Chapter 5 presents a survey of previous work in the field of software model verification. An assessment of previous work and existing verification tools as they relate to the modeling language used at the department is also given.

- Chapter 6 presents a description of a prototype tool implemented for integrating the model checker Spin with the modeling tool RSARTE.

- Chapter 7 presents a categorization of system properties and a description of how such properties may be specified. The two properties that are of primary interest to the department are also presented.

- Chapter 8 describes the models and presents the properties that are verified using the prototype tool.

- Chapter 9 presents verification results for each model and property.

- Chapter 10 presents answers to the questions that the thesis aims to answer. A discussion on the limitations of the chosen verification approach and prototype tool is presented, together with suggestions for possible future extensions and improvements of the work.

- **Appendix A** presents the verification model for a capsule discussed in Section 8.4.

- **Appendix B** contains two sample JET templates that are part of the prototype tool.

Theory

This chapter provides an introduction to the use of model checking tools, to formally verify systems. We describe formal specification languages using the model checker Simple Promela Interpreter (Spin) and its input languages as the example.<sup>1</sup>

#### 2.1Formal Verification

The objective of formal verification is to extend beyond what is possible to achieve using testing procedures, by providing a formal proof that a system conforms with design specifications. The system in question can, for example, be a hardware circuit or communication protocol (Clarke et al. 1999), or a software design (Holzmann 2003). The two major methods used to formally verify systems are deductive verification and model checking (Clarke et al. 1999).

Deductive verification relies on using a system of axioms and application of inference rules, to prove a system correct. This can be, and was originally done, manually, but generally requires expertise in both the area of the target system and in mathematics or logic. Tools such as KeY<sup>2</sup> and HOL Light<sup>3</sup> have been developed to aid the user by automatically providing a complete proof, or by serving as a proof assistant that guides the user's interaction with a theorem prover. According to Ben-Ari (2008, p. 23), one advantage of deductive methods is that they may allow verification of systems where the size of the state space would otherwise be limiting.

<sup>&</sup>lt;sup>1</sup>Spin is used as the example since it is used in later parts of this thesis. A motivation for this choice is given in Section 5.6. http://www.key-project.org

<sup>3</sup>http://www.cl.cam.ac.uk/~jrh13/hol-light/

## 2.2 Model Checking

The model checking field originated in the early 1980s as a method for addressing the problem of verifying concurrent programs (Clarke 2008). Such programs are hard to debug due to the frequent difficulty of reproducing errors (Clarke 2008). If the tasks executing concurrently in the program communicate or otherwise depend upon each other, it can very quickly become problematic to establish under what conditions deadlocks may occur or mutual exclusion constraints may be violated, due to the large number of possible ways in which multiple tasks may interleave.

Clarke et al. (1999) partition the process of model checking a design into three steps; modeling, specification and verification.

Modeling The design must be represented or encoded in some formal language. This can be done by directly writing code in the language of the model checker, or by transforming some other description, such as source code, into the language of the model checker. This transformation can be done manually, or by using some automated pre-processor (see for example Beyer, Henzinger, Jhala & Majumdar (2007) and Holzmann & Smith (1999)).

**Specification** The properties that the model should satisfy must also be stated in an unambiguous, formal notation. This requires firstly an understanding of what properties are of interest to verify, and secondly a language sufficiently expressive to capture those properties. Examples of such languages are Linear Time Logic (LTL)<sup>4</sup> and Computation Tree Logic (CTL), both members in the temporal logic family.

Verification The tool will accept the model and the specification and determine whether the design meets the requirements. The tool will determine if, for every possible path through an algorithm or for every possible state of a hardware circuit, the model satisfies the specification.

This task is not performed with brute-force methods since that would be infeasible for most target systems. For example, circuits with more than  $10^{90}$  states have been verified using model checking (Emerson 2008) which is far beyond the reach of any brute-force algorithm.

The two dominating model checking methods are divided by Holzmann (2003) into those using symbolic verification methods and those using explicit verification methods. An example falling into the first category is the Symbolic Model Verifier (SMV) tool that is based on Ordered Binary Decision Diagram manipulation techniques (Clarke et al. 1999). The Spin tool falls into the second category and uses partial order reduction (see section 2.3.5) as part of its strategy to cope with the state explosion problem (Holzmann 2003).

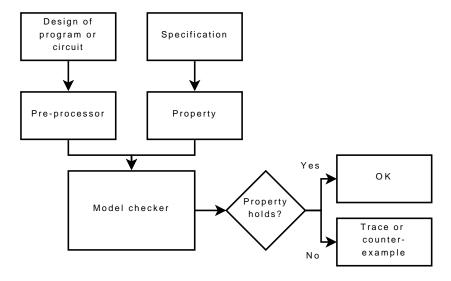

### 2.2.1 Model checking workflow

The practical usage of a model checker will typically follow the workflow outlined in Figure 2.1. A design is transformed into a description suitable for the model

<sup>&</sup>lt;sup>4</sup>LTL is described in more detail in Section 2.3.3.

checker, either manually or with the aid of tools, and a specification of a wanted or unwanted behavior is captured as a property. The result produced by the model checker on the basis of this information is either confirmation that the property has been verified to hold, or an error trace showing how the property can be invalidated (Clarke 2008, pp. 2–3). If given sufficient resources, the model checking tool will always terminate with an answer (Clarke 2008, pp. 3).

Figure 2.1: Outline of a general model checking workflow.

# 2.3 The Spin model checker

The Spin model checker was originally developed at Bell Labs in the beginning of the 1980s (Holzmann 1997) and has since been continuously developed. Spin has been available since 1991 and can be used freely for educational purposes (Holzmann 2003). Commercial use of Spin does not command a fee but requires a license agreement to be accepted (LIC 2001).

Spin is a system for proving properties of software systems by enabling a designer to create abstract models of the target system, specify properties that must hold for the model and verify if this is in fact the case or not.<sup>5</sup> Spin allows the designer to explore — through simulation or verification — system behavior which results from interaction between processes.

Spin uses verification models specified in Process Meta Language (Promela) (Holzmann 1997) and can be used in several ways including random, interactive or guided simulation mode, and verification mode. When used as random simulator, Spin will follow one randomly chosen execution path of the modeled system. In interactive simulation mode, the user is called upon to decide how to proceed when a choice must be made between possible execution paths. In guided simulation mode, Spin follows a trail file that describes a specific execution path through the system.

$<sup>^5</sup>$ For the underlying theory of how models and properties are handled by Spin to perform the verification, see Holzmann (1997).

Note that no amount of repeated random simulation guarantees that every execution path is eventually taken. The results from a simulation run is only applicable to the particular execution path through the system selected in that specific simulation run. A verification run is therefore necessary to verify claims about *all* of the possible simulation runs, i.e., about every possible execution path of the system. If Spin finds that a model does not satisfy a particular property, then a trail file is generated. The file details the exact steps that produces a violation of the property and can be used in guided simulation mode to replay the execution (Holzmann 2003, pp. 245–252).

#### 2.3.1 The Promela specification language

Promela is a specification language, visually resemblant of C, for describing models of concurrent systems. The number of constructs supported by the language is intentionally small and the focus of those constructs is on describing behavior and interaction between system components, rather than computation. The reason for this is that, "Promela is not meant to be an implementation language but a systems description language." Holzmann (2003, p. 8)

The Promela language provides features for describing concurrently executing processes and communication between such processes using message passing over buffered or unbuffered message channels. Promela also makes it easy to model indeterministic choice through the use of control statements similar to Dijkstra's guarded commands (Holzmann 2003, p. 407).<sup>6</sup> However, there are no features for returning values from function calls, no support for floating point numbers and no notion of time beyond event ordering.(Holzmann 2003, p. 8)

#### 2.3.2 A Promela example

It is beyond the scope of this thesis to describe details of Spin and Promela, but Listing 2.1 serves to give an impression of syntax and concepts of the Promela language. For a complete description of Spin, Promela and further examples see, e.g., Holzmann (2003), Ben-Ari (2008) and Holzmann (1997).

The example models a scenario with two bank tellers and two bank customers, communicating in pairs using message passing over a channel. The customers share one bank account with an initial balance of 60 currency units. The customers both carry out three transactions, choosing indeterministically between attempting to withdraw or to deposit 50 currency units. When a bank teller receives an order to withdraw money, the balance of the account is checked to ensure that it holds sufficient funds. If this is the case then the balance is decreased and the teller then verifies that the balance has not somehow fallen below zero (see lines 14–15 in Listing 2.1). When a bank teller receives an order to deposit money, the balance is increased.

A verification run with Spin can be used to find a process interleaving that can cause the account balance to fall below zero. The resulting trail file can in turn be used to playback the execution and locate the error. Listing 2.2 presents condensed output from the execution playback. It demonstrates that the assertion violation occurs when the first teller is interrupted in the withdrawal procedure *after* checking the account balance, but *before* recording the

<sup>&</sup>lt;sup>6</sup>See for example lines 28–31 in Listing 2.1.

Listing 2.1: Promela model vulnerable to a data race situation.

```

1 short balance = 60;

3 \text{ mtype} = \{ \text{withdraw}\_50, \text{ deposit}\_50 \};

5 \text{ chan } \text{channel\_a} = [0] \text{ of } \{ \text{ mtype } \};

6 \text{ chan channel_b} = [0] \text{ of } \{ \text{ mtype } \};

8 proctype teller(chan in) {

9 end:

10

do

:: in ? withdraw\_50 \rightarrow

i f

12

:: balance >= 50 \rightarrow

13

balance = balance - 50;

14

15

assert(balance >= 0);

else \rightarrow skip;

::

16

fi

17

:: in ? deposit\_50 \rightarrow

18

balance = balance + 50;

19

20

21

22

23

proctype customer(chan out) {

24

25

byte transactions = 3;

26

:: transactions > 0 \rightarrow

27

i f

28

:: out ! withdraw_50;

29

:: out ! deposit_50;

30

31

transactions = transactions - 1;

32

else -> break;

33

34

od

35

36

37

38 init {

atomic {

39

run teller (channel_a);

40

run customer(channel_a);

41

run teller (channel_b);

42

run customer(channel_b);

43

}

44

45

```

Listing 2.2: Condensed Spin output demonstrating a process interleaving resulting in an assertion violation.

```

2 (customer 1)

out!withdraw_50]

1 (teller 1)

in?withdraw_50]

2 proc

3 proc

[((balance>=50))]

1 (teller 1)

4 (customer 2) [out!withdraw_50]

5 proc

in?withdraw_50]

3 (teller 2)

3 (teller 2)

[((balance>=50))]

proc

3 (teller 2)

[balance = (balance-50)]

9 proc

10 proc

3 (teller 2)

[assert((balance>=0))]

11

1 (teller 1)

[balance = (balance-50)]

12 proc

13 spin: Error: assertion violated

14 spin: text of failed assertion: assert((balance>=0))

15 proc

1 (teller 1)

[assert((balance>=0))]

```

new balance. The consequence is that the tellers are able to make a withdrawal each, based on the same account balance, incorrectly causing a final negative balance.

#### 2.3.3 Property specification in Spin using LTL

The properties that we wish to prove or refute for a given Promela model must be specified in some formal notation. The example in Section 2.3.2 showed a correctness claim specified using an assertion statement, but Spin also supports verification of correctness claims specified in LTL (Holzmann 1997). This temporal logic allows specifications that refer to the future (Huth & Ryan 2004, p. 175) by extending propositional logic formulas with temporal connectives (Ben-Ari 2008, pp. 71–72).

The operators inherited from propositional calculus are: negation, conjunction, disjunction, implication and equivalence. In addition to this, LTL provides the temporal operators always, eventually, (strong) until, the dual of until (commonly referred to as release) and next. These allow us to state claims about the behavior of the Promela model and to use Spin to assert or refute those claims. See Holzmann (2003, pp. 135–136) for a complete description of the semantics of the operators and the syntax used in Spin.

- Always ( $\square$ ) captures properties that are related to invariance, e.g., the formula  $\square$  p specifies that condition p always holds true. The operator is written [] in Promela.

- **Eventually** ( $\Diamond$ ) captures properties related guaranteed behavior, e.g. the formula  $\Diamond$  p specifies that the condition p holds in the current state or will hold in some future state. The operator is written  $\Leftrightarrow$  in Spin.

- Until ( $\mathcal{U}$ ) captures properties of relative behavior, e.g.  $p \mathcal{U} q$  specifies that the condition p must hold until q becomes true (now or in the future).

The definition of weak until does not require that q ever becomes true, while the definition of strong until does require that q at some point holds true. Spin uses the strong definition of until (Ben-Ari 2008, p. 91). The operator is written U in Spin.

- **Release** ( $\mathcal{R}$ ) is the dual of the strong until operator, e.g.,  $p \mathcal{R} q$  specifies that q holds true until p becomes true, which releases q. If p never becomes true, then q must hold forever. The operator is written V in Spin.

- **Next** ( $\mathcal{X}$ ) captures properties that relate a state to its successor, e.g.,  $\mathcal{X}$  p holds in the current state iff p holds in the *next* state. The operator is written X in Spin.

The *next* operator requires caution because of the restrictions on its use that are imposed by Spin. The default behavior of Spin is to disallow the use of the *next* operator, due to the possibility of conflicts with the state space reduction method used by Spin (see Section 2.3.5).

#### 2.3.4 LTL property verification

Spin can be used both to prove desired behaviors (i.e., properties that should always hold) or error behaviors (i.e., properties that should never hold). For reasons of verification efficiency, Spin does not attempt to prove that a behavior is guaranteed; instead Spin attempts to show how a behavior claimed to be impossible can in fact be achieved (Holzmann 1997, p. 97).

This means that to prove a desired behavior, an LTL formula that captures that behavior is specified and then *negated*. Spin then attempts to show a run of the system in which the negated formula holds. If Spin succeeds, then the desired behavior can be violated; but if Spin determines that the negated claim cannot be refuted, then the model must exhibit the desired behavior. We can conclude that Spin is used "to check for *violations* of requirements." (Holzmann 2003, p. 149)

The challenge for any designer using model checking is to construct a small yet sufficiently detailed verification model that ideally only captures the features of the design that "must be considered to establish correctness" (Clarke et al. 1999, p. 13). Unnecessary details that make the model more complicated without affecting the "correctness of the checked properties" (Clarke et al. 1999, p. 13) should be omitted.

#### 2.3.5 Problem space reduction

Holzmann (2003, p. 191) writes that Spin makes use of two types of strategies for addressing the state space explosion problem, the aims of which are either "to reduce the number of reachable states that must be searched to verify properties, or to reduce the amount of memory that is needed to store each state."

One method used by Spin is called partial order reduction. According to Clarke et al. (1999) partial order reduction relies on selecting and examining only a subset of all possible execution paths. One example of how this is achieved is by detecting interleaving of processes such that the relative ordering of the processes' execution steps do not affect the final outcome of the execution, with

regards to the property being verified. This reduces the problem size because, as Clarke et al. (1999) writes,

"When a specification cannot distinguish between two interleaving sequences that differ only by the order in which concurrently executed events are taken, it is sufficient to analyze only one of them."

Another means of reduction is to exploit stutter equivalence, in that,

"a pair of sequences are considered to be equivalent if they differ in at most the number of times a state may adjacently repeat." (Peled, Wilke & Wolper 1995)

Spin's partial order reduction strategy assumes that stutter equivalence can be used and is therefore only guaranteed to be valid for stutter invariant properties. Although it is not impossible to write stutter invariant properties that make use of the next operator (Holzmann 2003), an LTL formula which does not contain the next operator is guaranteed to be stutter invariant (Peled et al. 1995). It is therefore also guaranteed not to invalidate the results of the partial order reduction algorithm (Holzmann 2003). Nonetheless, Ben-Ari (2008) comments that the abstract treatment of time explains why it would be of limited benefit to allow the next operator,

"For example, in a client-server system, we want to specify that a client process *eventually* receives a service from a server process but it doesn't really matter if that occurs in the next state or ten states later."

Lamport (1983, p. 661) also argues against the inclusion of a next operator in a temporal logic with the motivation that this allows requirements to be specified that distinguish between models on the basis of properties that are irrelevant in an abstract specification.

# CHAPTER 3

Method

In order to address the questions posed in Section 1.2, this project is divided into two phases:

**Phase 1:** An initial study of previous work describing methods and tools for formal verification of state machines and UML-RT models is carried out. The purpose of this is to provide an understanding of what verification approach can be suitable in the modeling environment at the department. We assess the applicability of existing work in the context of this environment, based on two factors:

- 1. The ability of the tool to verify properties that are of current interest, but also of possible future interest to the department.

- 2. The potential for integrating the proposed approach (and possibly already existing tool) into the department's tool environment.

The findings of the initial study determine if

- 1. a tool considered suitable is available, or if

- 2. a prototype tool based on principles suggested by previous work has to be implemented.

The results of the first phase determined that the second phase was directed towards the latter possibility, i.e., towards implementing a prototype tool.

**Phase 2:** We then demonstrate the chosen verification approach by conducting a case study, exploring the use of model checking in the setting of an RSARTE environment. In the case study, we

model selected problems with the modeling tools used at the department, and 2. apply the selected verification approach and tool to demonstrate how properties of those models can be verified.

The problems studied and modeled are chosen mainly from training material for the modeling tools used at the department. Starting with models from training material is suitable since such models introduce fundamental building blocks and important constructs used in the modeling environment. Avoiding complex models is also suitable for a prototype demonstration, since the intended focus is on the feasibility of verification rather than on tool performance.

In addition to problems from training material, the problem of the dining philosophers — which is well-known within verification and concurrent programming — is also modeled.

## 3.1 Configuration of test system

The experiments with verifying the properties of modeled problems are conducted on a test system running a 64-bit GNU/Linux operating system, using version 5.1.7 of the Spin model checker. Each experiment is restricted to using a maximum of 3200 MB of memory, and has a maximum time limit set to two hours.

# Description of modeling environment

The department develops software using the modeling language UML-RT, supported by modeling tools such as RoseRT and RSARTE. RoseRT is the tool in current use at the department but it is in the process of being replaced by RSARTE. This chapter gives a historic perspective on UML-RT and provides an introduction to modeling constructs that are important in UML-RT and that should be supported by a verification tool.

#### 4.1 Historic context

To give a better understanding of UML-RT, and how it relates to the tools evaluated in Chapter 5, we present a brief historical overview of some of the standards, concepts and tools that have influenced UML-RT and that have been used to model reactive systems<sup>1</sup> over the past two decades.

#### 4.1.1 Modeling reactive systems

Statecharts were introduced by Harel in the 1980s as a visual formalism for specifying complex reactive systems, such as, "telephones, automobiles, communication networks, computer operating systems, missile and avionics systems, and the man-machine interface of many kinds of ordinary software." (Harel 1987)

Statecharts form an extension to *state diagrams* that can be used to represent Finite State Machines (FSMs), that were in turn already being used to describe reactive components. Harel's work allowed specification of systems that were larger compared to those that could be conveniently described using FSMs. This was achieved by the introduction of, e.g., *hierarchy* and *concurrency* or

<sup>&</sup>lt;sup>1</sup>A component which performs a fresh computation for each invocation is called *transformational*. A component which may rely on prior computations, in addition to new values, to perform a practically continuous computation is called *reactive* (Drusinsky 2006). For such components there is some notion of memory and they may therefore be called stateful, whereas the transformational components are stateless.

orthogonality (Drusinsky 2006). Classic FSMs are flat and sequential and for these reasons they do not scale well to larger systems. This limitation was reduced by the introduction of Harel's extensions (Drusinsky 2006).

The next modeling formalism was Real-Time Object-Oriented Methodology (ROOM) and its ROOM charts, a modified variant<sup>2</sup> of Harel's statecharts. ROOM was supported by the ObjecTime Developer (OTD) tool, developed by the Canadian company ObjecTime Limited.<sup>3</sup>

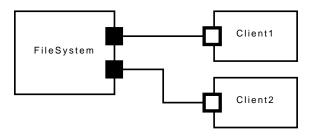

The ROOM language introduced the *actor* as a primary element (Selic 1996). The actor concept has propagated through the evolution of languages and remains in UML-RT, where it is referred to as a *capsule*. An actor is a concurrent object that communicates with its environment through interfaces known as ports. The ports are instances of protocol classes that define the message passing communication between actors. Figure 4.1 shows a ROOM example with two Client actors connected via ports to a FileSystem actor.

Figure 4.1: Example of actors in ROOM. Figure adapted from Selic (1996, p. 215).

The behavior of an actor is completely defined by a ROOM chart and the hierarchical modeling made possible by ROOM charts permits a gradual refinement of complex behavior (Selic 1996). Actors, or capsules, ports and protocols are described in more detail in Section 4.2.

# 4.2 Modeling constructs in UML-RT

This section gives an overview of some of the constructs that have been inherited by UML-RT from its ancestors. The components covered are *capsules*, *ports*, *protocols*, and *state machines*.

A capsule object corresponds to a logical execution thread and is defined by its structure and its behavior. The structure of the capsule describes its relation to other objects in the system and the behavior describes how the capsule reacts to its environment. A capsule has precisely one state machine that defines its behavior, but may contain any number of sub-capsules, referred to as capsule roles, and any number of connections to other capsules in its environment. The behavior and internal structure are completely contained

<sup>&</sup>lt;sup>2</sup>For example, ROOM charts do not support concurrent states, as a result of a trade-off decision between modeling power and code generation efficiency (Selic 1996).

<sup>&</sup>lt;sup>3</sup>In the year 2000, the Rational Software Corporation acquired ObjecTime, after which their products Rational Rose and OTD, respectively, where merged into the tool RoseRT. The Rational Software Corporation was in turn purchased by IBM in 2003 and RoseRT became part of IBM's product portfolio.

within a capsule, allowing other objects in the system to view the capsule as a black box.

Capsules communicate exclusively through message passing. Messages that are delivered to the capsule (by a run-time service library) will be received by its structure and are then processed according to its behavior. The run-to-completion semantics of capsules ensure that no more than one message at a time is delivered from the capsule's structure to its behavior. "When the capsule receives a message, a transition chain is triggered. The entire transition chain must be executed before the run-time service library delivers the next message." (Rat 2003)

The messages sent and received by capsules are defined by sets of signals grouped into *protocols*. A signal has a name, a direction (in or out) and can optionally be associated with a payload that is delivered in the message along with the signal.

The interface for communication with a capsule is called a *port*. A *public port* is an interface between a capsule and its environment, and a *private port* is an interface between a capsule and its capsule roles. Ports are associated with protocols, ensuring that only specific signals can be sent and received by the capsule using that particular port. The association also restricts how capsules can be connected to each other, e.g., by requiring that one of the connected ports is *conjugated* so that the out signals sent by one capsule correspond to the in signals received by the other, and vice versa.

A state machine defines the behavior of a capsule by describing how the capsule responds to stimuli, i.e., signals sent from other capsules. Signal reception may trigger a transition from one state to another, which in turn causes a sequence of actions to be executed. Each state may define entry and exit actions and each transition may define a transition action. In a situation where a signal received in state a triggers a transition t to state t, the exit action of t will be executed, followed by the transition action of t, followed by the entry action of t.

# 4.3 UML-RT tools at the department

RoseRT is the currently used tool at the department, but migration to RSARTE is in progress. The RSARTE tool is built on top of the Eclipse platform, which originated as a development platform at IBM's subsidiary Object Technology International (OTI) in 1998 (Cernosek 2005). Eclipse has since been released as an open source project. In 2004, IBM announced that several of its products such as Rational Software Modeler and Rational Software Architect would be built on top of the Eclipse platform, under the name IBM Rational Software Development Platform (Cernosek 2005).

RoseRT and RSARTE are both used for modeling in UML-RT. Even though both tools are based on Unified Modeling Language (UML), there are differences between the two. UML-RT models created in RoseRT are based on the 1.4 standard of UML, with custom extensions to provide the constructs that have been inherited from ROOM, e.g., capsules. The current version of RSARTE uses UML version 2.1 with a UML profile called *UMLRealTime*, which provides the necessary constructs.

Differences between model representations means that models are not in

#### Chapter 4. Description of modeling environment

practice trivially interchangeable between different tools. These compatibility issues also become clear in Chapter 5, wherein existing tools for software model verification are evaluated in relation to the UML-RT tools used at the department.

# CHAPTER 5

#### Previous work and tools for software model verification

Previous work exists in the area of property verification of UML models and this chapter presents a selection of such research projects and tools. Each tool is presented with a short description of important features and an assessment of the tool's potential for use at the department. The assessment is based on compatibility with the modeling tools and modeling language at the department, and in some cases the availability of the tool.

#### 5.1 vUML

The vUML tool, for automated property verification of state machines in UML models, is presented in (Lilius & Porres Paltor 1999a) and (Lilius & Porres Paltor 1999b). The tool translates a given UML model into a Promela model for use in the Spin model checker. Feedback to the user is given in the form of sequence diagrams generated from the error trails produced by Spin. The process of model transformation, verification and interpretation of error trails is fully automated, which frees the user from having to know Promela or interact with Spin directly.

vUML provides support for automatically verifying a set of pre-defined properties. These properties are specified by assigning special meaning to certain states of the state machine, by marking those states with labels. An example of such a label is the *invalid* label, which signifies that the marked state should never be reached. The labels are recognized in the transformation to Promela, automatically creating a verification model that includes these properties.

vUML lacks support for user specified properties, which may be limiting if properties beyond the default set are of interest. Moreover, the input language to vUML is non-standard (Lilius & Porres Paltor 1999b, p. 12) and vUML no longer appears to be distributed.

<sup>&</sup>lt;sup>1</sup>In addition to the tools discussed in more detail in this chapter, previous work has also been presented by, e.g., Mikk, Lakhnech, Siegel & Holzmann (1998), Shen, Compton & Huggins (2002) and Jussila, Dubrovin, Junttila, Latvala & Porres (2006).

## 5.2 Hugo

The Hugo<sup>2</sup> tool (Schäfer, Knapp & Merz 2001, Knapp & Wuttke 2007) allows transformation of UML models diagrams, such as state machines and collaboration diagrams, into the modeling languages of several different model checkers, including Spin. The main purpose of Hugo is to "to verify whether certain specified collaborations are indeed feasible for a set of UML state machines." (Schäfer et al. 2001, p. 9) This is achieved by producing a Promela model from the state machines and by making the claim to Spin that the behavior described by the collaboration diagram is *impossible*. Spin then attempts to refute this claim and will, if successful, produce an "error" trail demonstrating that the collaboration is in fact possible.

As in the case of vUML, Hugo relieves the user from direct interaction with the model checker and from using LTL for specifying properties. Unfortunately, Hugo does not appear to provide necessary support for UML-RT specific constructs, such as capsules.

#### 5.3 VIP and v-Promela

The Visual Interface to Promela (VIP) (Kamel & Leue 2000) is a tool for creating models visually and verifying properties using the Spin model checker as a back-end. The models created in VIP are based on v-Promela (Leue & Holzmann 1999), which is a modeling language that resembles UML-RT in several aspects, e.g., by supporting constructs such as capsules, ports and protocols, very similar to those that are found UML-RT.

The model transformation into Promela is automatic, but the verification process requires direct interaction with Spin and no information from the verification results is fed back into VIP. The exclusive use of v-Promela models in VIP also means that manipulation or verification of models created at the department is not immediately accessible. Nonetheless, the Promela code produced by VIP is interesting from a perspective of demonstrating principles for how modeling of state machines, protocols and interaction between capsules can be achieved in Promela.

#### 5.4 TABU

The work of Beato, Barrio-Solórzano, Cuesta & de la Fuente (2005) presents the Tool for the Active Behaviour of UML (TABU), an automatic verification tool for UML. The tool accepts UML models stored in the XML Metadata Interchange (XMI) format and performs an automated transformation into the modeling language of the SMV model checker. An interesting feature of TABU is that the tool provides a property writing assistant based the work of Dwyer, Avrunin & Corbett (1999), that aids the user in specifying model properties in temporal logic.

TABU does not appear to provide support for necessary UML-RT constructs.

<sup>&</sup>lt;sup>2</sup>Hugo has been released in several versions and is now called Hugo/RT. It is available at http://www.pst.ifi.lmu.de/projekte/hugo/.

## 5.5 SMARRT

The Static Model checking and Analysis for Rose RealTime (SMARRT) tool, presented in (Elamkulam et al. 2006), permits verification of properties for UML-RT models by integrating the modeling tool RoseRT with IBM's model checker RuleBase.<sup>3</sup> SMARRT is capable of automatically translating a UML-RT model into Property Specification Language (PSL), a very expressive language understood by RuleBase. It also provides functionality that aids the user in specifying model properties by using a variant of UML sequence diagrams. Verification results are presented in the form of sequence diagrams within RoseRT, making error interpretation simpler for the user.

# 5.6 Summary and conclusions of review

The SMARRT tool is closely integrated with the development tool already in use at the department but further evaluation of SMARRT and its potential for use in the future RSARTE environment is abandoned in this work, since the tool is not publicly available. The VIP tool supports several constructs similar to the ones available in UML-RT and is closely integrated with the Spin model checker. However, the tool is too restricted in its support of input models. TABU provides an interesting property assistant but does not support capsules. Neither does Hugo, although it demonstrates an interesting method for proving the feasibility of certain state machine behaviors. The vUML tool, finally, is not used for further evaluation since it appears to have become unavailable. Nonetheless, it does feature an interesting method for verifying a certain set of properties by extending an input model with special state labels.

The majority of the examined tools target some subset of UML or UML-RT models. No available tool has been found that provides sufficient support for important modeling constructs such as capsules, combined with being compatible with either RoseRT or RSARTE. The review suggests that a general approach for verifying properties of the types of models that are of interest, is to extract a verification model from the original model and to use a model checking tool to perform the verification. This corresponds to the general model checking workflow, as outlined in Figure 2.1.

Although the conclusion is that none of the reviewed tools can be integrated and used directly at the department, they highlight important concepts and interesting features that should be considered in an implementation of a prototype tool for property verification of UML-RT models. Chapter 6 describes such a prototype tool, based on the findings of this review. Spin is the model checker which dominates in reviewed previous work and it is also widely used in software model checking. It is therefore used as the back-end of the prototype tool.

$<sup>^3</sup>$ http://www.haifa.ibm.com/projects/verification/RB\_Homepage/

# Prototype system integrating RSARTE with Spin

This chapter presents design decisions for the prototype tool and outlines its implementation. The prototype tool is intended to integrate Spin with the modeling environment RSARTE, used at the department.

## 6.1 Verification model extraction options

The *pre-processor* step in Figure 2.1 corresponds to extraction of a verification model from the original model. Since the proof of concept prototype tool of this thesis is implemented using Spin as the model checking back-end, the verification model must be specified in Promela based on the original model from RSARTE. The extraction can be performed in several ways, each with advantages and disadvantages:

Manual translation A verification model can be extracted by manual implementation in Promela. Choosing this option eliminates the need to implement a transformation tool, but would be very impractical for targeting anything beyond a small number of simple capsules.

There is also a risk of losing or overlooking information when the verification model must be manually extracted and kept synchronized with a possibly changing original model. As a consequence, this option does not sufficiently consider the viewpoints of a designer and is therefore discarded.

**Re-modeling** The VIP tool supports visual modeling constructs similar to those of RSARTE. Using VIP, it is possible to model an equivalent or more abstract version of the original model, and then rely on VIP's ability to export the new model to Promela.

Compared with the previous option, the likelihood of losing information can be considered slightly lower, but the impracticalities of manually maintaining two versions of the same model disqualifies also this option.

Parsing generated C++ code The department uses code generation to produce compilable C++ code from models and Holzmann & Smith (1999) describes work done to allow automatic extraction of verification models from source code. Generating source code from a model results in a loss of abstraction, which is both unnecessary and undesirable when producing a verification model. Furthermore, verification of code is beyond the scope of this thesis and for these reasons the option is not considered further.

Parsing an exported model RSARTE allows models to be exported in XMI format. An external tool capable of parsing Extensible Markup Language (XML) could then be used to traverse the XMI file structure and generate a verification model based on the structure of the original mode. This option could spare the designer much unnecessary work required for maintaining two model versions but does not provide full integration with RSARTE.

Code generation RSARTE is built on the Eclipse framework and can as such be extended with tools and plug-ins for Eclipse, e.g., tools for model transformation and code generation. This option provides close integration with RSARTE and a high degree of automation, which is desirable from the viewpoint of a designer.

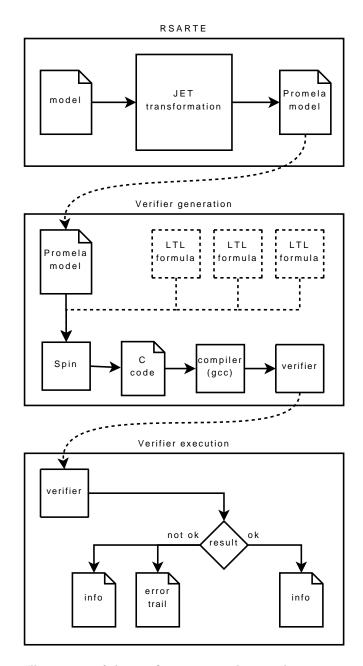

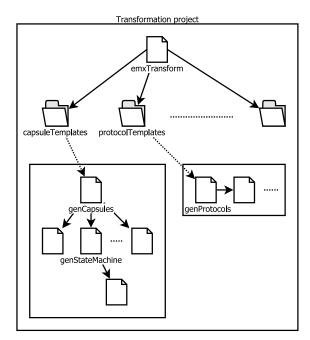

Code generation is selected for extracting a verification model in the prototype tool, since it automates much of the necessary work. The Eclipse platform's  $Model\ to\ Text^1$  project provides support for transforming models into textual artifacts. The Java Emitter Template  $(JET)^2$  tool is part of this project and can be used to generate source code in any language and is therefore used for code generation in the prototype tool. The resulting tool chain for model verification is illustrated in Figure 6.1.

The extraction of a verification model is performed within RSARTE using JET and the resulting Promela model is handed over to the Spin model checking workflow. The verifier, generated from the verification model and optional LTL property, produces verification statistics and an error trail if a property or assertion violation is detected. Holzmann (2003, pp. 245–246) provides more detailed information about Spin's verification process.

#### 6.1.1 Code generation in RSARTE using JET

JET uses a *template* system similar to Java ServerPages to describe the transformation from model to text files. The template system allows textual artifacts to be produced by mixing plain text with dynamic content extracted from the model using control tags. For example, the tags allow iteration over model elements, conditional branching and retrieval of model information. A collection of templates are combined to form a JET transformation project and can be applied to a model, producing text files where the dynamic content of the templates is expanded with information from the model (Ackerman, Elder, Busch, Lopez-Mancisidor, Kimura & Balaji 2008, p. 474).

JET uses model loaders that allow different kinds of models to be manipulated and navigated in a transformation project. The two model loaders bundled with JET do not provide sufficient support for loading models created in

<sup>1</sup>http://www.eclipse.org/modeling/m2t/

<sup>2</sup>http://www.eclipse.org/modeling/m2t/?project=jet#jet

Figure 6.1: Illustration of the verification procedure in the prototype system.

RSARTE, and the prototype tool therefore uses a customized model loader that is not part of JET by default.  $^3$

Once a model is loaded, JET allows navigation of the model structure using XML Path Language (XPath)<sup>4</sup> expressions. Information from the model, such as the names of elements, is also retrieved and inserted into the text artifacts using XPath expressions, as the template is expanded (Ackerman et al. 2008, p. 490).

# 6.2 Verification model overview

The prototype tool transforms elements from the model into a verification model in Promela. This section outlines choices made for closing the generated verification model and for transforming concepts of UML-RT to Promela.

# 6.2.1 Modeling capsule interaction with the environment

A capsule can use public ports to interact with its environment. Spin requires that a verification model "must always contain *all* the information that could possibly be required to verify its properties." (Holzmann 2003, p. 68) Therefore, if the top-level capsule in the model has public ports and is expected to interact with its environment, then the environment of the capsule must also be included in the verification model.

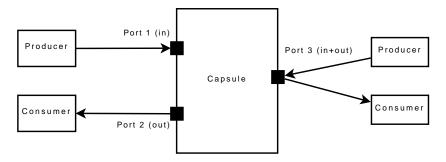

A capsule's only interface for interaction is its ports. The internals of a capsule is hidden from the environment's point of view and, conversely, the capsule's view of its environment is restricted to the reception and transmission of signals. Modeling a capsule's environment from the capsule's point of view can therefore be done by sending signals to the capsule's ports, and by receiving signals sent from the capsule's ports. An illustration is found in Figure 6.2, where components modeling the environment are connected to a capsule with three ports.

Figure 6.2: Illustration of a capsule that has public ports. Producer and consumer components are attached to the capsule in the verification model to model the behavior of the environment and close the verification model.

It is possible that the behavior of the environment is somehow restricted. However, if no restrictions are imposed on the signal sequences that can be sent

<sup>&</sup>lt;sup>3</sup>The customized model loader has been provided by Paul Elder, IBM.

<sup>4</sup>http://www.w3.org/TR/xpath

to the system (by ensuring that the choice of signals is non-deterministic) then any behavior of the environment is in effect modeled, including what would be controlled and intentional signal sequences. One benefit of modeling the environment in this way is that erratic and unexpected behavior of the environment can be precisely that which causes failure in a real system (Holzmann 2003, p. 5).

### 6.2.2 Mapping concepts in UML-RT to Promela

The structure of the Promela code is based to a large extent on the structure of verification models generated using the VIP tool. This section explains the more important points of the mapping between RSARTE models and the verification models. Section 8.4 contains a description of a UML-RT model created in RSARTE. The state machine of the only capsule in the model is found in Figure 8.13(a). The Promela code generated to verify that model is available in its entirety in Appendix A and is referred to for comparison throughout the remainder of this section.

The prototype system does not provide a complete mapping of all available UML-RT constructs. The recognized subset excludes, for example, hierarchical states, payloads carried by signals, and multiplicity values for model elements exceeding one. Moreover, no guard conditions in state machines are recognized, and neither are pseudostates (such as choice points) except the initial state.

#### Capsules

- Each capsule is modeled as a Promela process. The example verification model contains one such process called *DemonstrationCapsule* (line 63).

- Each process uses the run operator to start the processes that correspond to its capsule roles. The *DemonstrationCapsule* does not contain capsule roles, so it runs no other processes (lines 71–76).

- The top-most capsule is started by the init process. The *DemonstrationCapsule* is the top-most capsule and is started at line 257.

- There are no assumptions made on the scheduling of processes or priorities between them.

#### Protocols and signals

While v-Promela and UML-RT distinguish between *in* and *out* signals in a protocol, the VIP tool does not support this distinction (Kamel & Leue 2000, p. 474). The prototype system does, and generates a Promela model in which this *in* and *out* signals are treated separately.

- Protocols are modeled using a user-defined structured data type (using the typedef declarator). The original model in the example contains one protocol called *DemonstrationCommunication* (line 20).

- All protocol signals are modeled with mtype declarations. The *DemonstrationCommunication* protocol has three in signals (lines 24–28).

- The *in* and *out* signals of a protocol are separated into two typedefs.

#### Ports and connectors

- A connector joins two capsules and is modeled with Promela channels; one channel for *in* signals and one channel for *out* signals.

- A capsule communicates over one or more ports that are connected to other capsule ports with a connector. The channels used by a process are passed as arguments to the process when it is started. The name, used in the process to refer to the channel, corresponds to the port name to which the connector is connected (line 64).