UNIVERSITY OF GOTHENBURG

# Integrating Programmable Smart-NICs into Industrial Packet-Processing Systems

Master's thesis in Computer science and engineering

Lina Blomkvist and Tove Svensson

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2021

MASTER'S THESIS 2021

#### Integrating Programmable Smart-NICs into Industrial Packet-Processing Systems

Lina Blomkvist and Tove Svensson

UNIVERSITY OF GOTHENBURG

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2021 Integrating Programmable Smart-NICs into Industrial Packet-Processing Systems

Lina Blomkvist and Tove Svensson

© LINA BLOMKVIST, TOVE SVENSSON, 2021.

Supervisor: Romaric Duvignau, CSE Advisor: Patrik Nyman and Eric Nordström, Ericsson Examiner: Marina Papatriantafilou, CSE

Master's Thesis 2021 Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg SE-412 96 Gothenburg Telephone +46 31 772 1000

Typeset in  $L^{A}T_{E}X$ Gothenburg, Sweden 2021 Integrating Programmable Smart-NICs into Industrial Packet-Processing Systems

Lina Blomkvist and Tove Svensson Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg

#### Abstract

In order to cope with the requirements of 5G, Smart Network Interface Controllers are being used to offload general use CPUs. For them to be able to become more widely used, research of how to integrate them into already existing industrial systems and the cost of such a transition is needed. This thesis presents the method of integrating a P4 programmed Netronome Agilio Smart Network Interface Controller (SNIC) into a high speed industrial packet processing pipeline. A partition of the industrial system handling packet classification is translated and implemented and run on the SNIC and tested and compared to the original program performing the same task. The effect on performance is analysed and a qualitative evaluation of the process conducted. The challenges faced in this project consisted of understanding the industrial system environment and how to seamlessly translate the code without losing the original functionality.

Keywords: 5G, P4, SDN, SNIC.

#### Acknowledgements

Thank you to Romaric Duvignau, Patrik Nyman, and Erik Nordström for making this thesis possible, and to Dhrupal Hareshkumar Tilava, for your incredible support during the project.

Lina Blomkvist Tove Svensson, Gothenburg, November 2021

## Contents

| 1.1       Problem       2         1.2       Goals       2         1.3       Challenges       3         1.4       Method       3         1.5       Limitations       4         1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1                                                                                                                              | Li       | st of | Figur  | es       | xi        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|--------|----------|-----------|

| 1.2       Goals       2         1.3       Challenges       3         1.4       Method       3         1.5       Limitations       4         1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G       Architecture       7         2.1.2       5G       Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20 </th <th>1</th> <th>Intr</th> <th>oduct</th> <th>ion</th> <th>1</th>                                                  | 1        | Intr  | oduct  | ion      | 1         |

| 1.3       Challenges       3         1.4       Method       3         1.5       Limitations       4         1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Variation       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21                                                                                   |          | 1.1   | Proble | em       | 2         |

| 1.4       Method       3         1.5       Limitations       4         1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Vaccases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       13         2.2.3       Smart-NIC Architecture       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol                                                                           |          | 1.2   | Goals  |          | 2         |

| 1.5       Limitations       4         1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The                                                                    |          | 1.3   | Challe | enges    | 3         |

| 1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6 <td></td> <td>1.4</td> <td>Metho</td> <td>d</td> <td>3</td> |          | 1.4   | Metho  | d        | 3         |

| 1.6       Report structure       4         2       Background       7         2.1       Requirements of 5G       7         2.1.1       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                       |          | 1.5   | Limita | ations   | 4         |

| 2.1       Requirements of 5G       7         2.1.1       5G Vise-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       19         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                           |          | 1.6   |        |          | 4         |

| 2.1       Requirements of 5G       7         2.1.1       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                        | <b>2</b> | Bac   | kgrou  | nd       | 7         |

| 2.1.       5G Use-Cases       7         2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                      |          |       | -      |          | 7         |

| 2.1.2       5G Architecture       8         2.2       Smart Network Interface Controllers       11         2.2.1       The NIC       11         2.2.2       The NIC       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       19         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                       |          |       | -      |          | 7         |

| 2.2Smart Network Interface Controllers112.2.1The NIC112.2.2The Need for Smart-NICs112.2.3Smart-NIC Architecture132.2.3.1Netronome Agilio Smart-NIC132.3The Packet Processing Pipeline152.4Introduction to the P4 Language152.4.1Headers162.4.2Parser172.4.3Control Blocks182.4.4Actions192.4.5Match+Action Tables192.4.6Externs202.4.7Compilation202.4.8Limitations of P4202.4.8.1Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 212.5The GPRS Tunneling Protocol222.6Software Tools22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |       | 2.1.2  |          | 8         |

| 2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                   |          | 2.2   | Smart  |          | 11        |

| 2.2.2       The Need for Smart-NICs       11         2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                   |          |       |        |          | 11        |

| 2.2.3       Smart-NIC Architecture       13         2.2.3.1       Netronome Agilio Smart-NIC       13         2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       16         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                        |          |       | 2.2.2  |          | 11        |

| 2.2.3.1Netronome Agilio Smart-NIC132.3The Packet Processing Pipeline152.4Introduction to the P4 Language152.4.1Headers162.4.2Parser172.4.3Control Blocks182.4.4Actions182.4.5Match+Action Tables192.4.6Externs202.4.7Compilation202.4.8Limitations of P4202.4.8.1Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 212.5The GPRS Tunneling Protocol222.6Software Tools22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |       | 2.2.3  |          | 13        |

| 2.3       The Packet Processing Pipeline       15         2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |       | -      |          | 13        |

| 2.4       Introduction to the P4 Language       15         2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 2.3   | The P  |          | 15        |

| 2.4.1       Headers       16         2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |       |        | ÷ -      | $15^{-5}$ |

| 2.4.2       Parser       17         2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |        |          | 16        |

| 2.4.3       Control Blocks       18         2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       |        |          | 17        |

| 2.4.4       Actions       18         2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |        |          | 18        |

| 2.4.5       Match+Action Tables       19         2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 20         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |       | -      |          | 18        |

| 2.4.6       Externs       20         2.4.7       Compilation       20         2.4.8       Limitations of P4       20         2.4.8.1       Differences Between P4 <sub>14</sub> and P4 <sub>16</sub> 21         2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |       | 2.4.5  |          | 19        |

| 2.4.7Compilation202.4.8Limitations of P4202.4.8.1Differences Between P414 and P416212.5The GPRS Tunneling Protocol222.6Software Tools22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |       | 2.4.6  |          |           |

| 2.4.8Limitations of P4202.4.8.1Differences Between P414 and P416212.5The GPRS Tunneling Protocol222.6Software Tools22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |       | 2.4.7  |          | 20        |

| 2.4.8.1Differences Between $P4_{14}$ and $P4_{16}$ 212.5The GPRS Tunneling Protocol222.6Software Tools22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |       |        | 1        | 20        |

| 2.5       The GPRS Tunneling Protocol       22         2.6       Software Tools       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |       | -      |          |           |

| 2.6 Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 2.5   | The G  | 14 10    | 22        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | -     |        | <u> </u> | 22        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       |        |          |           |

| $2.6.2$ Mininet $\ldots$ $23$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |       |        | 10       |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       | -      |          | -         |

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |       |        | ° ·      |           |

|          |                            | 2.6.5 DPDK and pktgen                                     | 24 |  |  |

|----------|----------------------------|-----------------------------------------------------------|----|--|--|

|          | 2.7                        | Related Work                                              | 24 |  |  |

|          |                            | 2.7.1 Offloading 5G Functions to a Programmable ASIC      | 24 |  |  |

|          |                            | 2.7.2 Using Smart-NICs to Decrease Host Processor Usage   | 25 |  |  |

|          |                            | 2.7.3 P4-enabled Smart-NIC Offloading                     | 25 |  |  |

| 3        | Imr                        | plementation Methodology                                  | 27 |  |  |

| 0        | 3.1                        | Environment Setup                                         |    |  |  |

|          | 3.2                        | Initial P4 Test Program                                   |    |  |  |

|          | 3.3                        | Translation of industry code to P4                        |    |  |  |

|          |                            | 3.3.1 Brief Overview of The Original Program              |    |  |  |

|          |                            | 3.3.2 Required Changes for Translating C Code to P4       | 29 |  |  |

|          |                            | 3.3.3 Difficulties in Using Netronome's Programmer Studio | 30 |  |  |

|          |                            | 3.3.4 Dynamic Table Updates                               | 30 |  |  |

|          | 3.4                        | Creating the C-Program for Testing                        | 31 |  |  |

|          |                            | 3.4.1 Adapting the Code for Standalone Tests              | 31 |  |  |

|          |                            | 3.4.2 Adapting the Original System                        | 31 |  |  |

|          | 3.5                        | Necessary Downgrades of the Program                       | 32 |  |  |

| 4        | $\mathbf{F}_{\mathbf{V}0}$ | luation Methodology                                       | 33 |  |  |

| 4        | <b>E</b> va<br>4.1         | Performance Evaluation                                    |    |  |  |

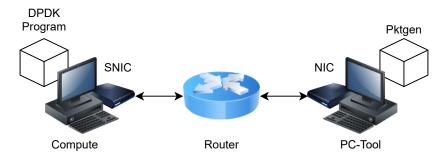

|          | 4.1                        | Test Environment                                          |    |  |  |

|          | 4.3                        | Performance Evaluation                                    | 34 |  |  |

|          | 4.0                        | 4.3.1 Measurement Program Implementation                  |    |  |  |

|          |                            | 4.3.2 Testing Method                                      |    |  |  |

|          |                            | 4.3.3 Possibility of Fully Integrated Testing             | 36 |  |  |

|          | 4.4                        | Qualitative Evaluation Criteria                           | 38 |  |  |

| <b>5</b> | Bos                        | ults                                                      | 39 |  |  |

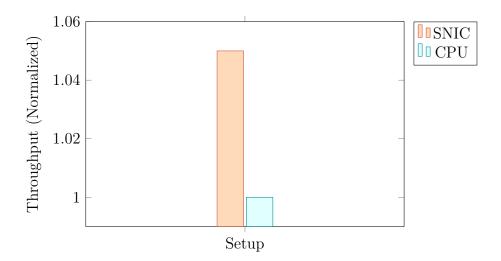

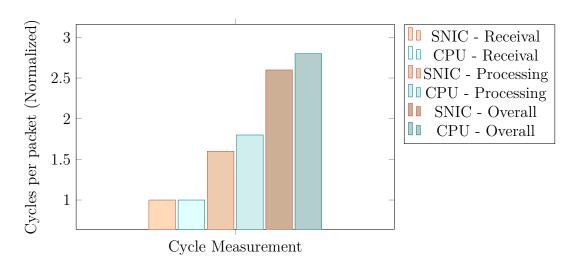

| J        | 5.1                        | Performance Evaluation                                    |    |  |  |

|          | 5.1                        | Qualitative Evaluation                                    |    |  |  |

|          | 0.2                        | 5.2.1 Ease of Environment Setup                           |    |  |  |

|          |                            | 5.2.2 Documentation Availability                          |    |  |  |

|          |                            | 5.2.3 Programming Experience                              | 42 |  |  |

|          |                            | 5.2.4 Hardware Limitations                                | 42 |  |  |

|          |                            | 5.2.5 Netronome                                           | 43 |  |  |

| 0        | C                          |                                                           |    |  |  |

| 6        |                            | ncluding Remarks                                          | 45 |  |  |

|          | 6.1                        | Discussion                                                | 45 |  |  |

|          |                            | 6.1.1 Performance Evaluation                              | 45 |  |  |

|          | 60                         | 6.1.2 Qualitative Evaluation                              | 45 |  |  |

|          | 6.2                        | Future Work   Conclusion                                  | 46 |  |  |

|          | 6.3                        | Conclusion                                                | 46 |  |  |

| Bi       | Bibliography 49            |                                                           |    |  |  |

## List of Figures

| 2.1 | The layers of the 5G infrastructure                                                                                | 8  |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | More detailed view over the different layers [14]                                                                  | 9  |

| 2.3 | Explanation of the micro-service architecture compared to the mono-                                                |    |

|     | lithic approach $[15]$                                                                                             | 10 |

| 2.4 | NFP-4000 Flow Processor Block Diagram [32]                                                                         | 13 |

| 2.5 | Agilio SNIC Sample Design [32]                                                                                     | 14 |

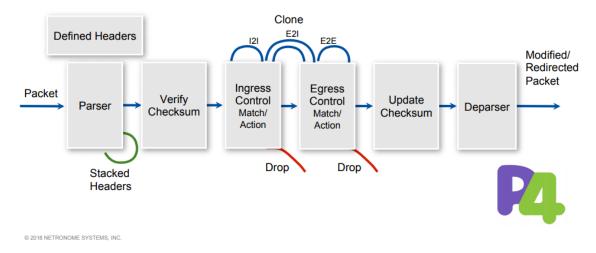

| 2.6 | The P4 abstract switch model [38]                                                                                  | 15 |

| 2.7 | The P4 to Netronome Agilio NFP-4000 compilation                                                                    | 21 |

| 2.8 | The GTPv2 Header.                                                                                                  | 22 |

| 3.1 | The v1model [50]                                                                                                   | 28 |

| 4.1 | Performance evaluation setup, the cubes representing the hypervisors.                                              | 33 |

| 5.1 | Difference in throughput between the SNIC implementation and the original system when handling GTPU packet stream. | 40 |

| 5.2 | Difference in cycles between the SNIC implementation and the CPU                                                   |    |

|     | system when handling GTPU packet stream                                                                            | 40 |

## 1

### Introduction

With the growing network transmission speeds of 5G, packet handling using generaluse CPUs is a bottle-neck in regard to speed. To improve the performance in packet handling, Network Interface Controllers (NIC) are used to handle full or partial packet offload from the CPUs in data centers. Furthermore, to be able to adapt to clients' changing demands on features, programmable NICs, called Smart-NICs (SNIC), are increasingly being used.

The SNICs are able to be programmed using various programming languages, an example of such is P4 [1], which is utilized by many large companies including Cisco, Intel, and Google [2]. P4 is a domain specific language for network programming and was developed to improve the flexibility and reconfigurability of networks. These capabilities, in combination with the programmable SNIC, are crucial to be able to apply Software Defined Networking (SDN) which includes a control plane allowing change of network functionality without physical interference. The possibility to use SDNs is key to being able to adapt to new technology and integrate new functionalities efficiently, which is why it is necessary to research the feasibility of replacing existing NICs in exiting data centers, with SNICs.

Though the possible performance gains of using SNICs have been known for a couple of years, little research on the integration process have been conducted. Research is required to investigate the method of integration, limitations to the type of and amount of logic that can be transferred the Smart-NIC, as well as the impact the integration has on performance. During this project, a part of an C-programmed 5G industrial packet processing pipeline was translated to P4 to then be offloaded to a P4-programmed SNIC. The performance the system gained by using the SNIC was then evaluated against the challenges the translation process brought to arrive at a final evaluation. The project strived to further the understanding of the SNIC integration process and the possibilities and limitations that it entails.

#### 1.1 Problem

In order for the use of P4-programmed SNICs to increase, it has to be evident that the performance gain in using SNICs is greater than the cost of transitioning to using them. This stresses the need to investigate the challenges in the process of offloading an industrial pipeline to a SNIC using P4. For a system operating mainly on CPUs or regular NICs to transition to P4-programmed SNICs, limiting factors of the language in terms of functionality must be identified in order to conclude which parts of the pipeline can and cannot be translated. Furthermore, it is necessary to evaluate the performance of the offloaded functions in a real system to ensure that the research suggesting that the use of SNICs with P4 will improve the performance of a system, holds up in practice.

With this in mind, the problem statement of the project has been phrased as the following research questions:

- 1. Do the performance gains justify the costs when integrating a SNIC to offload the CPU/ASICs of packet processing in an industrial cloud native data plane?

- 2. What are the limiting factors when using P4 programmed SNICs as opposed to CPU/ASICs?

- 3. Does the limited scope experiments performed in testing environments resulting in higher performance hold up in real scenarios?

A summary of current research within the area of using Smart-NICs can be found in Section 2.7.

#### 1.2 Goals

In order to answer the research questions stated in the previous section, three goals for the project have been outlined. Presented below, these goals involve translating a part of an industrial packet processing pipeline to P4 and running it on a SNIC. To ensure that the functionality is intact and measure the performance of the resulting system rigorous testing must be performed. The evaluation of the project should account for the performance of the system, and there should be a qualitative evaluation of the difficulty of the process and limitations of the technology.

The goals of the project have been summarised as follows:

- 1. Identify a part of the cutting edge industrial packet processing pipeline suitable for offloading to a SNIC and translate the logic of this section into a P4 program.

- 2. Offload part of the initial production level pipeline to a SNIC while preserving the functionality of the system.

- 3. Evaluate the performance of the resulting system with consideration to the

limits and difficulties of the process.

#### 1.3 Challenges

For the choice of which part of the system logic would be used for translation into a P4 program to control the SNIC, the guidance of industrial experts is required. The specific functionality of this part to be converted is also pinpointed by experts. However, in order to understand how the chosen logic communicated with its environment and how to mimic this in the translation, further investigation has to take place. Since the system is large and complicated, the main challenge in this is to understand the environment within which the chosen logic is deployed.

After the logic had been translated, the next challenge consisted of integrating the use of the SNIC with the P4 code into the industrial system. This challenge included preserving the dynamicity of the previous code and finding a way to communicate between the SNIC and the original C code at an acceptable speed.

#### 1.4 Method

One of the main goals of this project regards evaluating the process of the implementation of a P4 program and integration of a SNIC into a large pipeline. In order to perform the evaluation in an ordered manner, the methodology of the project requires careful consideration. Each step of the process can be isolated to ensure it is clear at what stage any issue arises and what challenges are associated with each part of the process. The details of the development is further explained in Section 3 and 4, but the following list gives an overview of the projects methodology.

- 1. A development environment was set up where a P4 programmed switch and a few end hosts were simulated using a network simulation software. This environment was used to test the functionality of the program during the implementation, before testing on real hardware.

- 2. Before translation of the industry code, an initial P4 program was created. The program did not include any specific functionality, but was rather just a shell to make sure parsing and deparsing of packets worked correctly and the development environment was operating as intended.

- 3. A suitable part of the industry pipeline was then selected for translation, and the initial P4 program was extended to accommodate this. A custom output header was introduced to deliver the results of the computations, and the functionality of the industry code translated to P4.

- 4. The SNIC was then loaded with the code and put in a testing environment to simulate the actual system. From which the performance was measured and compared to that of the initial system's.

- 5. After this, a qualitative evaluation was performed, discussing the difficulty of

the integration process.

6. The final result was then concluded by weighing the results of the qualitative evaluation and the performance evaluation against each-other.

#### 1.5 Limitations

There are several limitations in measuring the impact Smart-NIC usage may have on performance in an industrial system. For example, due to lack of time and resources, the research of this project is based on tests performed in one particular system only. Therefore, it is not known if the performance of systems structured differently will be affected by Smart-NIC usage in the same manner. Naturally, the difficulty of Smart-NIC integration in other systems is also unknown.

Another limitation to the performance impact measurements is that the project is limited to using one particular Smart-NIC hardware, again due to time and resource limitations. Hence, it could be that other Smart-NIC devices could affect performance differently.

The evaluation is also limited in scope, in that the main points of interest chosen are performance and ease of implementation. As such, other aspects such as the cost of the respective hardware or the difference in energy consumption of the devices has not been considered.

Further, the project is limited to handling only one part of a larger pipeline. The pipeline handles packet processing in a large scale industrial 5G network, and the part that is examined in this project performs simple classification of incoming packets. The reason for choosing only this part of the pipeline is primarily due to time constraints but also due to limitations of the use of P4 in the Smart-NIC. While P4 offers great flexibility, it is not possible to inspect the application layer of a packet in a P4 program, making in unable to perform operations that rely on this, for this reason, some parts of the industrial pipeline considered in this project are not possible to offload to a P4 programmed SNIC. There is hence a possibility that other programming languages could have other possibilities and thus effects on performance. However, due to time constraints, the choice was made not to investigate any additional languages.

#### 1.6 Report structure

The thesis begins by describing the needed background in Chapter 2. This chapter starts with Section 2.1 which describes the requirements on 5G and its architecture. Thereafter, Section 2.2 explains the workings of NIC to then introduce Smart-NIC by first motivating the need for them followed by an architectural description and an illustration of a packet's path through a SNIC. Section 2.4 then describes the use of the P4 language and its functionality. The background continues by Section 2.6 where additional software used in the project is briefly introduced. The final section

discusses related works to illustrate the current state of research in SNIC and P4 usage.

Chapter 3 regards the implementation of the project, including the setup of the environment, translation of the C code to P4 and, the integration of the program into the industrial pipeline. Following in Chapter 4 the evaluation of the project is depicted. The testing environment is presented along with the testing criteria and methodology, followed by a description of the qualitative evaluation criteria.

In Chapter 5 the results of the tests done are described in detail along with the assessment of the qualitative evaluation criteria. Finally, Chapter 6 contains the conclusions drawn by the authors as well as a discussion of the results.

#### 1. Introduction

## 2

### Background

The fifth generation cellular networks (5G) have to satisfy the needs of the coming years. The amount of traffic will not only significantly increase, but also introduce new demands as the nature of the connected devices change and the IoT grows [3]. In order to support the growth in uses such as cloud based technology, virtual streaming (vstreaming), and online gaming as well as the significant increase of Internet of Things (IoT) devices, demands on the networks are very high. The 5G networks need to satisfy low latency as well as a huge increase in bandwidth from 4G, while still pursuing to further decrease in energy consumption [4]. In order to meet the new requirements, the underlying architecture of the network needs to be both efficient and flexible. It is demonstrated in simulations that Smart-NICs could offer a possible solution to this problem [5, 6, 7, 8, 9, 10]. P4 is a new and increasingly popular language for programming these Smart-NICs.

This chapter gives an introduction to 5G networks followed by an explanation of what a SNIC is and how it works. Thereafter, the P4 language and other software tools used in the project are presented. Finally, there is a summary of relevant related work.

#### 2.1 Requirements of 5G

This Section begins by giving a closer introduction to the requirements of 5G, briefly explaining the main solution concepts. The following sections goes deeper into how the architecture of 5G vows to fulfill the requirements.

#### 2.1.1 5G Use-Cases

The 5G network is designed with vertical industries (markets catering to specific industries) in mind. These industries, including industrial automation, mission critical IoT, and medical care, come with new network use cases which put a new kind of pressure on the network architecture [11].

The different services of each industry demand appropriate data- and network resource allocation. Mission critical IoT for example, may contain services needing certain resources guaranteed at all time to be able to pull of critical tasks without being interrupted by network traffic. The solution to this is for the 5G architecture

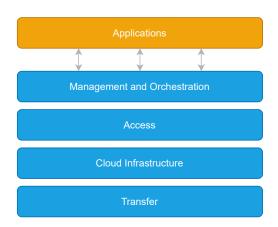

Figure 2.1: The layers of the 5G infrastructure.

to provide separate logical networks per industry. The separate logical networks are called network slices and each separate network slice contains functions specialized in the field it is managing. In order to handle the complex allocation management of resources slices incur, telecommunication operators deploy special orchestration functions. Further, if an operator lacks in a resources, or certain services, there is a need for the possibility of cross-domain orchestration, which also pushes the limits of the 5G architecture [12].

One of the main concepts of 5G is to facilitate deployment, management, and creation of new services. To be able to provide for this a Service-Based Architecture (SBA) is used, providing applications as a set of micro-services. For optimal performance, these micro-services should be further deployed in a so cloud-native 5G core network, where cloud services are used to the utmost ability to decouple networks and network functionality from hardware. For example, router functions could be moved from hardware to a remote virtual machine making it easier to deploy and remove [13].

In order to accommodate for a cloud networking environment, the 5G architecture further needs to integrate a way to manage hardware functionality in software, and an infrastructure where functionality within the hardware may be transferred to the cloud. Together, these infrastructures make cloud-native networks possible. These methods also promote creation of automation software to minimize manual handling of the 5G network [12, 11].

#### 2.1.2 5G Architecture

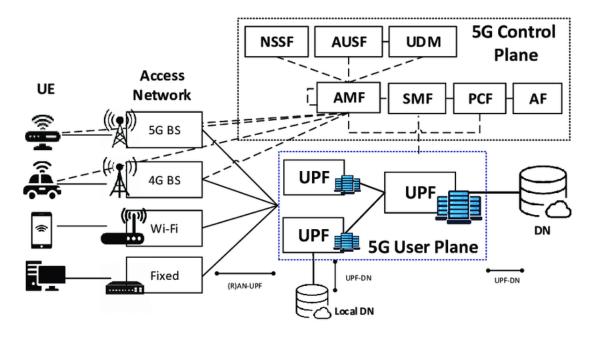

The general structure of the 5G Architecture is defined as shown in Figure 2.1 where the horizontal boxes represent the different infrastructure layers. A more detailed view of how the different layers are connected can be seen in Figure 2.2, where the user plane, which is the part this project concerns, is encompassed by a blue line.

The top layer is the application layer. This layer contains the applications using the network for their services. An application in the 5G network is defined as a software that uses underlying micro-services for it is provided functionality. This approach,

Figure 2.2: More detailed view over the different layers [14].

shown in Figure 2.3, steps away from the previous monolithic approach where each application is constructed as a single unit. The benefits of the modular approach includes the ability to scale only the micro-services in demand when scaling the application and the simplicity in only having to rebuild and deploy a new micro-service instead of the whole unit when making small changes to the code. The micro-service architecture also makes it easier to distribute and maintain services without needing large amounts of processing power and memory [15, 12, 16].

The challenge of using a micro-service architecture is the large amount of orchestration needed to maintain it. This is where the management and orchestration layer comes into play. A part of this layer manages network functions and interfaces, to for example micro-services, by available physical and virtual resource. Another part of the management and orchestration layer concerns maintaining the software defined control plane needed for SDNs. This control plane moves away control from hardware by making it possible to manage devices beyond physical connectivity via control software. By providing open API through software, the SDN control plane enables central programming of network behavior which in turn provides increased simplicity in management for operators. Using SDN also provides network automation which orchestrates the direction of network traffic depending on certain conditions [15, 12, 16].

With SDNs, NFV becomes more compelling. NFV focuses on the decoupling of network functions and hardware devices by using virtual machines on standardized (non-specialized) hardware. This eliminates need for specialized hardware and creates the possibility of using one machine for multiple network functions. Another benefit of NFV is to be able to move network functions around as demand changes, increasing flexibility. For example, if a new network function is needed, a new virtual

A monolithic application puts all its functionality into a single process...

... and scales by replicating the monolith on multiple servers

A microservices architecture puts each element of functionality into a separate service...

... and scales by distributing these services across servers, replicating as needed.

Figure 2.3: Explanation of the micro-service architecture compared to the monolithic approach [15].

machine is simply set up and when it is not needed the Virtual Machine (VM) is removed. The NFV resource and network demands are also orchestrated by the second layer and together with the SDN approach a network decoupled from hardware from functions to control is created [17, 18, 19].

Another concept of the 5G architecture is to enable network community innovation, making it possible for anyone to use the networks capabilities to evolve network functionality. In order to do this, the second layer also includes control functions for network exposure, meaning to present an API for programmer to use the provided services [16, 20].

The access layer contains the access and communication services and the packet core. The access services established access to the edge nodes of the network and distributes data plane functions to the edges of common core networks. The communication services manage how services communicate over different service providers as well as to a client over a single provider. It further defines how IP Multimedia Services (IMS) are distributed in the new cloud environment as well as how inter-networking with 3G and 4G is executed [16, 21].

The third layer contains the packet core. The packet core separates different data channels between an IP and user equipment (UE) in order to set parameters regarding performance. Thereafter, the PDN (Packet Data Network) Gateway is set as an IP anchor point for IP-communication between the UE and external PDNs (the Internet). The PDN Gateway also provides packet filtering and policy enforcement such as Quality of Service (QoS). The Serving Gateway (SGW) is the mobility anchor that makes sure packets are routed properly to then be delivered between the UE and PDN even though the UEs position changes. Finally, the User Plane (UP) includes mobile anchor functionality, external PDU session connection points, and packet routing and forwarding. This is where the packet traffic is carried over the data-link layer using Ethernet-frames with MAC-addresses, which is where Network Interface Controllers (NICs) are used [22, 23, 24, 16].

The cloud infrastructure layer contains all cloud functionality and resources including such for security. These are all the tools needed to build the cloud. Finally, the transfer layer contains the hardware for the network communication [16, 12].

#### 2.2 Smart Network Interface Controllers

This Section vows to give a conviction to the need for Smart-NICs in the 5G industry. Following is an explanation to how a Smart-NIC works in more detail.

#### 2.2.1 The NIC

A NIC is a hardware component used to connect a computer to a network. It acts as a packet transceiver and has as a main function to convert packets between digital signals and data form. The NIC provides devices with MAC addresses and strips or appends the packets' data layer frames upon arrival and dispatch respectively [25].

General NICs contain multiple smaller parallel cores in order to handle multiple transmit/receive queues in parallel as well as increase packet processing speed [6]. Older NICs may further use the host's general use CPU for running network stacks. However, the use of host CPUs for running networks stacks in the time of cloud computing has been proven to decrease available processing power from VMs and increases latency to the network performance [26]. Therefore, modern NICs contain extended hardware in order to offload the CPU on top of optimization hardware to increase network packet processing speeds [9]. For example, NICs may have offload engines (such as the TCP offload engine [27]) to relieve the TCP/IP packet processing stack from the CPU and include interrupt and Direct Memory Access (DMA) interfaces to the host processor to avoid accesses needing to pass through the CPU [9, 28].

Low speed (<10Gbps) packet processing is still possible using simply Operating System (OS) drivers paired with high-end CPUs. However, the mentioned extended techniques are crucial to reach speeds of 100G without overloading the CPU [9].

#### 2.2.2 The Need for Smart-NICs

While the regular NICs provide several performance increasing features, problems arrive when NICs are used in the continuously evolving networks of today. Firstly, the networks' applications demand increasing amounts of features including support for new protocols, evolving intrusion detection, and dynamic load balancing, on top of the already existing ones. Secondly, the rapid development of 5G has created the

possibility for new network use cases such as cloud computing, machine learning, and big data applications. As a result of this there is a need for new ways to architect communication networks.

The requirements of flexibility, dynamicity, performance, and efficiency demand carefully engineered NICs, which not only require a lot of time and money to develop, but also large deployments of dedicated hardware to run. Due to these issues, vendors tend to only add features which have been in demand for a longer time, which slows down development at the same time as the further addition of features slows the NICs down [29].

To mitigate the gap between the increased network bandwidth and the stagnating computing power of the CPUs as well as mend the flexibility issue of the NIC, SNICs have been developed [8]. Smart-NICs are network interface cards that provide programmability in the data path [6] by extending the foundational NIC with a programmable engine such as a Field Programmable Gate Arrays (FPGA), Application-Specific Integrated Circuits (ASIC), or an embedded CPU. This engine makes it possible for new features to be introduced to the already existing SNIC by using the programmable hardware functions [30].

Due to its programmability, the introduction of SNIC makes it possible to use SDN programmable data and control planes. By using these SDN planes, the features of the packet processing and routing can be defined in software and then optimized in hardware [9]. The programmability also makes the SNIC able to accelerate a larger variety of workloads compared to the previous ones [31].

The use of programmable SNIC, to offload logic for packet processing has already been researched and proven to improve processing speed even while using only partial offload [5, 6]. The research of the possibilities of offloading network stack functionality onto the SNICs has lead to development of multiple different system models designed for ease of use and performance in different environments [7]. For example, there are frameworks specialised in offloading distributed applications [8] and for running Azure network stacks [26].

Though the programming models of the Smart-NICs still are in development, there are languages, such as P4, that are designed with the features of Smart-NICs considered [6].

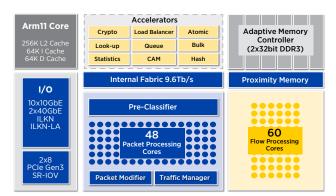

Figure 2.4: NFP-4000 Flow Processor Block Diagram [32].

#### 2.2.3 Smart-NIC Architecture

To be able to add support for new functions to be added after purchase, the Smart-NIC needs additional computational power and onboard memory which is not provided to a regular NIC. These needs can be provided by different architectures, but most are constructed with a control processor at the core [33]. This core is used to initialize and configure the SNIC, hold all additional features, as well as other control plane management features such as packet steering. By using this additional core, the host CPU's use of cycles is offloaded [34].

The additional computational power is usually provided by adding clusters of ASICs, Flow Processing Cores (FPCs), or by using an FPGA. Where ASICs are circuits specialized for a certain purpose, FPCs are customizable cores designed for optimizing packet flow processing, and FPGAs contain low level reconfigurable circuits. FPCs provide the cheapest, most flexible solution in comparison to the other two and is hence the most popular architectural approach [35, 33].

#### 2.2.3.1 Netronome Agilio Smart-NIC

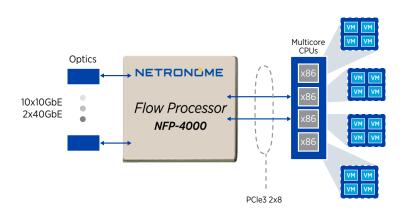

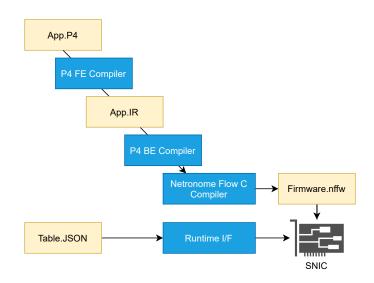

In this project, a Netronome Agilio SmartNIC with a Netronome Flow Processor (NFP) 4000 as control processor will be used. These NFPs use the FPC approach, supporting multiple threads each with access to dedicated instruction and data memories [36]. The Agilio NFP-4000 has possiblity to support up to 60 FPCs with each FPC able to use 8 threads each. This makes it possible for the SNIC to process 480 packets in parallel. A closer look into the NFP can be seen in Figure 2.4, where the output PCIe-Gen3 interfaces as well as different accelerators are visible. A sample design of a SmartNIC can further be viewed in Figure 2.5 where it is connected to a host through the PCIe-Gen3 interfaces. This section will now continue to explain a packet's path through the Agilio NFP-4000 SNIC.

When a packet is received at the SNIC ingress port, it firstly goes through an integrity check. Thereafter, it is stored in a buffer and delivered to the ingress processing stage. In the processing stage, Packet Processing Cores (PPCs) are used to parse the packet, generate its metadata, and finally the packet is sent to the DMA engine. The DMA engine then sends the packet headers to the FPCs and the

Figure 2.5: Agilio SNIC Sample Design [32].

payload to a buffer. All of this is done under complete software control. The FPCs do the flow processing, including generating keys for table matching, table lookups, and forward, Drop, and Add/Remove header actions. Finally, the PCI repackages the packet with headers and payload, and sends it to the host. When the packet is delivered from the host to the egress port instead, the PCI first delivers the packet to the FPCs where packet processing is performed. Thereafter, the packet is sent to the Egress PPCs where it is put in a traffic queue, to finally get its checksum computed and be delivered to a network interface the Egress MAC.

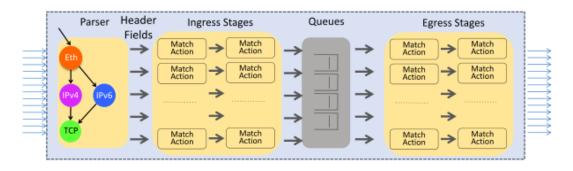

Figure 2.6: The P4 abstract switch model [38].

#### 2.3 The Packet Processing Pipeline